基于FPGA的高效灵活性数字正交下变频器设计

徐 伟,王旭东

(南京航空航天大学 电子信息工程学院,江苏 南京 210016)

在软件无线电中,数字下变频DDC作为一个桥梁连接着前端A/D转换器和后端的DSP器件。通过变频、抽取滤波,将低速数据送给DSP器件进行处理[1-4]。随着半导体技术的发展,FPGA的性能越来越高,而成本越来越低,并且内置越来越多的成熟IP核,这些都为其研究和开发提供了方便。利用FPGA实现DDC功能成为软件无线电设计中的常用手段。

1 数字下变频的基本原理

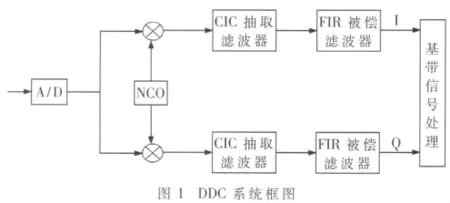

在软件无线电中,一般都采用正交数字下变频法,如图1所示,正交数字下变频法主要由数字混频器、数字振荡器NCO和抽取滤波器三个部分组成。其中核心部件是抽取滤波器和数字振荡器NCO。抽取滤波器采用具有抗混叠效应的CIC滤波和作为补偿滤波器的FIR来实现,NCO模块采用Altera的NCO核来实现[5]。

2 抽取滤波器的设计

2.1 积分梳妆滤波器(CIC)

CIC数字滤波器是窄带低通滤波器的高计算效率的实现形式,常常被嵌入到现代通信系统的抽取和插值模块的硬件实现中。

所谓梳妆滤波器,是指该滤波器的冲击响应具有如下形式:

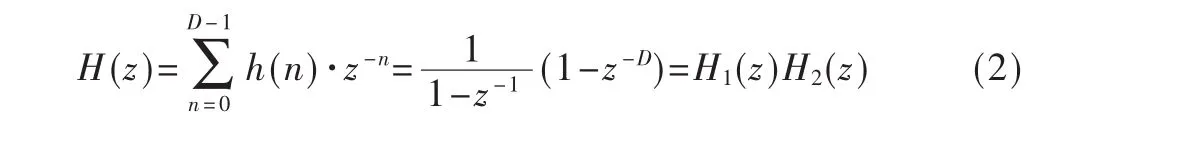

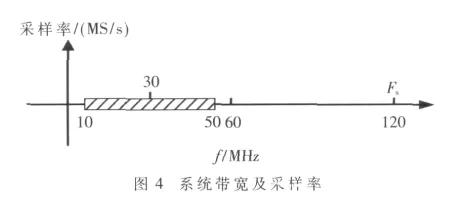

式中,D即为CIC滤波器的阶数(D其实也是抽取因子)。CIC滤波器的z变换为:

由于单级CIC滤波器的旁瓣电平比较大,阻带衰减很差,难以满足实用要求。为了降低旁瓣电平,采用多级CIC滤波器级联的方法来解决,滤波器级数N越大,CIC幅频相应越好。图2采用的是8级抽取结构的CIC滤波器。

2.2 FIR补偿滤波器

虽然梳状滤波器在高速采样的情况下很有效,但是其相应缺少平旦的通带和快速下降的过渡带。为了解决这个问题,一般在抽取CIC滤波器后面级联一个补偿FIR滤波器。积分梳妆滤波器CIC经过补偿滤波器CFIR的补偿后,其幅频响应具有近乎水平的通带和快速下降的过渡带。

积分梳妆滤波器CIC、补偿滤波器CFIR以及二者级联后的信号如图3所示。从图中可以看出,CIC与CFIR级联后的幅频响应曲线通带平坦、过渡带陡峭,满足设计要求。

3 系统硬件实现及结果仿真

下面以一个实际工程应用系统来说明当系统带宽的中心频率落在Fs/4位置时,可对上述结构进行简化。

3.1 系统结构进一步简化

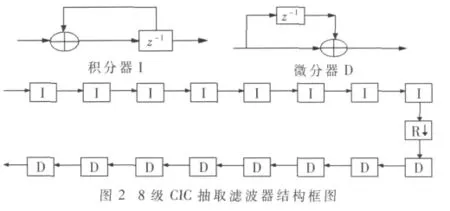

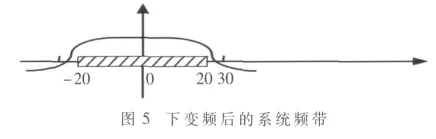

假设A/D采样率为120 MS/s、系统带宽为 40 Mb/s、中心频率选为30 MHz,为防止滤波器过度带对信号的影响,在用户频带的两端留有10 MHz的保护,如图4所示。

对图中的接收信号下变频至零中频,则图4中的NCO设置应为30 MHz(Fs/4)。为防止频率混叠,需对下变频后的信号进行低通滤波,如图5所示。

由于 NCO采用的是 Fs/4,因此其输出 I路为:1,0,-1,0…,Q 路为:0,-1,0,1…。 可见,并不需要乘法运算和NCO IP核,只需要改变两路输入数据的符号即可。

考虑对滤波后的数据要进行2抽1,为进一步减少运算冗余,根据多速率数字信号处理理论,可将抽取运算放在滤波之前,同时NCO的输出也要做相应变化,且这时的LPF变成了奇偶分离的多相结构。经过上述一系列变换后的正交变换模型如图6所示。

3.2 FPGA设计

对上述算法模型进行FPGA设计,采用Altera公司的STRATIXII系列FPGA作为器件平台,并在其STRATIXII DSP开发板上进行硬件验证。

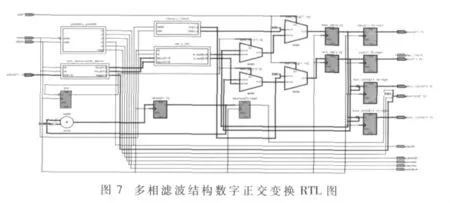

A/D采样率为120 MS/s,系统输入时钟频率为120 MHz,低通滤波器(LPF)的阶数为 64阶,分解到奇偶两路各32阶。在QUARTUSII软件中应用Verilog进行开发,系统经综合编译后的RTL图如图7所示。

表1为系统的资源消耗情况,可以看出该系统消耗的逻辑资源、存储器资源以及DSP模块资源非常少,满足绝大多数雷达、电子侦察、通信系统的要求。

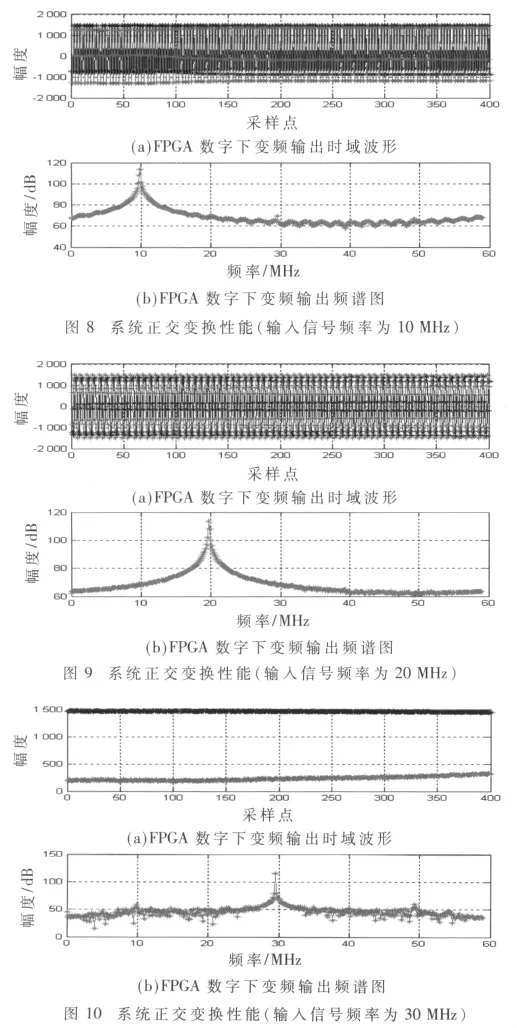

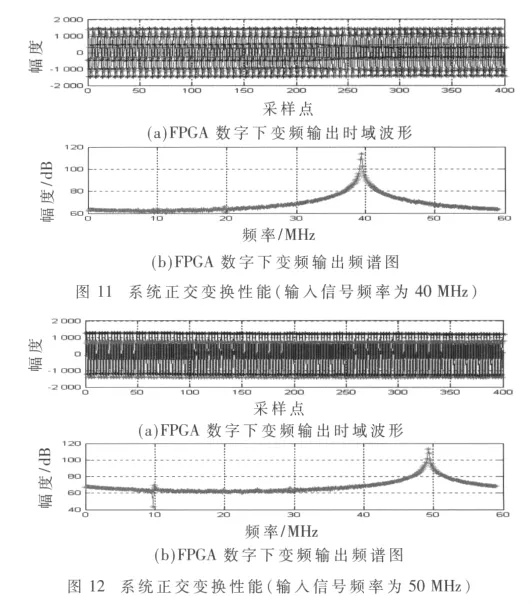

将关心的信号添加到Altera提供的SignalTap II Logic Analyzer中。利用板子上的ADC输入不同频率的信号,使用STP进行采集并将采集到的波形数据保存为CSV文件,然后利用Matlab将其中I/Q两路输出信号读出,作图分析其正交性。为验证该系统在整个频带内的性能平稳度,每隔10 MHz设置一个频点,进行详细验证,如图8~图12所示。

表1 改进的数字下变频系统资源消耗

硬件验证结果表明,在整个10 MHz~40 MHz设计带宽内有效地实现了对中频信号的下变频处理,并且信号具有很好的正交性。该正交变换系统的镜频抑制能力可达60 dB,能够满足绝大多雷达、电子侦察、通信系统的设计要求。

[1]杨小牛,楼才义,徐建庭.软件无线电技术与应用[M].北京:电子工业出版社,2010.

[2]杨勋.软件无线电中上下变频技术的设计和实现[D].西安:西安电子科技大学,2007.

[3]SIMONE L,COMPARINI M C,MARCHETTI F,et al.Spacecraft transponder for deep space applications:design and performance[C].IEEE Areospace Conference Proceeding,2002:1337-1347.

[4]COLEMAN J O,ALTER J J,SCHOLNIK D.FPGA Architecture for gigahertz-sampling wideband if-to-baseband conversion[C].2000 International Conference on Signal Processing Applications and Technology,2000.

[5]Altera Corporation.NCO megacore function user guide[Z].2009.