基于ADSP-21369的浮点DSP实验教学系统设计

韩 赛,杜普选

(北京交通大学电子信息工程学院,北京100044)

数字信号处理(DSP)技术广泛应用于通信、语音、图像、生物医学、工业控制、仪器仪表等各个领域。面对社会和市场的广泛需求,高校必须开设以新型DSP芯片为核心的教学及实验课程,使学生能够掌握最新科学技术。

SHARC系列DSP产品具有运行速度快、片内资源丰富、接口齐全的特点,特别适用于高校实验教学系统的开发,但在国内尚无高校开设基于该系列DSP产品的实验教学课程。

因此,本文对SHARC系列DSP进行深入研究,并设计出一套基于ADSP-21369的浮点DSP实验教学系统。

1 方案设计

该系统以SHARC系列中ADSP-21369为核心处理器,辅以其它模拟器件,主要实现以下功能:

(1)可实现教学中所有实验,如FIR/IIR数字滤波器的设计,FFT/IFFT/ZFFT的实现。

(2)考虑外部接口的通用性,可完成对SDRAM,FLASH,ADC和DDS的控制。

(3)利用ADSP-21369的固有特性,通过数字应用接口DAI(Digital Applications Interface)完成对音频、S/PDIF、 LED灯等的控制。

(4)通过ADSP-21369自带的数字外设接口DPI(Digital Peripheral Interface)完成对LCD,UART,键盘的控制,如实现LCD液晶屏的人机交互等。

整体系统设计框图如图1。

2 系统硬件设计

2.1 DSP处理器的选择

图1 系统设计框图

本系统选择SHARC ADSP-21369做为DSP处理器,其主要优势在于:(1)内核:时钟频率高达400 MHz,指令周期2.5ns,运算能力2 400 MFLOPS,采用单指令多数据运算方式,支持32 bit定点和32-/40 bit浮点运算。(2)片上存储器容量大,SRAM为2 Mbit,ROM为6 Mbit。(3)片上接口丰富: 数字外设接口包括2个SPI,2个UART,3个定时器,1个两线I2C;数字应用接口包括8个串行端口SPORT, S/PDIF Tx/Rx, 8通道异步采样率转换器 ASRC,4个精密时钟发生器;16个PWM;1个TWI;32 bit SDRAM接口。

2.2 外部存储器接口模块设计

该模块由同步存储器接口和异步存储器接口构成,根据ADSP-21369硬件设计手册,除SDRAM应用同步存储器接口设计外,其它均采用异步存储器接口设计。考虑到实验教学需要,外部存储器接口设有SDRAM、FLASH、ADC和DDS4种。

2.2.1 同步存储器接口

同步存储器的同步是指 Memory工作需要同步时钟,内部命令发送与数据传输都以该同步时钟为基准。

SDRAM采用同步存储器接口。SDRAM(Synchronous Dynamic Random Access Memory)是同步动态随机存储器,动态是指存储阵列需要不断的刷新保证数据不丢失,随机是指数据不是线性依次存储,而是自由指定地址进行数据读写。所选型号为MT48LC4M32B2,因为它速度较快,价格便宜,存储容量为128Mb (1M x 32-bit x 4 Banks)。它有4个Bank,块地址线BA0,BA1;地址线12根,A0~A11,(行地址A0~A11,列地址A0~A7);数据线32根,DQ0~DQ31。

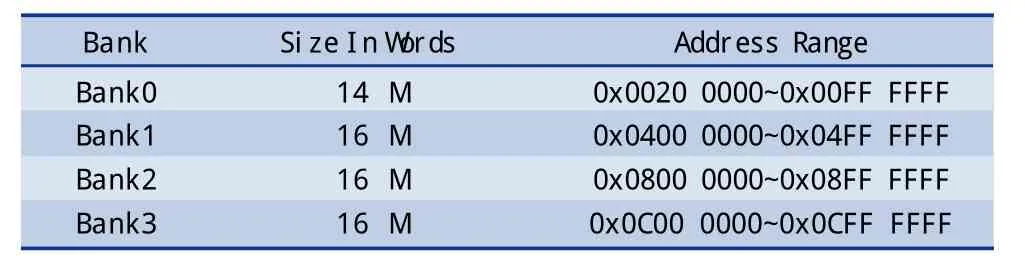

外部存储器SDRAM地址空间分配范围如表1所示。

在这里选择BANK2,相应的则选择MS2作片选(低有效)。32 bitSDRAM的地址必须从addr1开始,因此将DSP的addr1和SDRAM的A0相连,DSP的SDA10必须和SDRAM的A10相连。

2.2.2 异步存储器接口(Asynchronous Memory Interface, AMI)

表1 外部存储器SDRAM地址空间

该部分由FLASH存储接口、AD存储接口、DDS存储接口3部分组成,根据ADI提供的硬件设计手册,其设计标准如下:

时钟达到166 MHz,I/O口电压为3.3 V。AMI在Bank1,Bank2,Bank3的外部存储器中支持1 6 M的字,在Bank0的外部存储器中支持12 M的字。读写需要花费至少3个外围时钟周期来完成。外部存储器非SDRAM存储空间分配范围如表2所示。

表2 外部存储器非SDRAM存储空间

(1)FLASH存储

FLASH型号为AM29LV0819B,8Mb(1M*8bit),地址线20根,A0~A19;地址线8根,DQ0~DQ7。芯片主要性能如下:访问时间为80 ns;编程擦除电流为15 mA;读操作时电流为7 mA。另外,它还可以作为DSP程序引导,根据21369芯片特性,MS1可用于FLASH boot模式中,因此选定MS1作为片选。

(2)AD采样转换电路

实时数字信号处理系统必须通过 A/D转换将输入的模拟信号转换成数字信号,也可用于采集DDS信号,所选型号为MAX1322,2通道高速同步采样并行接口14 bit模数转换器。 ±5 V到±16.5 V的电压容错范围。选定MS0作为片选。

(3)DDS信号发生电路

该部分电路以单片集成DDS芯片AD9831为核心,包括3根地址线,16根数据线。该芯片集成包括相位累加器、正弦表和10 bitD/A转换器,可实现信号的相位和频率调制,其时钟频率最高可达25MHz。配合相应算法可以发出单频、FSK、PSK等多种规则信号和一些专用特殊信号。信号通过一个单运放低通平滑滤波器电路输出,该电路同时对AD9831起到保护作用。产生的信号可通过系统的DDS输出端子输出,也可通过跳线连接A/D输入,成为一个信号发生器,即实验中无需再外接信号发生器。使用中应注意DDS输出不可短路。

在选定号各存储器件后,需进行外部存储器的地址分配,本实验系统采用表3地址分配方式。

表3 外部存储器地址分配表

2.3 数字应用接口DAI

2.3.1 音频模块

选用多媒体数字信号编解码器AD1835,它有4个立体声数模转换(DACs)做音频输出,一个立体声模数转换(ADCs)做音频输入。可实现所有通道中96 kHz采样速率输入输出数据,其中一个DAC通道采样速率可达192 kHz。

DSP处理器通过DAI接口和AD1835芯片相连。DAI引脚被配置成以时分复用(TDM)模式或2线接口模式(TWI),从AD1835传输串行数据.AD1835的主输入时钟(MCLK)可以由板上12.288Mhz晶振产生,或者由DSP处理器上的DAI引脚提供,并通过开关配置。

AD1835音频通过开关能被配置成主模式或从模式。在主模式下,音频芯片驱动串口时钟和帧同步信号给DSP处理器。在从模式下,DSP处理器产生和驱动所有的串口时钟和帧同步信号。

2.3.2 S/PDIF数字音频接口

ADSP-21369带有S/PDIF (Sony/Philips Digital Ubterface)标准的串行接口,可实现各种音频设备间的数字音频数据传输。其最大优势是不需进行模拟信号转换就实现设备之间的数据传输。

SHARC处理器的S/PDIF发送器可以从任何串行输入口接收数据。发送器的串行数据输入字宽为16, 18, 20或24 bit,数据格式可以是左对齐,I2S或右对齐。S/PDIF发送器的串行数据,时钟和帧同步输入通过信号路由单元(SRU)指定路径。

2.3.3 LED灯的控制

学生可以通过编写实验程序,控制相应的引脚实现对LED灯的状态控制。

2.4 数字外设接口DPI

2.4.1 UART异步串行接口

ADSP-21369支持2个UART,本系统只用到UART0,通过芯片(型号为MAX3232)进行电平转换后与DB9(公口)串口相连。

UART使能开关可以选择是否连接DSP处理器DPI引脚的UART信号,当开关关闭时,其相关DPI信号可用于接口扩展,增加系统的灵活性。

2.4.2 LCD显示屏

SHARC处理器带有2个符合工业标准的同步串行接口SPI,每个SPI有其对应的寄存器配置,并支持与各种外设通信。本实验教学系统中,其SPI应用于LCD显示接口设计。

系统采用MzLH01-21864液晶显示屏,为128x64点阵LCD显示模组,自带2种字号的一、二级汉字库,基本绘图 GUI 功能和2种字号的ASCII码西文字库。

模组上为串行 SPI接口,除电源和背光之外通讯仅需要连接从机选择线(SS)、时钟线(SCK)、数据线(SDA)及BUSY 线即可;接口简单、操作方便;与各种MCU均可进行简单方便的接口操作。LCD显示模块电路如图2。

图2 LCD显示模块电路

2.4.3键盘

本实验系统采用4*4键盘,用于实验数据输入。4*4键盘共有16个按键,排列成4行4列的矩阵形式的分布,I/O口连接每行和每列,用8个I/O口通过扫描方式实现对16个按键的识别,这种模式可有效节省I/O口资源。

2.5 JTAG接口模块

接口可实现对实验教学系统的程序下载、硬件调试。本系统中采用14针JTAG接口设计方式。

3 结束语

本实验教学系统采用SHARC系列的ADSP-21369浮点处理器,拥有4种外部存储器,DPI、DAI接口丰富,如LED、LCD、音频、键盘、UART、S/PDIF等,与TI系列实验教学系统相比,可更好的满足实验教学需要,能够充分调动学生的自主性,锻炼实际动手能力。该系统可作为实时DSP技术及浮点处理器应用的教学试验平台,也可作为铁路轨道信号相关课题的研究平台。

[1] 刘书明. ADI DSP应用技术集锦[M] . 北京:电子工业出版社,2009.

[2] 冯小平,罗勇江,罗明. ADSP技术与应用[M] . 北京:机械工业出版社,2007.

[3] 杜普选,马庆龙. 实时DSP技术及浮点处理器的应用[M] .北京:清华大学出版社及北京交通大学出版社,2007.