基于DSP的USB数据采集系统设计

杨传文,陈春俊

(西南交通大学机械工程学院,四川成都 610031)

0 引言

现代工业的快速发展,传统的数据采集方法已很难满足现代信息技术实时高效的需求。USB以其传输速度快、支持热插拔、即插即用、可扩展性强等优点[1],广泛应用于人们生产、生活之中。USB2.0规范能够提供高达480Mb/s的传输速度,虽然USB3.0传输速度比USB2.0高,但现今应用仍以USB2.0为主,因此本文所述的数据采集系统采用USB2.0接口进行设计。

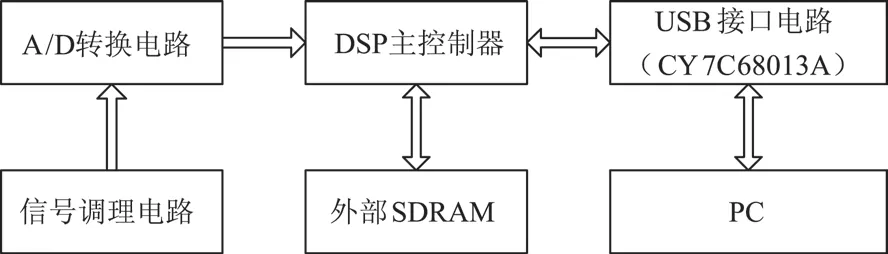

1 系统的总体设计

系统总体设计结构如图1所示,系统由信号调理电路、A/D 转换电路、DSP 主控制器、USB接口电路、PC 组成。总体来说本系统分为两大部分:数据采集部分和数据传输部分。 PC USB接口提供的5V 电压,能够满足系统需求。因此,系统电源由USB 接口提供,通过USB 供电还可以减少由于使用外接电源而引进的工频干扰。

图1 系统的总体结构图

TI 公司的28系列TMS320F28335 DSP 作为主控制器,但主控芯片内部程序空间和数据空间RAM 仅为34KB,明显不够用,因此外扩了一个256KB的RAM-IS61LV25616-12T。在外扩RAM中开辟2块512大小的数据缓冲区,用于对采集到的数据进行预存储。

2 系统的硬件设计

2.1 A/D转换电路设计

信号在进行A/D 转换之前,经过信号调理电路对信号进行预处理,用以减少干扰的影响,提高信号的信噪比。

A/D 转换电路采用美信公司MAX1320模数转换芯片。其片选信号CS 连接到主控制器的GPIO4;主控芯片的EPWM2B 信号与它的COVNST 相连,作为A/D 转换的启动信号,可以通过设置EPWM的频率值,实现已知固定频率的数据转换;EOC与ELOC 分别连接至主控芯片的GPIO7与GPIO16,用以产生主控制器的中断信号,通知主控制器读取并行数据线上的数据。

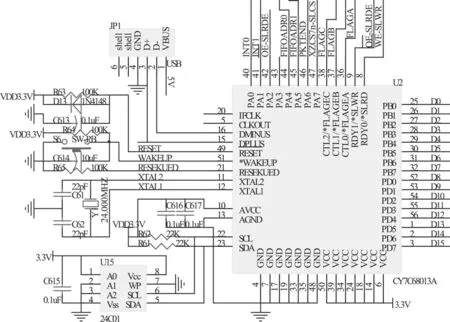

2.2 USB接口电路设计

USB 接口电路设计是本系统设计的核心部分,USB 接口电路由CY7C68013A 及其外围电路构成,主要完成数据从主控芯片到PC的高速连续传输及控制命令从PC 传到主控芯片。USB 接口电路如图2所示。

图2 USB 接口电路设计

CY7C68013A 采用上电自动复位方式进行复位操作。CY7C68013A时钟信号由一个24MHz 石英晶振提供,晶振的两个管脚连至CY7C68013A的XTAL1、XTAL2引脚。在本系统中,USB 设备是工作于Slave FIFO模式,作为主控芯片的一个外设,其片选信号引脚PA.7/*SLCS#连接至主控芯片的Zone6的选通信号XZCS6n,输出使能信号SLOE和读写控制信号SLRD、SLWR 分别接至主控芯片对应的读写控制信号XRD、XWE0。数据线接主控芯片的低16位数据接口XD[0…15]。芯片通过I2C 总线外接了一个EEPROM 用于存储设备启动所需信息。CY7C68013内部有4KB 内部FIFO,通过FIFOADDR[0,1]分别选通EP2、EP4、EP6、EP8,其选通信号连接至地址线的XA1与XA2。

3 系统软件设计

系统的软件设计主要包括CY7C68013A 固件程序及其驱动程序设计、主控芯片程序设计、上位机应用程序设计。

3.1 CY7C68013A固件程序及驱动程序设计

3.1.1 固件程序设计

固件程序设计是开发CY7C68013A 芯片的核心,CY7C68013A 有3种工作模式:Master GPIF、PORTS、Slave FIFO模式[2-4]。本系统的特点是快速持续传送大量数据,同时对于数据传输的准确性——完备性要求很高,故采用异步通信模式,使CY7C68013A工作于异步Slave FIFO模式,固件程序完成CY7C68013A 芯片初始化和配置工作。

固件设计采用Cypress 公司提供的固件函数框架,使用Keil uVision4集成开发环境,最后通过Cypress 公司的EZ-USB Control Panel 控制面板完成固件程序的装载。通过编写的TD_Init()初始化函数,即可实现对它的初始化工作,主要配置语句如下:

CY7C68013A 配置为异步Slave FIFO模式,8051内核不对数据进行处理,将传输数据进行自动打包(AUTOIN=1)处理,采用批量传输方式,总线宽度为16位,使用EP6作为IN 端点,配置成2缓冲512字节,将数据传至PC。EP2作为OUT 端点,上位机的控制命令通过EP2传至主控制器。EP2、EP6分别映射到主控制器zone6的0x10FC00、0x10FC06地址,主控制器向地址0x10FC06写数据,即把数据写入EP6。

3.1.2 设备驱动程序设计

USB 设备驱动程序设计是开发本系统的一个关键,USB 驱动程序设计主要完成应用程序与USB 设备的通信协议的实现。在开发驱动程序的时,采用的开发包是Driver Studio 3.2和Microsoft 公司的WinXP_DDK,并以VC++6.0作为辅助开发环境,利用CYPRESS 公司提供的基于EZ-USB FX2的外设连接通用设备驱动程序包[5-6],对该驱动程序包稍加修改,使之成为适合本系统能自动下载固件和完成设备重枚举功能的驱动程序。

3.2 主控制器程序设计

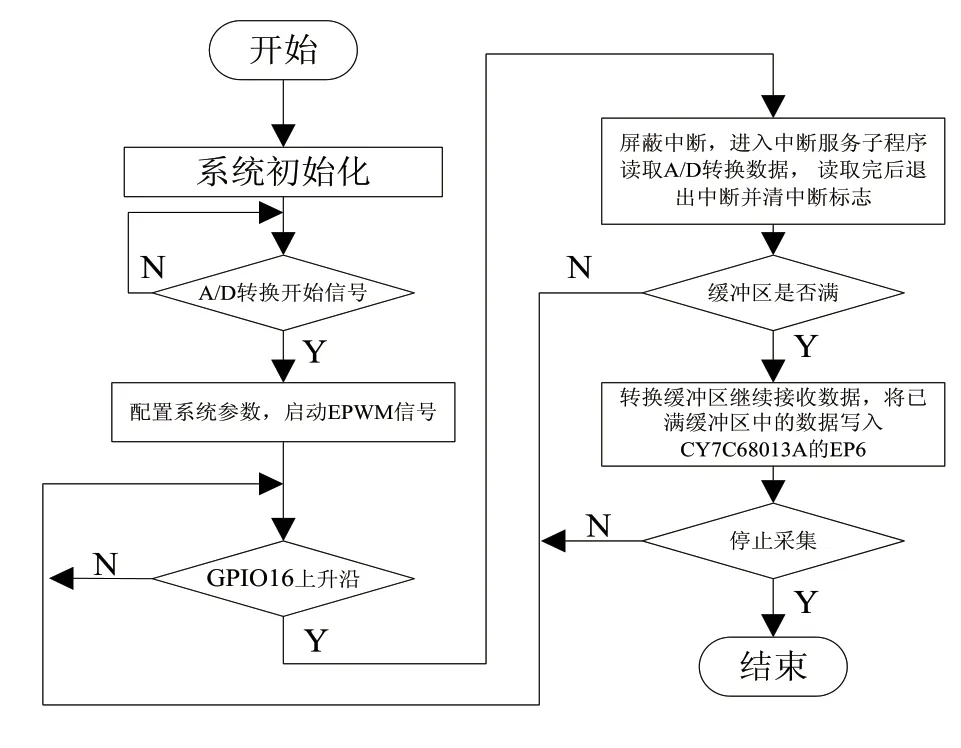

主控制器程序主要完成数据采集和数据传输的功能,使用CCS3.3开发环境。程序流程图如图3所示。

图3 主控制器程序流程图

数据采集在中断服务程序中完成,利用完成一组转换信号ELOC 触发一次中断,继而在中断服务程序里完成对8个通道数据的读取,把MAX1320端口数据寄存器的数据读入RAM所开辟的数据缓冲区里。每进入一次中断程序就执行一次清除中断标志,以接收下一次中断,进行下一次数据采集。MAX1320芯片启动A/D 转换的启动触发信号是通过主控芯片的EPWM2B 信号触发,通过设置TBPRD 寄存器更改EPWM 波形的频率,从而实现要求固定已知频率的A/D 转换。

当前存储数据的缓冲区满之后,把数据写入CY7C68013A 端点EP6所对应的地址0x10FC06,交由USB 送入上位机。并采用开辟的另外一块缓冲区来继续接收数据。

3.3 上位机应用程序设计

上位机应用程序设计利用VC++6.0开发工具完成,上位机程序向USB 设备发送各种命令信号,接收USB 设备传送的数据并对接收的数据进行存储、显示操作。上位机应用程序调用CreateFile()函数用来获取USB 设备的句柄,用以确认有USB设备连接到主机,获取USB 设备句柄之后调用DeviceIoControl()函数向USB 设备驱动程序发送I/O 请求完成数据的读写操作[7-8],USB 端点寄存器的数据通过此句柄函数传送给上位机,既而进行存储、显示等操作。

4 实验测试

选用一个标准正弦信号作为信号源进行实验验证,信号频率20Hz、幅值0~3V,系统采样频率为5 kHz,图4为系统所采集数据的分析结果。

图4 测试结果分析图

图4的分析结果可知,本系统采集的数据的时域信号波形与信号源吻合,对采集的数据进行FFT 变换,得到信号最大频率点值为19.53 Hz,考虑到数字信号的离散性,两个频率点之间有一定的信息损耗,故测试结果是准确的,系统满足设计要求。

[1]寇静.基于端口模式的CY7C68013固件程序设计[J].微计算机信息,2010,26(2-2):116-117,120.

[2]Cypress Semiconductor.EZ-USB FX2 Technical Reference Manual[Z].2001.

[3]马俊涛,李振宇.Slave FIFO模式下CY7C68013和FPGA的数据通信[J].中国传媒大学学报:自然科学版,2009(6):38-44.

[4]王静红,刘教民..采用CY7C68013芯片的系统固件程序设计[J].河北师范大学学报,2008,32(2):169-173.

[5]胡文静,陈松.基于EZ-USB芯片CY7C68013的驱动程序设计[J].计算机应用研究,2005(9):220-221,228.

[6]徐夏,雷明.基于CY68013的数据通信系统设计[J].微计算机信息,2009,25(6-2):198-199,205.

[7]李国柱.基于单片机和USB接口的数据采集系统设计[J].计算机应用技术,2009(4):65-67,75.

[8]张礼勇,王娟,张旭辉.基于CY7C68013的电力线载波通信模块设计[J].哈尔滨理工大学学报,2008,13(1):14-17.