USB直接制版机高速发排卡的设计与优化

苏政伟,陈科明,马 琪

(杭州电子科技大学微电子CAD研究所,浙江杭州310018)

0 引言

发排卡是一种用来连接印前设备和输出设备的印刷业专用设备,主要功能是把PC机里的版面文件处理成点阵格式后发送给输出设备[1]。按其采用的接口技术可以分为PCI发排卡、USB发排卡等。近年来,USB发排卡凭借发排速度快、通用性强、支持即插即用等优势,逐渐取代PCI发排卡成为主流。但是USB发排卡还是存在发排速度不高、稳定性不够、系统通用性和可扩展性不足等问题。本文根据实际需求,设计了由FPGA专用硬件逻辑、USB2.0接口芯片及SDRAM存储器构成的USB发排卡系统结构,同时从软硬件两方面对发排卡的发排速度、系统稳定性进行了优化,优化后发排速度高达30MB/s,并且性能稳定。

1 工作原理概述

直接制版机(Computer To Plate,CTP)是一种数字化印刷成像的光机电一体化设备,将文字、图像转变为数字信号,用此信号驱动激光器在专用版材上扫描成像,再用显影液显影生成印版[2]。CTP设备主要应用于大型印刷企业,如报社印刷厂和商业印刷厂等等。

CTP系统如图1所示,包括PC机、CTP控制系统、USB发排卡、LD驱动电路和激光器等。USB发排卡的主要功能是通过USB从PC机取得激光打点数据,并转发给LD驱动电路进行激光打点。

图1 CTP系统框图

2 硬件设计

2.1 USB发排卡硬件结构设计

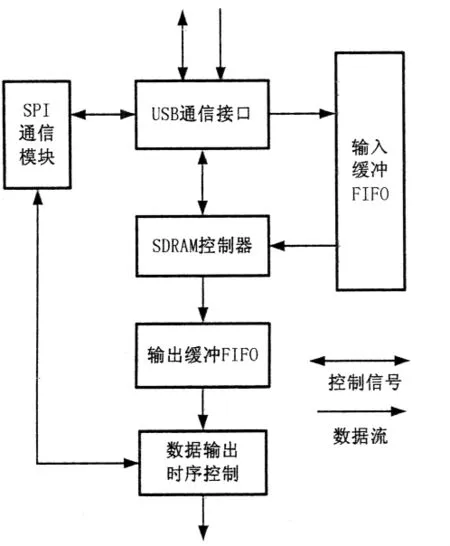

USB发排卡硬件结构如图2所示,主要包括FPGA主控制器、USB接口、SDRAM存储器、SPI通信接口、编码器输入和LD驱动接口等模块,主控制器用Altera EP1C6Q240 FPGA芯片实现。

PC机发排软件将版面数据发送到USB接口模块,FPGA主控制器将版面数据放SDRAM中缓存。在激光扫描过程中发排卡的数据必须和CTP的机械运动相配合,因此将编码器输入的CTP系统行同步信号和位同步作为读数据的时钟,按照一定的时序关系将SDRAM中暂存的版面数据输出至LD驱动接口模块。为了提高传输速度,结构设计中采用了面积换取速度的思想,用两块SDRAM进行乒乓操作来轮流读写数据[3]。LD驱动接口模块负责将输出的并行数据转换成高速的串行数据,输出到CTP的LD驱动电路。SPI通信模块则负责发排卡与CTP控制系统的通信,完成信息的交互和握手信号的传递。

图2 USB发排卡硬件结构图

2.2 FPGA主控制器的硬件逻辑设计

FPGA主控制器的硬件逻辑结构如图3所示,划分为以下4个模块:USB通信接口、SDRAM控制器、与CTP控制系统的SPI通信模块、发排卡数据输出时序控制模块。在USB通信接口和SDRAM控制器之间,采用了一个1 024×16的FIFO作为输入数据的缓冲;而在SDRAM控制器与数据输出时序控制模块之间,则采用了一个4 096×16的FIFO作为输出数据的缓冲。

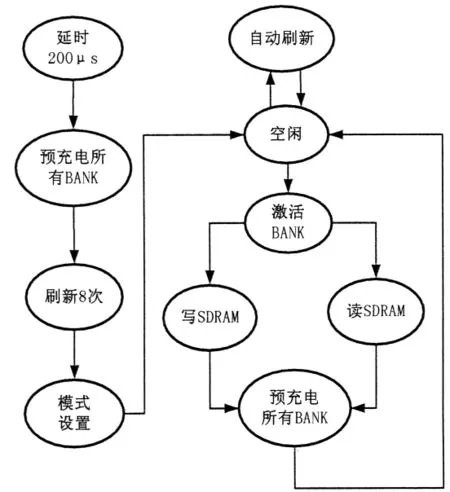

SDRAM控制器设计是FPGA主控制器硬件逻辑设计的难点。SDRAM的操作流程是:先初始化设置SDRAM工作模式,然后进行数据读写,同时通过刷新保持电容的数据。SDRAM控制器状态机如图4所示。

图3 FPGA主控制器逻辑结构框图

图4 SDRAM控制器状态机

由于USB发排卡的实际传输数据较大,设计中选择SDRAM的页猝发方式进行读写。对于设计选用的SDRAM芯片MT48LC16M16A2,一次要连续写入或读取512个字。但是在USB发排卡传输版面数据的最后一行时会出现传输数据小于512字的情况。本设计利用预充电命令中断猝发读写,可以解决这个问题。在版面数据传输结束时,把输入缓冲FIFO中的读地址传入SDRAM控制器,即传入SDRAM最后一行数据的大小N。写入时,在发起写入命令后的N-1个时钟,对所有BANK预充电中断页猝发写。读出时,在读取命令后的N+1个时钟对所有BANK预充电中断猝发读。此外本文采用了集中刷新方式解决了刷新与读写数据的冲突。当刷新定时器计数到时,若正好有数据传输,会先让数据传输继续。数据传输完成后,利用数据传输的时间间隙再连续刷新多次,这样能保证SDRAM中的数据不丢失。

3 软件设计及优化

本设计开发的软件包括上位机发排软件动态链接库和USB固件程序。为了保证数据传输的连贯性,发排卡输入端USB的传输速度应该大于发排卡输出端LD驱动电路的传输速度。发排卡实际的数据传输速度由CTP系统的LD驱动电路和激光器的路数所决定,当CTP系统采用更多路的激光器时,LD驱动电路数据传输速度就要求更快,USB的传输速度也要随之提高。本设计从上位机软件、USB驱动程序、USB固件等几方面对USB传输速度进行了优化,最高传输速度能够达到30MB/s,提高了发排卡的发排速度。

3.1 发排软件动态链接库的设计与优化

发排软件动态链接库是在Microsoft Visual C++6.0开发环境下,使用CYPRESS提供的CYAPI.lib库文件进行设计,实现对USB设备的管理和控制[4]。本文在动态链接库中设计了通用的USB数据传输函数,屏蔽了USB传输的细节,发排软件开发人员可直接调用,而不需要考虑数据传输的类型。本设计还对动态链接库中的函数进行了优化,以提高发排卡系统的性能。驱动程序中数据缓冲大小不足是造成USB传输慢的一个重要原因。本文通过将驱动程序缓冲大小设置为2MB,将USB传输速度由优化前的 13MB/s,提高到 28MB/s。

实际使用中还发现CY7C68013A芯片工作不稳定,导致数据传输被中断的现象。经大量尝试,发现对CY7C68013A进行软件复位能够解决这个问题。本设计通过端点0对CY7C68013A的CPUCS寄存器先后写入数据0x01和0x00来实现对芯片复位。

3.2 USB固件程序设计与优化

USB固件程序完成芯片的初始化、处理各种USB标准设备请求、重列举和电源管理。CYPRESS公司提供CY7C68013A固件程序的流程框架,设计中根据需求修改和添加固件框架中的描述符文件dscr.a51和外设功能文件periph.c中的代码,即可实现USB特定设备的功能[5]。

本设计从数据包大小和端点缓冲区配置两方面对固件程序进行一定的优化,以提高USB的传输速度。数据包大小的设置应该在协议消耗和剩余带宽之间取平衡。高速传输下,块传输允许的数据包最大值为512Byte。而数据包设置多大能使传输速度达到最佳,取决于传输的数据量以及端点的配置,需要根据实际情况测得。本文通过大量实验,测得在传输20MB数据时,数据包大小设置为480字节,USB传输速度最快。端点缓冲区大小对USB传输速度也有一定影响。多重缓冲结构可以在数据传输过程中有效提升数据带宽,平滑带宽抖动,减少传输等待的时间。本设计将端点缓冲区大小优化后配置为3×512字节,较原来的2×512字节的配置,USB传输速度有一定的提升。

4 结束语

本文设计了一种USB2.0高速发排卡,硬件上采用USB2.0+FPGA+SDRAM的设计结构,软件上通过对发排软件动态链接库和USB固件程序进行设计和优化,能够完成与主机的USB通信、版面数据的缓冲、与CTP控制系统的交互以及发排数据输出的时序控制,具有可扩展性强、传输速度高和传输连贯性好等优点。经过优化,发排卡的传输速率由13MB/s提高到了30MB/s,系统稳定性也有大幅提升。目前,发排卡已应用于实际印刷制版中。

[1] 王玉丽.基于USB2.0的直接制版机高速发排卡的设计与实现[D].苏州:苏州大学,2010.

[2] 于鹏.直接制版机控制系统和USB发排卡的设计与实现[D].苏州:苏州大学,2008.

[3] 刘延飞,杨铁阡,李琪,等.多总线地面测试设备中双SDRAM控制器的设计[J].电讯技术,2011,51(4):31-34.

[4] 何苏勤,黄翠翠.基于USB2.0的异步数据传输和控制接口的设计[J].应用天地,2010,29(3):79-83.

[5] 薛园园.USB应用开发技术大全[M].北京:人民邮电出版社,2007:202-205.