基于FPGA的数字信号传输性能分析仪

廖聪裕 鲁锦涛 苏建加

中国地质大学(武汉)机械与电子信息学院 430074

基于FPGA的数字信号传输性能分析仪

廖聪裕 鲁锦涛 苏建加

中国地质大学(武汉)机械与电子信息学院 430074

本设计采用FPGA产生数字信号发生器和伪随机信号发生器,通过三路不同截止频率的滤波器模拟出信号在信道中传输衰减情况,最后显示在示波器上,观察出眼图。整个系统由数字信号发生器、伪随机噪声信号发生器、低通滤波器、加法电路、数字信号分析电路,信号眼图显示器和单片机控制电路组成。最后通过对信号进行曼彻斯特编码并提取出编码中同步信号,在示波器上显示出眼图,实现了对数字信号传输性能的测试。

m序列;伪随机信号;FPGA;同步信号自提取

1 系统功能与组成框图

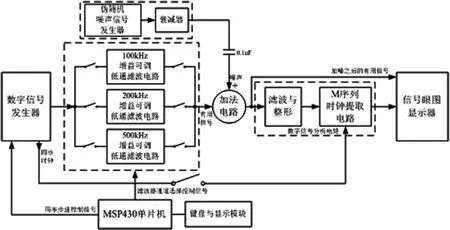

本系统总体结构如图1所示:

图1 系统总体结构框图

该系统模拟了数字信号的发射、信道传输,信号的接收过程,并实现了信号传输性能测试功能。整个系统由数字信号发生器、伪随机噪声信号发生器、低通滤波器、数字信号分析电路、信号眼图显示器和单片机控制电路组成。其中数字信号发生器和伪随机信号发生器均由FPGA产生。数字信号发生器由低通滤波器输出,并通过加法器电路与伪随机信号发生器电路相加,送至示波器进行显示。数字信号分析电路通过提取曼彻斯特编码的同步信号,在示波器上显示出眼图。

2 理论分析与计算

2.1 低通滤波器的设计

由于每阶低通滤波电路在理想状态下的十倍频程衰减为20dB,要使该电路的十倍频程衰减不少于40dB,因此为满足要求须采用2阶以上的滤波电路,因此采用由二阶有源低通滤波电路和一阶无源滤波电路组成的三阶低通滤波电路。

2.2 m序列数字信号的产生

n阶的m序列的周期为2n-1,数字信号发生器产生8阶的m序列,因此采用FPGA产生9个D触发器构成线性移位寄存器;伪随机信号发生器产生12阶的m序列,因此利用FPGA产生13个D触发器,构成线性移位寄存器。可以通过改变D触发器的时钟频率来改变输出的数据率。

2.3 同步信号提取

曼彻斯特码是一种用跳变沿来表示要传输的二进制信息,要想解码,首先要将同步信号从曼彻斯特编码中解出。本设计采用了纯软件的方法直接从曼彻斯特码中解出:先固定一个时间,利用曼彻斯特编码中包含的时钟信息,在这一段时间中找出最小的时钟周期。在最坏条件下的也只需要2*Tm/Tclk。其中Tm表示m序列的周期且Tm=2n-1,n表示m序列的阶数。Tclk表示数据传送的比特率,也就是数据时钟。经计算,提取同步信号所需要的时间不会超过51.1ms。

3 电路与程序设计

3.1 硬件电路实现

3.1.1 滤波与增益控制电路

低通滤波器截止频率分别为100kHz、200kHz和500kHz,并且通带增益在0.2—4内可调,本设计利用运算放大器OPA602来构成滤波器和反相放大器,这样既可以实现滤波,又可以满足将TTL电平放大4倍增益的要求。

3.1.2 加法电路

数字信号发生器和伪随机信号发生电路可以通过加法电路实现相加。本设计通过LM318,实现一个反相加法电路。

3.2 系统软件设计

本设计利用FPGA实现了同步时钟信号的提取。在曼彻斯特编码的上升沿到来时利用FPGA的50MHz有源晶振输出的时钟对其进行计数,在下降沿的时候停止计数,从而得到解码时钟的分频系数,与此同时产生启动信号同样的对50MHz时钟信号计数得到同步信号。利用同步信号经过D触发器产生了一定的延时,使得时钟的上升沿对准了有效的数据位,此时将数据读出就可完成了解码。

4 结语

通过测试,数字信号发生器可以生成m序列,伪随机信号发生器和滤波器已经全部达到预期要求。除了完成对曼特斯特编码,提取同步时钟信号之外,还完成了对曼彻斯特编码的解码部分。通过对这些结果的分析,成功模拟出数字信号在传输过程中的特性。从结果可以看出,眼图和噪声之间有直接的关系,当噪声越大的时候,眼幅度就会变小。当噪声降低的时候,眼幅度会相应增大。因此眼图可以准确地反映出信号在信道传输中的噪声水平。

廖聪裕,男,湖北省武汉市人,从事测控技术与仪器研究。)