VW550多路图像集成显示系统设计与实现

陆小锋,王卓磊,陆亨立,郭众磊

(上海大学通信与信息工程学院,上海 200072)

大尺寸、高分辨力、效果多样的屏幕显示技术在科学研究、交通指挥、展示、娱乐等方面得到了广泛应用。实现更大尺寸、更高分辨力、更多特效的一个有效方法就是将多台成像设备(DLP或LCD屏幕)拼接起来形成一个逻辑上统一的超大屏幕显示系统。多个LCD或者DLP屏幕拼接完成的超大尺寸显示系统与常规的单屏幕显示系统相比,能够将用户需求的更多视频信息、交互信息进行同步显示与操作,满足不同用户对于可视内容多而全的需求,从空间上扩展了显示分辨力。目前大屏幕拼接系统已经逐步在电力系统、会展系统、交通系统等方面有广泛应用[1-3]。专业拼接型大屏幕系统的核心硬件组件便是多路、多制式视频图像集成处理显示系统。

本文介绍的VW550多路图像集成显示处理系统由4块主控板卡(Main Card)、1块视频矩阵板卡(Video Matrix)和1块VGA矩阵板卡(VGA Matrix)组成,全部通过PCI总线实现数据连接和信号控制,在后台计算机的控制下完成了多路图像在2×2拼接屏幕上的图像信号实时显示,并能够实现画中画、叠加、移动、图像切换等特效功能。系统硬件设计特别是控制器主要基于Altera公司的FPGA与CPLD实现,采用了灵活的SoPC技术,具有很好的系统可扩展性和剪裁性,系统功能调整方便,降低了开发成本[4-5]。

1 多路图像集成显示系统总体设计

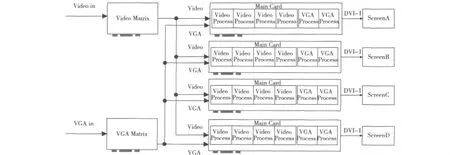

多路图像集成显示系统主要由Main Card,Video Matrix和VGA Matrix这3类硬件板卡组成。图1所示为系统总体设计框图。

16路CVBS视频信号或8路S-Video视频信号经由Video Matrix按用户设定要求分配给后端的Main Card,系统支持PAL与NTSC制式视频格式,每块Main Card可获取其中任意4路CVBS或2路S-Video。同时,4路VGA信号通过VGA Matrix,其中每块Main Card可以获取其中任意2路VGA信号。Main Card支持同时处理4路CVBS(或2路S-Video)和2路VGA信号,通过DVI接口输出到单屏分辨力为1400×1050的DLP投影屏幕组成的2×2大屏拼接墙。通过后台计算机控制软件,支持用户通过简单操作透明的完成Video和VGA信号切换、图像的跨屏显示、画中画、画面的亮度调节、对比度调节等特效与控制功能。

图1 多路图像集成显示处理系统总体设计框图

2 多路图像集成显示处理系统主要模块设计与实现

2.1 Main Card 软硬件设计

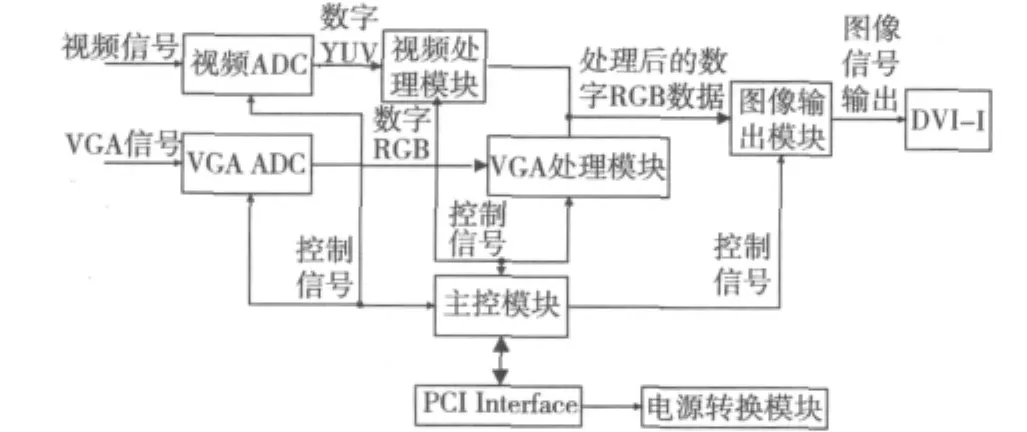

Main Card主要由视频ADC与视频处理模块、VGA ADC与VGA处理模块、PCI总线适配模块、系统整体逻辑主控制模块和图像输出模块等硬件模块。各模块硬件连接框图如图2所示。

图2 Main Card硬件模块连接图

2.1.1 视频ADC与视频处理模块设计

视频ADC模块采用Philips公司的SAA7114,由整体逻辑主控制模块通过I2C方式控制,完成将输入的模拟视频信号数字化,解码后传送给后端的视频处理模块。在本系统中,通过I2C配置使得SAA7114输出16位YUV数字视频信号。

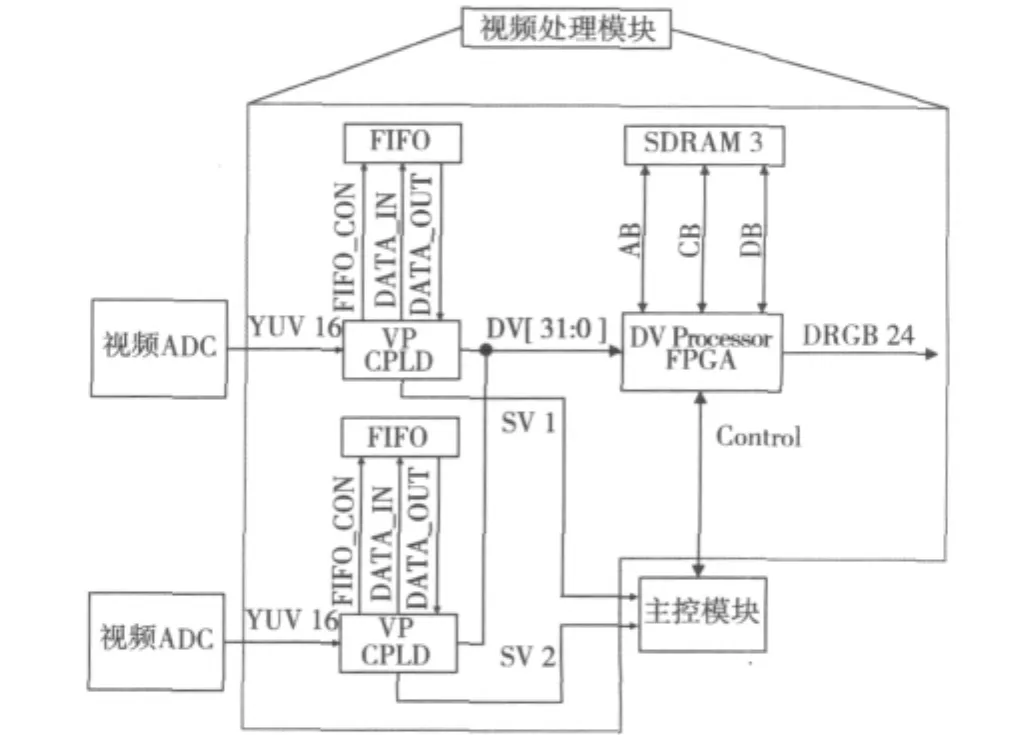

视频处理模块从视频ADC模块接收数字化YUV信号后进行隔逐行变换、帧频提升等处理,因此对数字YUV信号进行缓存。由于多路输入视频信号是异步采集,在后端屏幕上同时显示时需要完成输出场频同步的操作,为了节省大量的SDRAM存储器及其带来的PCB布板困难,本设计中没有采用传统的多片SDRAM轮换读写方案。如图3所示,在本系统中,对每路输入的独立异步视频信号首先输入由1片CPLD控制的FIFO缓存,通过慢写快读模式,能够保证多路异步视频的同步读入后续由FPGA控制的3片并联SDRAM中,进行包括隔逐行变换、帧频提升、图像插值运算等操作。

图3 视频处理模块信号框图

2.1.2 VGA ADC与VGA处理模块设计

VGA信号ADC模块电路核心芯片是AD公司的AD9884A。AD9884A是8位RGB模数转换集成芯片。它具有140 Msymbol/s(兆字符/秒)和500 Hz全功率的模拟带宽,能够支持1280×1024(SXGA)分辨力和75 Hz刷新率。输出信号 DR[7:0]、DG[7:0]、DB[7:0]是数字化的24 bit RGB分量,连同模数转换后的同步信号plsg(像素时钟)、hsg(行同步)一起传递到VGA处理模块。

VGA处理模块视频处理模块对数字化RGB信号进行插值运算、窗口“游动”等处理。因此对数字RGB信号也需缓存。本设计中每路VGA处理模块都采用1片FPGA与3片SDRAM组成处理核心。由于输入的模拟VGA是场频为75 Hz的逐行信号,因此无须帧频提升与隔逐行变换。对于输入的2路VGA信号不同步的问题,通过3片SDRAM的轮换读写操作实现同步化操作。SDRAM单片容量为128 Mbit,对于1400×1050的VGA信号,可以存放3帧图像;每片SDRAM都有3个状态Write,Wait和Read,对于某一路VGA处理,根据其独立同步信号写入SDRAM,读出数据则要根据基准同步信号输出;经过实验测试,在写和读状态中加入特定等待状态,可使2路VGA实现在异步输入前提下同步读出。

2.1.3 PCI总线适配模块设计

PCI总线适配模块主要完成后台计算机控制指令与多路集成显示处理板卡之间的控制指令通信桥接,整体逻辑主控制模块中FPGA硬件描述语言编程实现了PCI从模式的数据协议,节省了专用ASIC,降低了硬件开发成本。PCI总线适配器完全基于硬件描述语言通过状态机进行模块式设计。

2.1.4 系统逻辑主控制模块设计

系统逻辑主控制模块设计功能主要包括PCI协议适配以及根据PCI协议指令进行系统多种功能控制。其中PCI协议适配、视频与VGA的输出SDRAM多片轮换控制及系统同步逻辑控制完全采用硬件描述语言设计实现,系统功能控制采用在Altera FPGA中植入NiosII软核的方式通过软件实现。NiosII软核处理器丰富的外设接口时可以通过用户自己的需求来进行添加或删除,对于系统扩展性和成本控制都有益处。

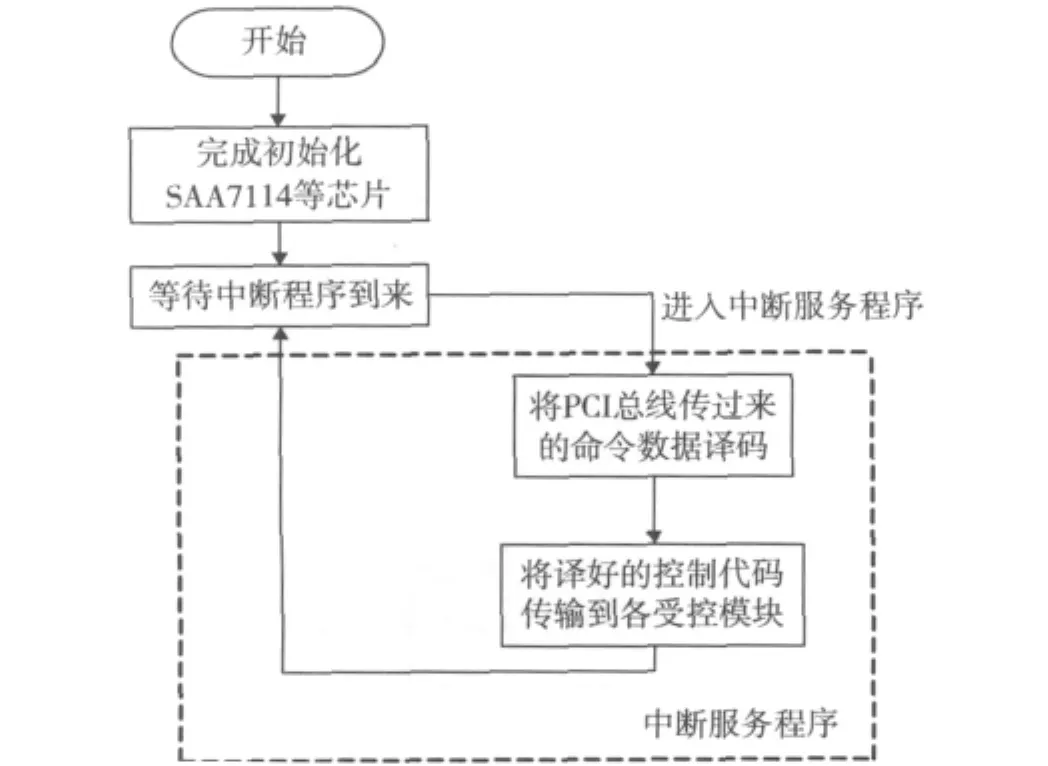

多路图像显示处理板卡从PCI总线上获得指令数据后,通过PCI总线适配模块处理后将数据放入片上FIFO,供NiosII处理器使用,而NiosII处理器通过自定义的片上数据总线来控制Main Processor中其他的模块以及多路图像显示卡上其他的模块。图4为NiosII微处理器中的程序执行流程,表1为NiosII微处理器解码PCI协议指令定义。

图4 主控制模块中NiosII软核主程序流程

表1 NiosII软核解码PCI协议指令定义

2.1.5 图像输出模块设计

本系统设计中视频输出格式支持VGA与DVI用户自选。图像输出模块中输出VGA模拟视频信号的芯片采用AD公司的ADV7197,支持3路兼容TTL输入的高速视频数字/模拟转换器,3个独立的10比特数据输入端口,可接收4∶4∶410 bit YCrCb 或 RGB 信号,或者4∶2∶210 bit YCrCb信号;输出DVI差分数字信号的芯片采用是TI公司的TFP410,支持从VGA到UXGA的分辨力(25 MHz到165 MHz的像素率),有12位双边和24位单边2种输入模式。ADV7197与TFP410由整体逻辑主控制模块通过I2C方式控制。

2.2 Video Matrix软硬件设计

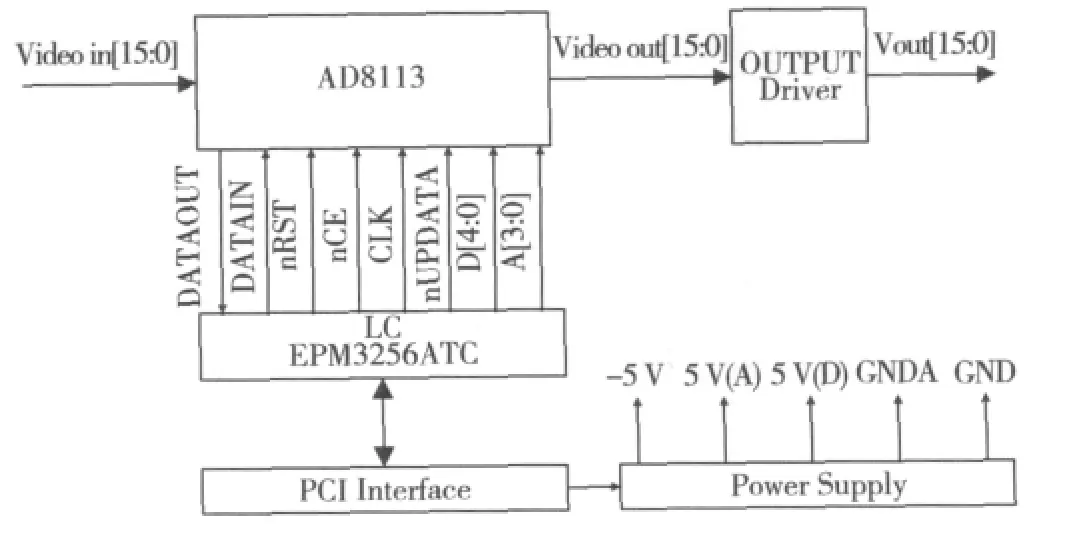

Video Matrix由视频矩阵模块和PCI总线适配模块组成。其中视频矩阵模块使用的是AD公司的AD8113,可以进行16×16的视频矩阵切换,通过并行或串行方式配置AD8113中的寄存器便可将16路输入的视频信号的任意一路输出到16路输出端口的任意一个,而完成对AD8113中的寄存器的配置以及修改是靠PCI总线适配模块来完成的,它的任务就是将PCI总线上传输过来的命令通过译码后去配置或更改AD8113寄存器。硬件与信号流程图如图5所示。

图5 视频矩阵板卡硬件与信号流程图

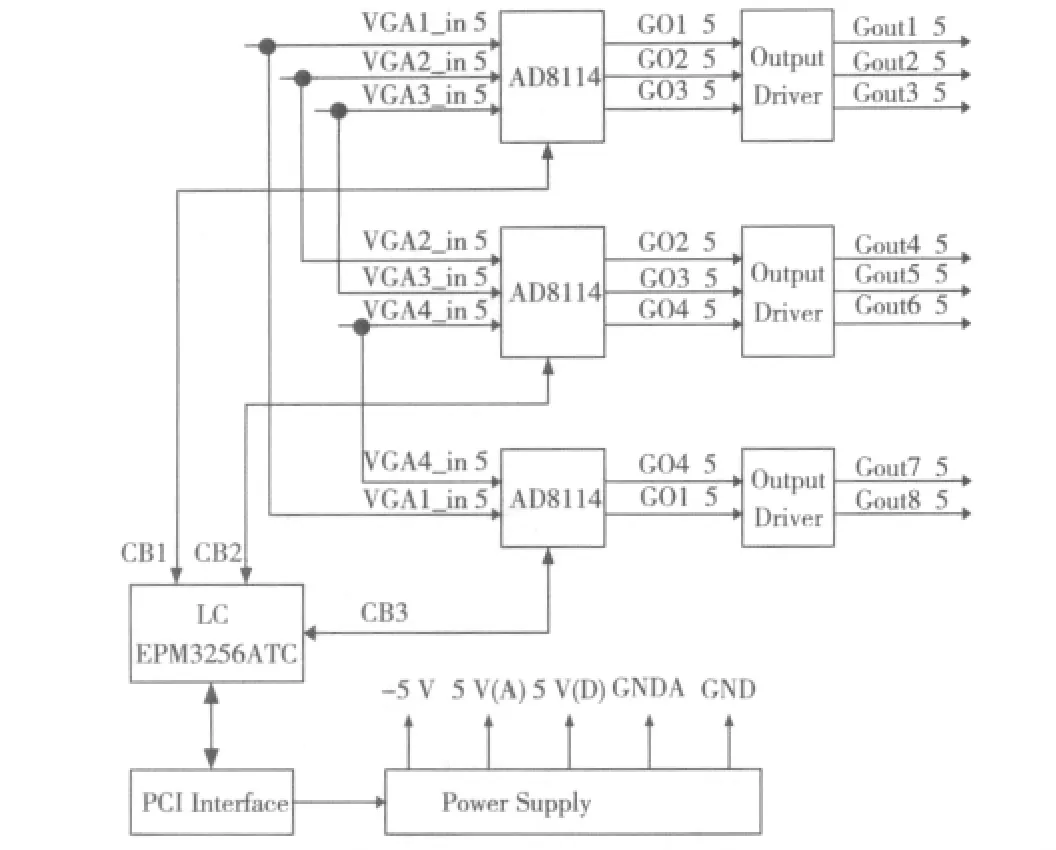

2.3 VGA Matrix软硬件设计

VGA Matrix的构成类似Video Matrix,由VGA矩阵模块和PCI总线适配模块组成,VGA Matrix中使用了3片AD8114分别对R,G,B这3个分量及每路的同步信号进行矩阵切换。图6为 VGA矩阵硬件与信号流程图。

图6 VGA矩阵板卡硬件与信号流程图

3 后台计算机PCI板卡WDM驱动程序设计与实现

要实现4块Main Card、1块Video Matrix和1块VGA Matrix插到计算机中通过上层用户软件对其进行控制,首先操作系统能够识别出这些板卡,需要编写WDM驱动程序。WDM分层驱动模型如图7所示。FDO表示功能设备对象,PDO表示物理设备对象。分层模型中PCI总线驱动程序与过滤驱动程序为系统自带,其中的功能驱动程序为自行设计[6-8]。

图7 WDM分层模型

本系统设计中选用DriverStudio+DDK的方法来编写PCI总线驱动程序,通过使用DriverStudio的生成向导可以的到PCI驱动的一个框架,通过DriverStudio定义的类函数,可以调用它们来完成用户需求的驱动程序。如图8所示,用户软件不是直接调用Win32 API函数来实现与驱动程序通信的,而是加了一层自定义函数库作为隔离。自定义函数库的本质是动态链接库,在里面对驱动的调用进行封装,可使编写上层软件的人员避免直接调用出错时产生的保护模式错误或者系统崩溃,同时也使上层软件编写人员无须了解底层硬件运作原理。

在自定义函数库中对VW550中Main Card,Video Matrix和VGA Matrix的各种操作进行封装,例如对Main

图8 用户软件与驱动程序间通信示意图

Card控制需要对图像缩放时窗口左上角坐标点、窗口长度和宽度的参数传递的函数进行封装。对于不同的设备、不同的功能就要定义不同的函数,这些函数通过“设备接口”去访问相应的硬件驱动,实现对各PCI设备上各功能的控制和使用。函数库对外只留出一个函数接口给上层应用软件编写人员使用,这样便可使编写出来的软件能够“透明”地控制VW550多路图像集成显示处理器。

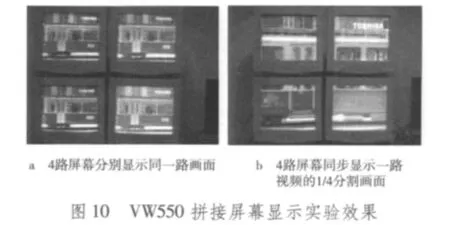

4 设计实现

本设计实现的系统硬件实物如图9所示,包括4块Main Card、1块Video Matrix和1块VGA Matrix硬件板卡实现了2×2拼接屏幕控制系统设计。系统显示效果如图10所示,图10a为4路屏幕上分别显示同一路视频,图10b为4路屏幕上同步显示一路视频的1/4分割画面。通过实验效果,本设计在多路异步视频同步化显示、SDRAM视频存储控制、PCI接口协议控制等方面较好地完成了系统功能设计,设计的硬件电路板卡已经能够在拼接大屏幕控制系统中进行有效应用。

[1]陆珉,邱钢,季晓勇.运用VHDL语言设计电视墙数字图像处理电路[J].微计算机应用,2002,23(1):10-13.

[2]丁玉珍.HDTV多媒体大屏显示墙系统方案[J].中国有线电视,2005(12):1182-1184.

[3]李建,吴久清,陈宁.大屏幕液晶数模一体电视机的设计实践[J].电视技术,2009,33(11):50-53.

[4]CILETTI M D.Verilog HDL高级数字设计[M].北京:电子工业出版社,2006.

[5]吴继华,王诚.Altera FPGA/CPLD设计高级篇[M].北京:人民邮电出版社,2005.

[6]徐晓画,高小鹏,龙翔.可定制PCI接口设计[J].计算机与数字工程,2005,33(10):123-126.

[7]张广华,苏秀琴,李哲.Windows2000下PCI数据采集卡WDM驱动程序设计[J].科学技术与工程,2006,6(12):1633-1635.

[8]宋海吒,唐立军,谢新辉.基于FPGA和OV7620的图像采集及VGA显示[J].电视技术,2011,35(5):45-47.