基于单片机的数字信号传输性能分析仪的设计*

李天山

(厦门海洋职业技术学院,福建 厦门 361012)

伴随着计算机的飞速发展和网络时代的到来,数字通信应用的领域越来越多,在通信的过程中各种干扰因素也随之而来,这些干扰的存在严重影响了数字信号的传输性能,因此设计一种能够及时快捷的检测数字传输通道的传输性能的分析仪有很长深远的应用意义。

1 系统整体设计

1.1 数字信号发生模块

m序列数字信号可通过移位寄存器的逻辑组合实现,其产生序列的速度非常快,我们可以采用TI公司的MSP430F169单片机为DDS定义时钟周期信号,达到输出信号数据率的步进可调。MSP430F169单片机在具有8MHz高速晶振的同时,还具有方便的切换超低功耗模式,从而大大降低系统的功耗,性价比高等特点。DDS在数字频率合成方面的优势具体体现在相对带宽宽、频率转换时间短、频率分辨率高、输出相位连续、可产生宽带正交信号及其他多种调制信号、可编程和全数字化、控制灵活方便等方面,并具有极高的性价比。

1.2 伪随机信号发生模块

利用有源晶振为移位寄存器提供时钟信号,电路易于实现,同时具有很强的抗干扰能力,有源晶振不需要单独搭建振荡电路,信号质量好,比较稳定,而且连接方式相对简单。本研究使用10M有源晶振。

1.3 数字信号分析电路

用FPGA对曼彻斯特码进行数据分析,并提取出信号的时钟周期,运用FPGA的优势是它的处理速度非常快,可以通过内部锁相环把外部时钟倍频,核心频率可以到几百兆。便于提取时钟信号。

2 理论分析与计算

2.1 m序列数字信号的参数与理论计算

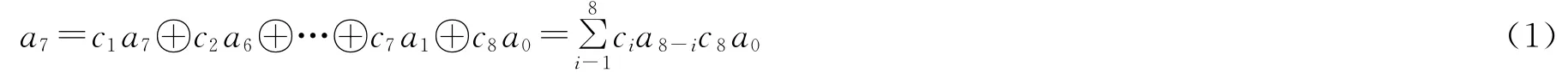

信号产生电路主要由MSP430单片机、DDS电路、线性反馈移位寄存器等部分组成。在数字信号发生器中运用的是八级线性反馈移位寄存器,电路图如图1所示。

八位移位寄存器的初始状态为a-1a-2…a-8,经过一次一位之后,状态变为a0a-1a-2…a-6,经过n次移位之后,状态变为a7a6…a1a0。再次移位一次,移位寄存器左端新得到的输入a8,可以写为

ci的取值决定了移位寄存器的反馈连接和序列的结构,故ci是一个很重要的参量。用特征方程表示为:

图1 八级移位寄存器电路图

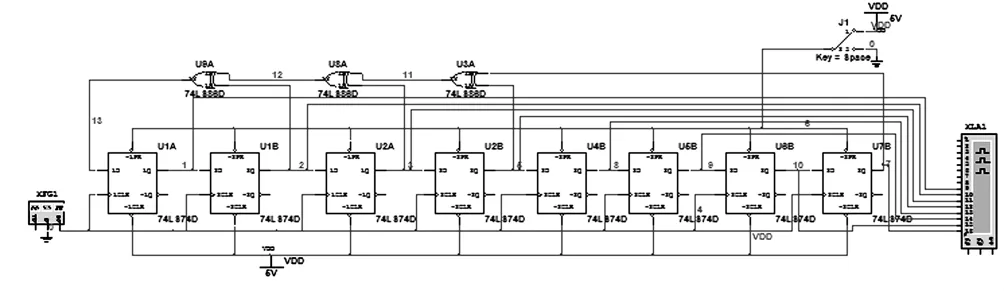

2.2 低通滤波器的参数计算

此模块采用三个截止频率分别为100K、200K、500K的二阶无限增益多路低通有源滤波器。对于截止频率为100K的滤波器,电路图如图2所示

2.3 同步信号的提取原理

本系统可以选择使用曼彻斯特码模式工作。曼彻斯特码在时钟前半周期和原码相同,后半周期和原码相反。因此要用数据选择器,在时钟信号为高电平时,选择原码作为曼彻斯特编码的信号,而时钟信号为低电平时,选择原码的反码作为曼彻斯特编码信号。

在数字信号分析电路中,需要对曼彻斯特码进行同步时钟信号的提取,具体的提取电路可以分为整形电路、微分电路、全波整流电路、窄带滤波电路和锁相环电路。利用这些电路来提取出同步信号,并经过FPGA对时钟信号和数字信号进行分析最终在示波器上显示出眼图。

图2 低通滤波器仿真电路

2.4 眼图的显示分析

数字信号在示波器上累积而显示出眼图,从眼图的形状可以看出码间串扰和噪声的影响,分析出传输信号的整体特征。一个完整的眼图应包含从“000”到“111”的所有状态,八种状态在短时间间隔内相叠加,即可形成眼图。可以根据计算得出眼图的消光比、Q因子等参数、眼交叉比和信号上升时间和下降时间。根据这些参数来判断信号的受干扰程度。

Q因子用于测量眼图信噪比的参数,它的定义是接收机在最佳判决门限下信号功率和噪声功率的比值,可适用于各种信号格式和速率的数字信号,其计算公式如下:

其中,“1”电平的平均值Ptop与“0”电平的平均值pbase的差为眼幅度,“1”信号噪声有效值σ1与“0”信号噪声有效值σ0之和为信号噪声有效值。

Q因子综合反映眼图的质量问题。Q因子越高,眼图的质量就越好,信噪比就越高。Q因子一般受噪声、光功率、电信号是否从始端到终端阻抗匹配等因素影响。一般来说,眼图中1电平的这条线越细、越平滑,Q因子越高。在不加光衰减的情况下,发送侧光眼图的Q因子不应该小于12,接收测的Q因子不应该小于6。

3 系统电路与程序设计

3.1 系统整体框图设计

图3 系统总体框图

如图3所示,本设计由MSP430单片机控制DDS电路为八位线性移位寄存器提供时钟周期,使移位寄存器产生f(x)=1+x2+x3+x4+x8的m序列数字信号。用10M有源晶振为十二位线性移位寄存器提供时钟周期,产生f(x)=1+x+x4+x5+x12的m序列伪随机信号。数字信号在经过三个低通滤波器后与伪随机信号在同向求和运算电路中合成为信号V2a。该信号经过电压比较器电路的整形后传输给FPGA进行同步时钟信号的提取,并利用时钟信号触发传输信号,在示波器上显示出眼图。从而判断系统数字信号的传输性能。

3.2 数字信号发生器的设计和原理图

本模块使用MSP430单片机作为信号发生的主控芯片,它定义DDS发出方波信号作为m序列数字信号发生器的时钟信号,使八位移位寄存器发出不同频率的数字信号,并实现了数据率在10—100kbps之间的步进可调。在此基础上,运用液晶12864正确显示出信号发生器的的步进率。

相位累加器由N位加法器与N位累加寄存器级联构成。每来一个时钟脉冲fs,加法器将控制字k与累加寄存器输出的累加相位数据相加,把相加后的结果送到累加寄存器的数据输入端,以使加法器在下一个时钟脉冲的作用下继续与频率控制字相加。这样,相位累加器在时钟作用下,不断对频率控制字进行线性相位累加。由此可以看出,相位累加器在每一个中输入时,把频率控制字累加一次,相位累加器输出的数据就是合成信号的相位,相位累加器的溢出频率就是DDS输出的信号周期频率。

为了避免在开始工作时移位寄存器进入全0状态,将组成的8级移位寄存器电路的D触发器中1~7级的复位端和第8级D触发器的置数端连接一个单脉冲发生器。当接通电源开始工作时,单脉冲发生器会产生一个开机复位脉冲,就使移位寄存器开始工作时不会进入全0状态。理论上在接通电源以后,这个由8级D触发器所组成的移位寄存器电路就会产生P=63的m序列。

4 系统测试和数据分析

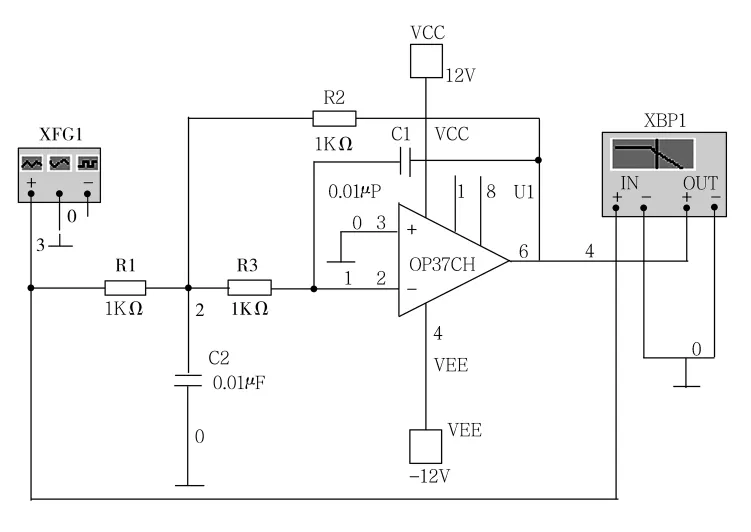

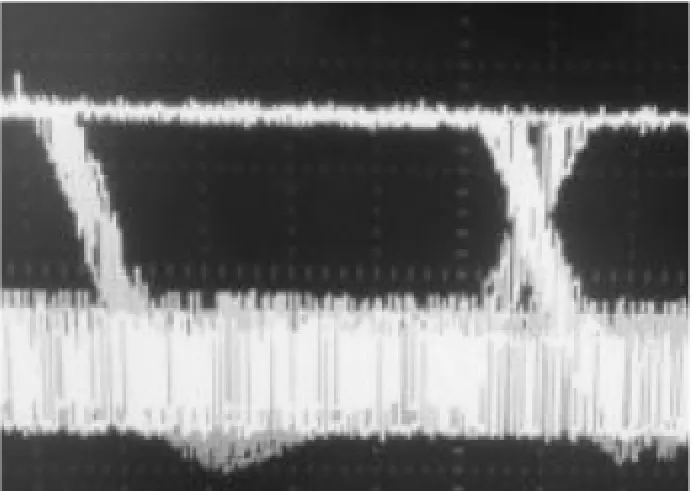

通过示波器观察在有干扰信号和无干扰信号两种状态下的眼图波形如图4和图5所示。

图4 实测无噪声眼图

图5 实测加入噪声眼图

通过示波器可以观察到当加入的伪随机信号的幅值不同时得到的眼图的幅度、消光比、眼交叉比会发生相应的变化,从而可以分析出该数字信号传输的性能。

经测试,本次设计已完成m序列随机数字信号发生器、伪随机码发生器、并通过曼彻斯特编码进行传输、三个低通滤波模拟实际数字信号传输、曼彻斯特编码同步信号提取模块等各项功能,并均达到实际应用的各项指标。

5 结束语

在数字时代的浪潮中,数字信号传输性能分析仪的应用前景越来越广阔,基于该技术的应用产品会有很大的发展空间,本系统采用MSP43F149作为主控处理器,完成了由信号发生器、伪随机信号生成器、滤波电路、控制显示部分组成,能够很好的实现对数字信号传输性能的测试功能,通过对该系统的整体性能测试,本设计能过满足实际应用的技术指标要求。

[1]童诗白,华成英.模拟电子技术基础[M].4版.北京:高等教育出版社,2001.

[2]曹磊.MSP430单片机C程序设计与实践[M].北京:北京航空航天大学出版社,2007.

[4]王前虹,债殿堂,成谢锋.电工电子一体化实验教程[M].北京:中国石油大学出版社,2008.

[5]王兆安,黄俊.电力电子技术[M].北京:机械工业出版社,2000.

[6]王毓银.数字电路逻辑设计[M].北京:高等教育出版社,2005.

[7]李朝青.单片机原理及接口技术[M].北京:北京航空航天大学出版社,2005.