TMR加固的SpaceWire节点的设计与实现

刘涛 贺强民 黄伟

(北京空间机电研究所,北京 100076)

1 引言

SpaceWire总线技术是欧空局推出的一种面向航天应用的高速差分串行总线技术。可以解决星上分系统间、设备间通讯数据总线带宽不足的问题,并且提供一种通用接口从而简化和规范不同设备之间的互连。该总线技术已成功地应用于欧空局的Mars Express和Smart-1等多个空间任务,协议的实现主要使用专用芯片。使用FPGA实现SpaceWire节点具有设计灵活、传输协议可根据项目特点进行裁剪、设计成本低、系统集成度高等优势[1-2]。

FPGA功能加固技术包括三模冗余(Triple Modular Redundancy,TMR)技术、定时刷新配置技术、动态重配置技术等,可以降低空间高能粒子辐射导致的单粒子效应(Single-event Effects,SEE)对FPGA逻辑功能的影响。TMR技术相对于其它FPGA功能加固技术,具有技术相对成熟和通用性强的优势。目前该技术已经成功应用于空间任务中,典型的技术就是Xilinx公司的XTMR技术[3]。

本文结合SpaceWire高速串行总线在传输机制上的高容错性和三模冗余设计在FPGA功能实现上的高容错性,在SpaceWire节点代码设计中对关键功能模块进行了软件辅助三模冗余设计和手动三模冗余设计,并在Xilinx公司FPGA上实现了TMR加固的SpaceWire节点与SpaceWire标准设备之间的高速数据传输。

2 SpaceWire节点的设计

SpaceWire节点设计应严格按照SpaceWire协议功能框架进行[4],如图1所示。

图1 SpaceWire协议节点的功能模块图Fig.1 SpaceWire link interface block diagram

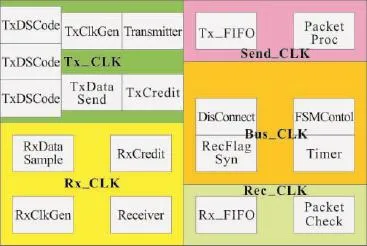

在SpaceWire节点的FPGA设计中,根据协议特点对软件功能模块和时序域进行划分[1,5]。如图2所示,图中不同功能模块工作在不同的时钟域(用颜色区分不同时钟域),其中数字滤波编码模块(TxDSCode模块)需要单独做三模冗余设计。

图2 SpaceWire节点设计的功能模块划分和时钟域划分Fig.2 SpaceWire link interface function and timing

3 TMR加固技术

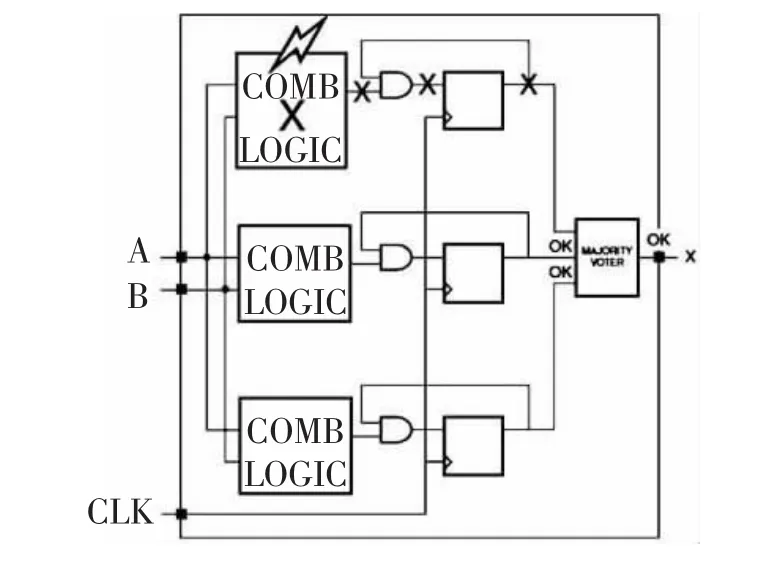

3.1 传统TMR设计

传统TMR设计方法将用户逻辑(组合逻辑加上寄存器)进行了复制处理,3个相同的模块接收3个相同的输入,产生的结果送至多数表决器,表决器的输出取决于3个输入。若有一个模块故障,则另两个正常模块的输出可将故障模块的输出屏蔽,表决器输出仍然正确,如图3所示。

图3 传统TMR电路的逻辑功能受到SEE影响Fig.3 Traditional TMR circuit logic function affected by SEE

图4 传统TMR电路的时钟受到SET影响Fig.4 Traditional TMR circuit clock affected by SET

虽然传统TMR设计方法可以在一定程度上减小电路受SEE影响而出错的概率,但仍存在如下不足:

1)若时钟线受到单粒子瞬态SET影响,可能导致输出错误,如图4所示;

2)若组合逻辑受SEU影响,由于电路没有提供寄存器错误恢复机制,会导致错误积累;

3)若多数表决器受SEU影响,将导致输出错误。

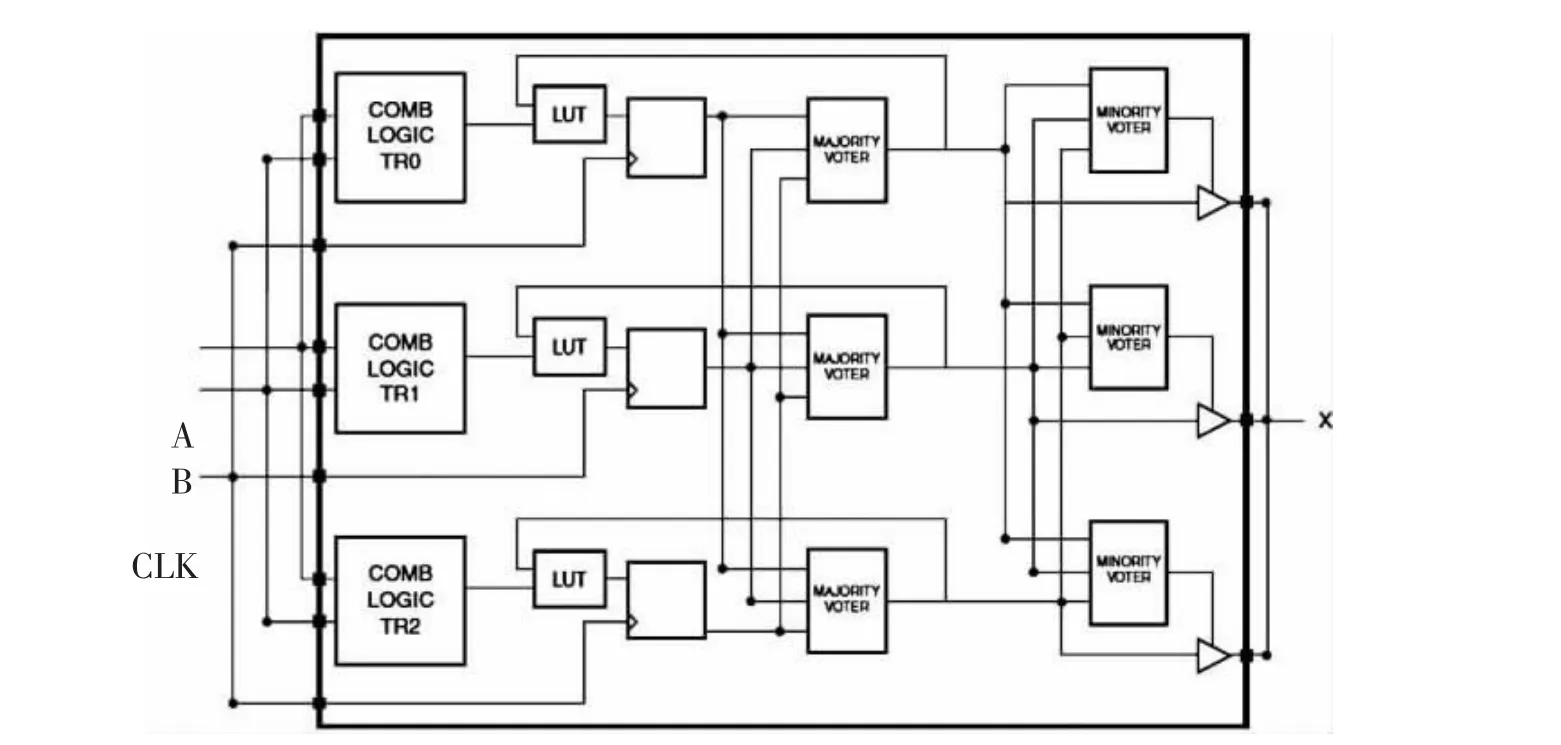

3.2 XTMR设计

XTMR是Xilinx公司的TMR设计软件,相比传统的TMR设计,XTMR方法从设计思路上进一步增加了FPGA功能的可靠性[6],XTMR电路结构如图5所示,其改进主要体现在3个方面:

1)三模时钟信号和输入信号。即使某一路时钟信号受到SET影响,仍能保证输出结果正确。

2)三模反馈逻辑和多数表决器。这样即使某一个表决器受SEU影响出错,仍能保证结果正确,并且多数选择器后添加了反馈回路,可以及时纠正由组合逻辑带来的寄存器错误。

3)三模输出信号并且增加少数表决器。输出端口添加了少数选择器,该选择器能够在本路输出与其它两路不同时,将本路输出三态门设置为高阻,这样就不影响正确结果输出。

图5 Xilinx TMR设计电路结构Fig.5 Circuit structure of the Xilinx TMR design

3.3 TMR的适用范围

在实际的FPGA设计中,不是所有的功能模块都适合做TMR。本文结合SpaceWire节点的特点对TMR适用性进行了如下分析。

1)模块功能失效时对系统功能影响大的优先做TMR。FPGA软件根据数据流的方向进行软件系统可靠性分析,不同功能模块的失效,对整个系统功能的影响不同。TMR设计应首先针对对系统功能影响大的模块。

2)是否适合做TMR。产生的时钟信号或还原的时钟信号不适合做TMR。时钟是整个时序逻辑的基础,时钟的产生或者时钟的还原本身会存在相位差[7],对FPGA的时序会造成较大的影响,不符合时序逻辑设计的原则。

3)TMR设计成本分析。TMR设计时,相应的模块资源会增加3倍以上,由于使用FPGA资源的增加,布局布线会更加困难,导致时序性能下降;另外,TMR需要的判断表决电路中存在大量组合电路,有可能会变成FPGA时序的关键路径,此时很难提高FPGA的时序性能。前期代码设计在提高时序性能上的努力也很难体现。

在SpaceWire节点设计时,发送端DS编码功能模块失效时,会产生发送编码错误。850ns链路断开检测功能模块失效时,会产生超时断开错误。这两个模块如果发生单粒子翻转事件,会导致链路断开复位,这需要经过约26μs的时间才能重新建立连接,导致等效的传输效率下降。综上所述,需对DS编码模块和链路断开功能检测模块进行三模冗余设计。

4 XTMR设计的SpaceWire节点

在SpaceWire节点设计时,对发送端DS编码模块进行辅助三模冗余设计。

本文采用XTMR软件的XTMRTool设计工具,分3步对M_TxDSCode模块进行TMR设计。

第一步:先将需要做三模的代码进行综合,生成网表文件SPW_RS232.ngc。

第二步:将网表文件SPW_RS232.ngc导入TMRTool进行TMR操作,TMR读取网表文件。首先,设置ISE软件中的层次化结构,并设置XTMR软件,锁定IO端口,设置需要进行三模冗余的模块。然后,当XTMR软件运行完成并产生新的网表文件,手动修改新的网表文件,删除新增加的IO端口,否则会与IO管脚约束文件产生冲突,编译时出现错误。

第三步:建立第二个ISE工程,编译XTMR产生的文件,增加三模冗余设计后,在Xilinx ISE Floop plannar下查看SpaceWire功能模块架构,打开M_TxDSCode模块,若该模块中相应的寄存器变成TR0,TR1,TR2,则表明已经成功做了三模冗余设计。

5 TMR设计在降低亚稳态导致系统功能错误中的应用

目前FPGA功能设计中,TMR大多用在抗单粒子翻转的设计中,广义上讲,TMR设计的思想是降低目标部件发生错误对系统功能造成的影响,所以三模冗余设计也可以应用在降低亚稳态导致系统功能错误的设计中。

在多时钟域设计中,亚稳态是常见的问题,一般使用双采样降低亚稳态产生的概率,但是仍然有一定概率会产生亚稳态。当产生亚稳态时,最差情况下,需要经过几个甚至更多个时钟周期,寄存器输出才能稳定在“0”或者“1”。 本文尝试使用TMR设计来降低亚稳态的产生对系统逻辑功能造成的影响。

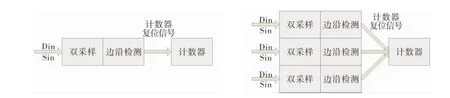

SpaceWire协议有链路断开检测功能,当850ns内Din和Sin信号都没有变化时(即没有发生高低电平的变化),会产生内部报错。输入信号与本地时钟为异步信号,存在产生亚稳态的可能。常规的设计方法是使用本地时钟同步两次输入信号,然后进行边沿检测,边沿检测原理为判断相隔几个时钟周期的采样信号是否相等。当检测到边沿信号时,清空复位计数器,如果在一定时间内没有检测到边沿信号,计数器则会达到预设值,产生链路断开连接错误信号。电路原理如图6左侧所示。

图6 常规设计与三模冗余设计Fig.6 Conventional design and triple modular redundancy design

实际使用ChipScope采样数据时,发现Din或者Sin信号电平发生变化,但是计数器并没有清零仍然继续计数的现象,如图7所示。笔者认为是本地时钟同步输入信号时产生了亚稳态,导致边沿检测电路失效,没有对计数器复位,使计数器达到预设值而产生错误报警信号。

图7 Din和Sin信号电平发送变化,边沿检测失效Fig.7 Din and Sin signal level sent changes in the edge detection failure

本文对双采样电路和边沿检测电路进行三模冗余设计[5],只要有一个检测到边沿的生效,即可以驱动计数器清零复位,如图6右侧所示,这种设计方案降低了亚稳态导致边沿检测失效的可能性。亚稳态的产生是以概率来衡量的,即使经过本地时钟同步的信号,仍然存在产生亚稳态的风险,只是概率会减小很多。对边沿检测模块进行TMR设计,可以进一步降低亚稳态的产生对系统功能造成的影响。

6 TMR加固的SpaceWire节点的实现

本文对TMR加固后的SpaceWire节点进行了测试,测试系统由FPGA电路板和DunDee大学的SpaceWire标准设备组成。

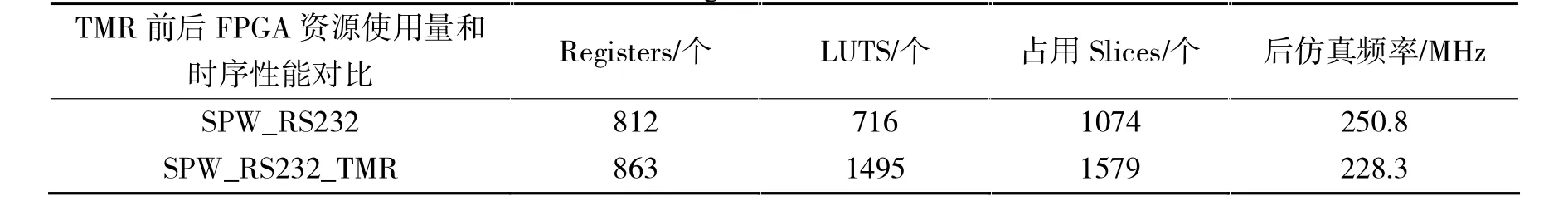

SpaceWire节点在使用TMR设计前后所占用FPGA资源的变化如表1所示。可以看到在进行TMR设计前后,FPGA资源变化很大,尤其是LUT的资源,几乎增加了一倍,这是由于TMR设计时,在发送端DS编码模块时使用了3个多数表决器和3个少数表决器,导致组合逻辑资源增加。相应的FPGA布局布线难度增加及关键信号路径延迟的增加,导致FPGA时序性能有所降低。因为使用双沿采样(ODDR)发送[8],所以理论上发送端速率仍然高达450Mbit/s,但是受器件IO端口最高频率的限制以及PCB布线EMI的影响,实际测试时,FPGA运行在100MHz,对应200Mbit/s的传输速率。测试中使用ChipScope截图与图7相似,未另行截图。

表1 TMR操作前后FPGA资源使用Tab.1 FPGA resource usage between used TMR and unused TMR

7 结束语

本文同时使用SpaceWire总线和TMR加固设计,结合SpaceWire总线在传输机制上的高容错性和三模冗余设计在FPGA功能实现上的高可靠性,对SpaceWire节点设计中的关键功能模块进行XTMR软件辅助三模冗余设计和手动三模冗余设计。目前,国内尚无公开文献报道TMR加固的SpaceWire节点与SpaceWire标准设备之间的数据传输。本文使用TMR设计,在降低亚稳态导致系统功能错误方面做了有益的尝试。

(References)

[1]刘涛,黄伟,潘卫军.SpaceWire软核的设计与验证[J].航天返回与遥感,2011,32(1):51-58.

LIU Tao,HUANG Wei,PAN Weijun.Design and Verification of SpaceWire IP Core[J].Spacecraft Recovery&Remote Sensing,2011,32(1): 51-58.(in Chinese)

[2]Ponomarev S A.SpaceWire In Prospective Space Systems and International Collaboration[C].SpaceWire-2010 Proceedings of the 3rd International SpaceWire Conference,Petersburg,2010.

[3]Xilinx.Triple Module Redundancy Design Techniques for Virtex FPGAs[EB/OL].//www.Xilinx.com.

[4]European Cooperation for Space Standardization,ECSS-E-50-ST-12C SpaceWire-links,Nodes,Routers and Networks[S].Issue2,European Cooperation for Space Standardization,2008.

[5]Masaharu Nomachi.Race Condition Free SpaceWire Decoder For FPGA[C].SpaceWire-2010 Proceedings of the 3rd International SpaceWire Conference,Petersburg,2010.

[6]Xilinx.TMRToolUser Guide,Version9.2i[EB/OL].//www.Xilinx.com.

[7]Actel.Implementation of the SpaceWire Clock Recovery Logic in Actel RTAX-S Devices[EB/OL].//www.actel.com

[8]Xilinx.Virtex-5 User Guide[EB/OL].//www.Xilinx.com.