基于DSP与FPGA的运动控制器研究

周国娟,金红莉,苏福根

(1.北京经济管理职业学院 北京 102602;2.北京邮电大学 世纪学院,北京 102613)

运动控制即通过电机驱动的执行机构对电机的转速、转矩以及转角等加以控制,以使执行机构按照预定轨迹运动。运动控制技术是机器人、数控机床和生产加工自动化等领域的关键技术,是一门融电子、计算机、控制和传感器等多学科于一身的交叉技术。运动控制技术发展水平的高低标志着一个国家工业现代化水平的高低。运动控制技术在我国的发展大致经历了基于大规模集成电路、基于单片微处理器、基于专用集成电路 ASIC(Application Specific Integrated Circuit)以及基于数字信号处理器(DSP)芯片几个阶段。笔者介绍一种基于DSP和现场可编程门阵列(FPGA)的运动控制器,该控制器充分发挥了DSP运算速度快、兼容性好的优势,也利用了FPGA的高速并行处理的能力,具有信息处理能力强、模块化程度高、编程容易、运动控制精度高等优点。

1 整体方案介绍

文中设计的运动控制系统基于TI公司的DSP芯片TMS320F2812和ALTERA公司的FPGA芯片EP2C8Q208C。在本控制器中,DSP因为有着强大的信号处理能力和很高的运算速度,主要用来完成多自由度静态运动轨迹的计算或者运动轨迹的动态规划以及运动控制算法的实现。同时,DSP还可以通过PCI总线和PC机通信,以获取控制参数。FPGA因为有着丰富的内部资源,高效的底层数据计算处理能力,且可以实现并行操作,因此用FPGA实现与各传感器和电机驱动器的接口,以及模拟各种专用电路或芯片,如模拟QEP编码采样电路对编码器信号进行解码计数,或者实现步进电机的脉冲发生等。此外,FPGA内部有着丰富的RAM资源,可以用来存储需要实时处理的大量数据资源。

一般的运动控制器多用来通过电机驱动器驱动步进电机、直流或交流电机等原动机,所以需要有相应的脉冲信号输出和模拟量信号输出功能,其中脉冲信号输出可以由FPGA在DSP的指令下,输出PWM波,也可以由TMS320F 2812自带的12路PWM专用发生电路发出;模拟信号则由挂在FPGA上的D/A芯片在发出。为了采集系统中传感器的反馈和控制信号,控制器还应该具有采集编码器的差分编码信号、以及进行A/D采样的功能,这些接口和底层数据的处理都由FPGA实现,FPGA只把包含位姿信息的最终结果发送给DSP进行相应的处理。

此外,该控制器还应该包含有大量普通的输入输出端口,用来控制继电器或者采集行程开关等开关量的输入信号或者用来控制电机转向,电磁阀开关等。图1为系统总体框图。

图1 系统总体框图Fig.1 System block diagram

2 具体模块设计

2.1 DSP模块设计

TMS320F2812是一块专门用于电机运动控制的高性能的数字信号处理芯片,其内部具有一个32位的硬件乘法器,可以在一个周期内完成两个32位数据的乘法,对于乘除法的计算效率远高于其他普通单片机。其核心电压仅为1.8 V,I/O口输入输出标准电压3.3 V,功耗很低。通过倍频技术主频最高可达150 MHz,且片内含有128 K×16 b的片内FLASH供编程使用。

DSP的重要功能之一是与上位机进行通讯,接收上位机的运动轨迹数据及其他指令,并将传感器的信号值反馈给上位机。DSP与上位机通讯可以根据需要选择串口通讯方式、CAN总线通讯方式、PCI总线通讯方式等多种方式。其中以PCI总线方式的抗干扰能力最强,速度最快。TMS320F2812芯片自带有CAN总线模块,只需要配置响应的CAN总线收发器即可实现通讯。在本设计中,DSP通过以太网控制器RTL8019AS与上位机通讯。RTL8019AS包含一个16 kB的SDRAM,DSP可将其视为自己的外部存储器,对其进行相应的读写就完成了与上位机的数据交换。

直流伺服电机的驱动多要求带有死区的占空比可调的PWM信号,TMS320F2812内部有两个事件管理器,可以直接控制输出12路PWM信号。用户可通过设定PWM控制寄存器来设定PWM波的产生模式、占空比及死区时间。与传统的用定时器中断来产生PWM波的方式相比,通过事件管理器定时器硬件来产生PWM波不仅大大降低了编程的复杂性,也解放了宝贵的CPU资源,大幅度提升了该芯片应用于电机控制时的性能。

通常情况下,运动控制系统需要完成位置环与速度环的双闭环控制,进行实时的PID计算与调节,还需要根据上位机的参数实时规划运动路径、速度等。这些任务自然都是交给拥有强大计算处理能力的DSP来完成的,而完成这些任务需要大量的程序存储空间和数据存储空间,尽管TMS320F2812内部含有 18 K×16 b的 SARAM以及 128 K×16 b的FLASH,但依然显得过小,因此为了提升系统性能,充分发挥DSP的优势,本系统为DSP外扩了128 K×16 b的RAM和512 K×16 b的FLASH。

2.2 FPGA模块设计

与DSP相比,FPGA在大数据量的底层数据并行处理上有明显优势,且实时性好,而DSP的优势主要体现在复杂算法和浮点数运算上[1]。FPGA内部逻辑单元可以自由编程,使用非常灵活,可以编程模拟各种专用信号处理芯片,以及进行信号采集后数据的初步处理。例如,可以用FPGA模拟DSP的QEP正交编码电路,同时对多个编码器的输出脉冲进行计数,并通过编码器的返回值计算当前的姿态和位置,只在规定的时间将当前的姿态和位置信息反馈给DSP,从而大幅度的减少了DSP处理底层数据的工作量。

FPGA主要用来实现运动控制器的各种接口,以扩展DSP的普通I/O口数量,并对采集的信号进行初步的处理。在本系统中,FPGA负责对编码器的反馈信号进行采集分析,控制A/D转换器对模拟量输出的传感器进行信号采集,并将计算出的位姿信息传输给DSP。接受DSP的信号,输出相应的开关量或者控制相应的D/A转换器输出模拟量电压值。FPGA的选用应考虑逻辑单元的数量、I/O口的数量是否够用,与DSP的接口是否容易等,同时应该考虑开发成本,不能一味的追求逻辑单元多、I/O口数量多的型号而造成浪费。考虑本设计中的应用,选用Altera公司的CycloneⅡ系列的EP2C8Q208C8芯片。该芯片有138个I/O口和8256个逻辑单元,且I/O口电平与所选DSP芯片兼容,均为3.3 V,链接方便。该FPGA内核采用1.2 V供电,具有低功耗的特点。

2.3 PCI总线模块设计

DSP通过以太网控制器RTL8019AS与上位机相连,RTL8019AS除了含有通讯内核外还含有16 kB的SDRAM,它和主机的接口有跳线模式、PnP模式和RT模式,接口复合Ethernet2和IEEE802.3标准。在本设计中,为了便于DSP的应用,采用跳线的模式。连接时,DSP的16位数据总线与RTL8019AS的数据总线直接相连即可。RTL8019AS的片内寄存器是通过其映射I/O口进行访问的,实际连接时,如图2所示,只需将SA0~SA9与DSP地址线相连,而SA10~SA19可直接接低电平[2]。

图2 RTL8019AS与DSP接口Fig.2 Interface between RTL8019AS and DSP

RTL8019AS可以使用双绞线作为传输介质,为了消除因电路数字特性导致的高次谐波,可通过20F001N双绞线驱动器发送信号,20F001N为耦合隔离变压器模块。RTL8019AS与20F001N的连接如图2所示。

2.4 DSP与FPGA接口设计

DSP与FPGA的接口有很多种实现方式,为了实现高速的数据交换,保障DSP与FPGA通讯的实时性,可以在FPGA内部模拟一个双口的RAM,这样DSP只需要将FPGA作为自己的一个外部存储器,在相应的外部地址内进行数据的读写,就可以实现与FPGA的数据交换。这样虽然可以保障数据通讯的速度,但是占用了大量的I/O口,而在本设计中,FPGA已经完成的大部分数据的底层处理,DSP只需要每隔一段时间读取一下FPGA反馈回来的数据信息即可,需要传输的数据量并不大,实时性要求也不是非常高。因此采用SPI总线实现DSP与FPGA的通信即可,这样即节省了并行数据通讯需要占用的大量I/O口资源,也使得层次结构更为清晰,编程更加方便[3-4]。这需要将DSP芯片上的多通道缓冲串口配置为SPI主机模式,而FPGA中采用NIOS核可以实现SPI模块的模拟,应将FPGA模拟的SPI模块设置为从机模式。

2.5 A/D,D/A模块介绍

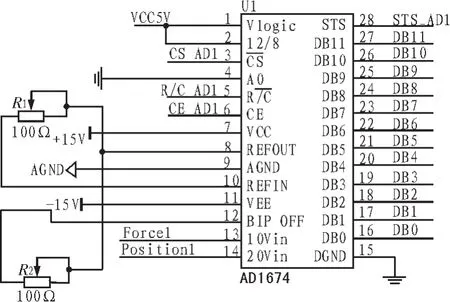

对于高精度的伺服控制系统而言,传感器输出信号的采样精度直接决定了最后系统的控制精度。在高精度、高速度、高采样范围、高抗干扰性的要求下,DSP自带只能对0~3 V信号采样的12位A/D传感器已经无法满足要求。为此,我们额外扩展了2片AD1674专门用来进行A/D采样。AD1674是AD公司推出的一种12位带并行接口的逐次逼近型模/数转换芯片,可以对-10~+10 V信号进行采样。采样频率可达100 kHz,转换时间为 10 μs,满量程校准误差[5]仅为 0.125%。图3为AD1674接线图,其中REF IN管脚接基准输入电压,通常可以将内部的10 V基准电压接50 Ω电阻后接在这个管脚上;BIP OFF管脚为双极电压偏移量调整端,在双极输入时可以通过50 Ω电阻接在REF OUT端,若只是单级输入,则可将其接模拟地。

图3 AD1674接线图Fig.3 Wiring diagram of AD1674

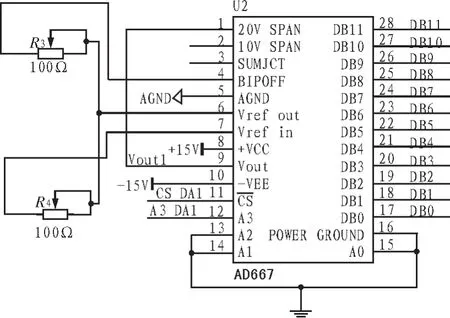

模拟信号输出电路同样采用AD公司的D/A转换器AD667,它是具有2级缓冲器的12位D/A转换芯片,功耗300 mW,建立时间只有3 μs。为了实现多电机的同步控制,可以将多路D/A芯片的控制信号连接与LDAC连接在一起,这样当所有的D/A芯片数据全部装载完毕后,在同时打开控制信号,即可完成多路驱动的同时控制。图4为AD667用于双极输出时的接线图,其接线方法与AD1674基本相同,REF IN管脚与BIP OFF管脚含义也与AD1674相同[6]。

图4 AD667接线图Fig.4 Wiring diagram of AD667

2.6 电源模块设计

该运动控制器采用+5 V供电,而控制器实际需要的各种电压值需要在内部进行相应转化得到。控制器需要的电压主要有 3.3 V、1.8 V、1.2 V、±5 V 和±15 V。 其中的 3.3 V、1.8 V和1.2 V电压可由线性稳压模块稳压得到,主要用于给DSP和FPGA供电[7-8]。应该注意到,TMS320F2812有上电顺序要求,3.3 V电压应先于1.8 V内核电压上电,因此1.8 V电压必须由3.3 V电压稳压得到,并在1.8 V电压与数字地之间上加10电容,以保证上电顺序。AD667和AD1674芯片要求±15 V的模拟电压,该电压可由开关稳压得到,本设计中选用开关电源MC34063。在运行过程中,高频的数字信号会对模拟信号产生较大的干扰,为了增强系统的抗干扰能力,应该对给数字电路供电的5 V和给模拟电路供电的5 V用DC/DC隔离后,在进行相应的电压变换。

3 结束语

随着机器人技术、多自由度伺服运动控制技术等机电一体化技术的不断发展,机械系统对于运动轨迹、运动速度的控制要求越来越高,迫切的需要高性能的运动控制器。而随着模糊PID算法、神经网络算法,以及动态路径规划算法等复杂算法的应用,也对运动控制器的计算能力和数据处理能力提出了越来越高的要求。同时,随着机械系统复杂性的不断增加,在系统中往往含有大量的传感器,需要进行大量的数据采集、底层数据处理,这就要求运动控制器有着丰富的I/O资源和强大的并行处理能力,能够同时处理多组数据,保证系统的实时性。DSP+FPGA的体系结构恰恰可以满足高性能运动控制器的所有要求,DSP有着强大的数据处理能力,可以进行复杂的控制运算;FPGA有着丰富的I/O资源和强大的并行处理能力,可以作为各种外部资源与主控芯片的接口和专用信号处理电路。FPGA的应用使得系统的灵活性和适应性大幅度的提升,也减少了DSP在多任务切换时无谓的运算资源消耗。该控制器充分利用的DSP和FPGA各自的优点,整个控制器性能指标高、抗干扰能力强、功耗低、结构紧凑合理。

[1]季振洲,周勇林,胡铭曾.FPGA芯片设计效率的研究[J].高技术通讯,2000(5):71-73.JI Zhen-zhou,Zhou Yong-lin,Hu Ming-zeng.Research on FPGA chip design efficiency[J].Hich Technology Letters,2000(5):71-73.

[2]夏辉,车国轮.基于DSP的导航计算机设计[J].微处理机,2006(2):55-57.XIA Hui,CHE Guo-lun.Design of navigation computer based on DSP[J].Microprocessors,2006(2):55-57.

[3]刘永锋.基于DSP和FPGA的机器人运动控制系统的研究[D].南京:南京理工大学,2007.

[4]朱军,高清维,韩璐.基于DSP和FPGA的数据通信实现方案[J].电子测量技术,2009(1):102-104.ZHU Jun,GAO Qing-wei,HAN Lu.Solution of data communication based on DSP and FPGA[J].Electronic Measurement Technology,2009(1):A102-104.

[5]邱云周.基于DSP和FPGA的运动控制技术的研究 [D].四川:四川大学,2004.

[6]石江华.基于DSP与FPGA的四轴运动控制器设计与研究[J].现代电子技术,2011(21):202-204.SHI Jiang-hua.Design and research on four-axis motion controller based on DSP and FPGA[J].Modern Electronics Technique,2011(21):202-204.

[7]白峻.基于FPGA和多DSP的多总线并行处理器设计[J].计算机测量与控制,2012(1):173-176.BAI Jun.A multi-bus parallel processor based on FPGA and multi-DSP[J].Computer Measurement&Control,2012 (1):173-176.

[8]关宗安.基于TMS320F2812 DSP的网络通信系统设计[J].电子技术应用,2009(3):94-96.GUAN Zong.The design of network communication system based on TMS320F2812 DSP[J].Application of Electronic Technique,2009(3):94-96.