小型雷达环境模拟器双波段快速跳频模块设计*

高建栋,韩壮志,何 强,郭宝锋

(军械工程学院,河北 石家庄050003)

实现RES的关键是实时生成与雷达状态相匹配的综合回波信号。其中,难点是在便携式条件下实现多波段脉间捷变频雷达的信号实时模拟。一方面要求具有雷达状态获取、传输,且信号处理部分具备高速处理的能力;另一方面要求射频模块具备多波段宽带快速跳频的能力。因此,射频模块性能的好坏将直接影响RES的性能。

高性价比多波段宽带快速跳频模块的设计是当前微波模块设计的热点之一[9],本文采用 DDS+倍频链技术,实现了输出射频信号在C、X波段的频率跳变。其频带较宽、跳频速度快、杂散低、相噪低、频率分辨率高,并且输出功率可调,确保了RES系统的实现。

1 设计方案

1.1 设计指标

设计指标有:(1)工作频段:C波段、X波段;(2)相对带宽:10%;(3)频率分辨率:小于 10 Hz;(4)跳频时间:小于 5 μs;(5)输出杂散抑制:优于-50 dBc;(6)相位噪声 :优于-70 dBc/Hz@10 kHz;(7)输出功率:可控,步进精度为0.5 dBm。

1.2 方案设计

宽带微波频率源主要有以下几种实现方式:直接数字频率合成(DDS)、锁相环(PLL)、DDS激励 PLL或倍频器[10]。DDS技术具有频率分辨率高、频率切换快、频率稳定度高等优点,但是输出信号频率较低、带宽有限;PLL技术输出频谱纯度高,但其频率转变时间较长,频率分辨率也有限。通常会考虑把DDS和PLL组合在一起应用,但DDS和PLL结合的主要缺点是频率转换时间较长。虽然DDS本身的频率转换时间很快(可达ns级),但其输出频率低,杂散多,所以要依靠PLL实现倍频和跟踪滤波,而PLL在跟踪频率时需要一定的捕获时间,这个时间与环路的类型、参数和频率步进等有关,而DDS+PLL频率合成的转换时间取决于PLL,这就相当于牺牲了DDS频率转换时间快的优点换取高输出频率和纯净的频谱。

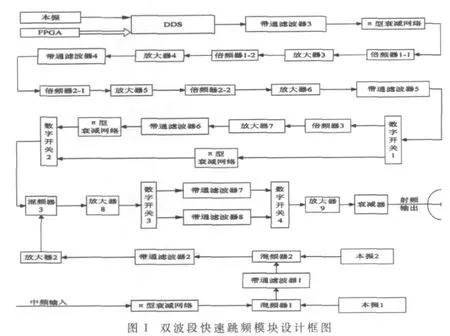

因此本设计中,使用倍频器代替PLL,可以克服DDS+PLL频率合成器转换时间较长的缺点。采用“DDS+倍频链”的设计方案,以DDS作为频率合成的核心,用倍频链提高DDS的输出频率,同时拓展了DDS的输出带宽,容易满足系统设计的要求。尽管倍频会使输出产生非线性失真和杂散,若合理选择DDS直接输出的频段,利用带通滤波器可有效地抑制DDS的杂散输出,可以保证频率合成器在输出频率高速切换的同时满足输出频谱纯度的要求。双波段快速跳频模块设计框图如图1所示。

该模块工作过程为:DDS在FPGA的时序控制下,产生窄带信号,经DDS倍频链后满足带宽要求;输入的中频模拟信号经两次混频后分别与DDS输出的16次倍频和32次倍频后的信号混频,实现C波段和X波段射频输出的要求,通过开关选通电路实现C波段和X波段之间的切换。输出端接一个6 bit数字衰减器,用于控制射频输出功率的大小。在实现设计指标的前提下,如何提高输出信号的频谱纯度是本方案实现的难点。

1.3 主要器件选择

该系统主要由DDS、倍频链、数字开关、FPGA、本振源及带通滤波器组成。DDS芯片采用Analog Device公司的产品AD9912;倍频链由功分、放大、混频、倍频等部分组成,将DDS输出信号实现输出频率的倍频,以供数字开关选择输出;数字开关采用Hittite公司的HMC232LP4开关,开关时间为 6 ns,是一款宽带、高隔离、无反射砷化镓场效应晶体管双路选择开关,可以实现频率快速跳变;FPGA芯片采用美国Altera公司的CycloneII系列EP2C5T144C8,其功能强大,性价比较高;本振源选用SYNERGY微波公司的LFSW2476-10和LFSW190410-100芯片,本振源的选取会直接影响射频输出的相位噪声指标及杂散抑制能力;低频段的带通滤波器设计采用LC滤波器,高频段的滤波器设计采用平行耦合微带带通滤波器,对带外杂散的抑制均大于30 dB,带内纹波小于0.5 dB,输入、输出阻抗均为 50 Ω。

这种运营的模式指的是,企业直接去找专业的能配送生鲜的物流企业进行合作,这种模式一方面可以使服务更加专业、有利于社会的相关资源分配、发挥经营规模大的、为企业节约其余物流开支;另一方面我们也要看到它的弊端就是前期的投入大,相关设备价格昂贵,并且缺乏专业人才与行业相关标准。例如订单为200元,第三方的物流就会产生80或100元的费用,成本较高。

1.4 方案实现

1.4.1 低杂散设计

该模块的杂散主要来源于DDS杂散及混频后的交互调分量[11]。产生DDS杂散的主要原因为相位截断误差、幅度量化误差和DAC非线性误差,所以DDS芯片和混频器的选择尤为重要。本设计中,DDS芯片选用具有杂散抑制通道的AD9912芯片,其突出特点是拥有能够编程的辅助直接数字频率合成器通道,可以降低输出频谱中问题谐波杂散的等级,改进了DDS固有的杂散和噪声大等缺点。本方案中,DDS所选频段杂散抑制为-61 dBc。

根据频率范围的需要,混频器选择性价比和隔离度均较高的器件,最后通过滤波器可以滤除混频后的交互调分量,保证低杂散的实现。同时,由于该模块工作频率较高,必须做好电磁兼容性设计。

1.4.2 跳频时间设计

跳频时间主要由数据配置时间、DDS芯片响应时间和PIN开关切换时间构成[12]。本设计中所用DDS芯片为AD9912,该芯片只能采用串口模式进行配置。AD9912需要配置的频率控制字的位数为 48 bit,指令控制字位数为 16 bit,所以 FPGA和DDS的串行通信发送的数据总共为64 bit。经计算,FPGA工作在50 MHz主频时,完成64 bit的数据配置所需时间为 2.56 μs,并且由芯片数据手册可知,DDS芯片响应时间小于 1 μs,PIN开关切换实际测试时间小于 1 μs,且 DDS芯片响应时间和 PIN开关切换时间可在同一时段完成,所以总时间可满足系统跳频时间小于 5 μs的要求。

1.4.3 低相噪设计

通过分析AD9912的数据手册给出的测试数据可以看出,在不使用内部PLL乘法器时,其相位噪声优于-130 dBc/Hz@10 kHz。AD9912的850 MHz时钟信号采用锁相方案,对相位噪声有影响的器件主要是鉴相器和参考时钟。鉴相器采用ADI公司的ADF4106芯片,其归一化噪声基底为-219 dBc/Hz@10 kHz,当鉴相频率等于25 MHz时,环路分频比 N为 850/25=34,则带内总的相位噪声为-114.4 dBc/Hz。此外,考虑到 PLL参考时钟也会对相位噪声产生较大的影响,系统采用输出频率为100 MHz的晶振,其相位噪声为-145 dBc/Hz@10 kHz,它对输出相位噪声的影响为-126.4 dBc/Hz。综上所述,850 MHz时钟信号的输出相噪为-114.4 dBc/Hz@10 kHz,这是DDS总相位噪声。经32倍频后输出的相位噪声恶化20lg32 dB(即30 dB),混频器3的RF输入端相噪为-84.4 dBc/Hz@10 kHz。 本振源 1和本振源 2选用SYNERGY微波公司的频综LFSW2476-10和LFSW190410-100,其相位噪声分别为-100 dBc/Hz@10 kHz和-85dBc/Hz@10 kHz,混频后的相位噪声按较差的计算,取-85 dBc/Hz@10 kHz,该信号在混频器3中与DDS倍频后的信号混频。由于RF和LO端口输入相噪相差不大,因此输出相噪恶化 3 dB(即-82 dBc/Hz@10 kHz),优于-70 dBc/Hz@10 kHz,满足系统设计对相位噪声的指标要求。

1.4.4 电磁兼容设计

电磁兼容性对系统的相位噪声、杂散等重要指标有很大的影响,如果设计不当,则会致使指标很难满足设计要求。因此,为保证系统工作性能,需要采取措施减少或抑制外来干扰噪声,降低附加噪声和系统自身信号串扰。具体措施如下:

(1)做好屏蔽措施。屏蔽不仅对辐射干扰有良好的抑制效果,而且对静电干扰和干扰的电容性耦合、电感性耦合均有明显的抑制性作用。本设计选用铝合金材料制作屏蔽盒,将分好块的电路分别放入各屏蔽盒中,把盖盖好并用螺钉紧固。各个屏蔽盒之间的高频信号用SMA接头引出,通过同轴线连接,可有效防止外界干扰进入屏蔽盒。

(2)做好接地和PCB布线。模拟电路部分和数字电路部分要分开,以避免模拟电路、数字电路和电源公共回线产生公共阻抗的耦合。对于差分传输的信号,应遵循等长等距原则。

1.4.5 电路设计调试

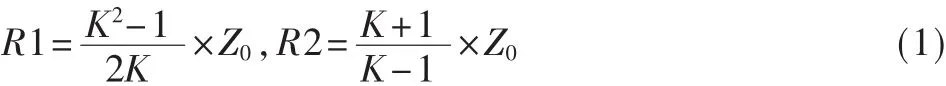

π型衰减网络通过电压来控制射频信号的功率,对电路起到衰减和匹配作用。由于倍频器、混频器等微波器件对射频输入都有功率方面的要求,所以π型衰减网络在射频以及微波网络方面有很广泛的应用。π型衰减网络的基本结构如图2所示,该网络由3个电阻组成,且两边的并联电阻相等。

其计算公式为:衰减值 β=20lgK dB,计算出 K值后代入式(1)计算电阻值:

图2 π型衰减网络的基本结构

其中Z0为特性阻抗。射频设计中,只需根据衰减值和特性阻抗大小,选择适当的电阻,即可很方便地完成信号的衰减和阻抗的匹配。

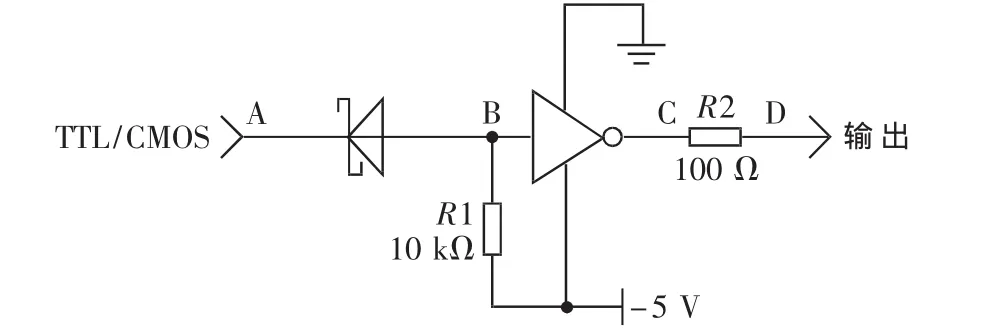

在射频输出端设计数字衰减电路,可以通过FPGA很方便地实现射频输出功率的变化。数字衰减器HMC424LP3采用-5 V电压 Vee供电,6 bit控制位的控制信号电平为0~-5 V,当输入控制信号电平在0~-3 V时为逻辑低、Vee~Vee+0.8 V时为逻辑高,而 FPGA的 I/O引脚输出为 0~3.3 V的 TTL/CMOS电压,因此欲实现 FPGA对数字衰减器的控制,必须设计控制信号的驱动转换电路,如图3所示。

图3 控制线的驱动转换电路

2实验结果与分析

若参考时钟频率不变,DDS的频率分辨率只由相位累加器的位数决定。DDS的输出频率分辨率为频率控制字为1时DDS的输出频率。本文参考时钟为850 MHz,输出分辨率为 f=(1×850×106)/232=0.197 Hz。将 DDS 的输出32 倍频后,频率合成器的分辨率为 f=0.197×32=6.33 Hz,满足指标要求。

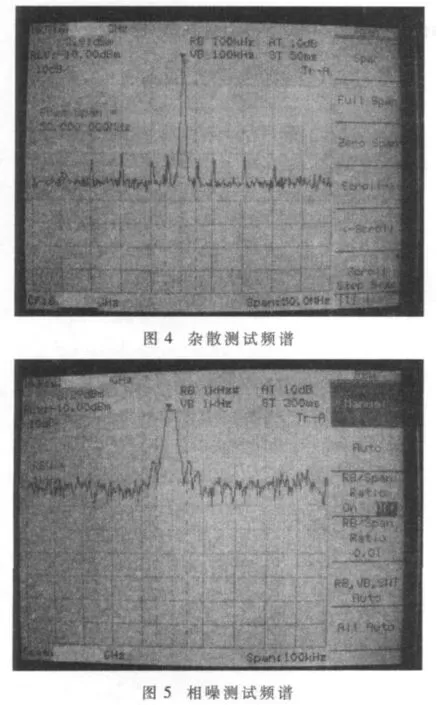

分别从C波段和X波段选取一个频点,采用Anritsu系列频谱分析仪MS2668C测试杂散,C波段的杂散抑制为-57.3 dBc,X 波段的杂散抑制为-52.8 dBc,验证了输出杂散抑制优于-50 dBc。同时C波段和X波段的相噪在-75 dBc/Hz@10 kHz附近,该结果与理论值相近,均优于-70 dBc/Hz@10 kHz,满足设计指标要求。从C波段取一频点,测试杂散及相噪结果分别如图4和图5所示,从图中可看出系统满足指标要求。

通过实际电路验证,本设计的双波段快速跳频系统达到了设计要求,跳频速度快、频带宽、杂散低、相噪低、频率分辨率高,便于数字控制且结构简单。同时,该系统体积小,成本低,易于生产实现,可广泛应用于部队雷达的抗干扰训练和检测。

[1]钱可伟,唐伟,徐自强,等.毫米波雷达信号模拟器研制[J].现代雷达,2011,33(1):18-21.

[2]向道朴,黎向阳,孟宪海.一种通用雷达回波模拟器的设计与实现[J].现代雷达,2007,29(10):84-90.

[3]Intersoft Electronics.Radar target generator RTG 698[Z],2010.

[4]杨鸿鹄,许蕴山,夏海宝,等.基于FPGA+DSP的雷达回波发生器设计[J].电子技术应用,2009,35(12):57-60.

[5]马浩.一种雷达回波实时仿真的软件实现方法研究[J].计算机工程与应用,2011,47(23):143-146.

[6]王胜,石志广,范红旗.基于目标电磁散射特征的雷达回波信号实时模拟系统的研制[J].电路与系统学报,2009,14(4):124-130.

[7]GEORGE L B,PhD,DAVID M H.A-irborne Radar Desktop trainer[EB/OL].Camber C-orporation[2012-06-26].http://cambertx.com/resources.php.

[8]赵菲,王生水,柴舜连,等.辐射式雷达目标模拟器射频前端设计与集成[J].国防科技大学学报,2010,32(3):109-114.

[9]邓茜,梁小朋.高性价比小型C波段宽带跳频源的研制[J].压电与声光,2011,33(3):432-435.

[10]黄超,任丽香,毛二可,等.一种X波段宽带快速跳频频率源[J].北京理工大学学报,2011,31(4):467-471.

[11]刘永智,鲍景富,高树廷.一种S频段高性能频率合成器的设计与实现[J].电讯技术,2011,51(1):89-92.

[12]刘永智,徐盛旺,高树廷.超宽带频率合成器的设计与实现[J].电讯技术,2009,49(12):88-90.