基于ARM和FPGA的高扩展性超声检测模块设计与实现*

孙鑫明 ,苗长云 ,白 华 ,杨彦利 ,刘 阳

(1.天津工业大学,天津300387;2.天津市中环系统工程有限责任公司,天津300040)

超声检测技术近年来取得了长足的进步,正在向检测自动化、分析智能化、多通道等方向快速发展,并在电力、航空航天、石化、军事、工业制造、医疗等领域被广泛应用[1]。在超声检测中,超声信号采集系统与上位机的数据通信主要有两种方式:PCI总线传输方式和以太网方式。目前的应用以PCI传输方式为主,该方式简便高效,但在远距离传输方面受到限制。而运用以太网方式更适用于需要远距离数据传输、检测信息互联网共享、在线监测的场合[2]。目前国外已开发出基于以太网传输的多通道超声采集系统,但价格昂贵,且购置前需要进行特殊定制。而国内在这方面尚未发现有成熟的产品面世。因此,对以太网接口的多路超声检测器模块的研究有着重要的实际意义。

1 基本功能和整体方案

1.1 基本功能

本系统以小型化和数字化为研究目标,实现系统模块化设计。系统设计的基本功能是制作一套4通道超声检测模块,在模块内部每一个通道可独立工作,包括单路超声探头的高压脉冲激励、信号的隔离限幅。同时,4个通道的超声回波信号经过带通滤波、信号放大、A/D转换后以并行的方式同时进入数据处理单元。其优点是:(1)提高了模块的集成度,减少了元件数目,大大减小了模块的尺寸大小,方便以后的硬件扩展;(2)提高了数据吞吐率。把整个系统的最小采集模块设计成4通道,以便在有大量通道时,系统将可按照4通道为一个单位将所有的通道轮询一遍,从而使得系统采集超声回波信号的时间比单路选通的时间缩短4倍,使系统的数据吞吐率大大增加。

1.2 整体方案

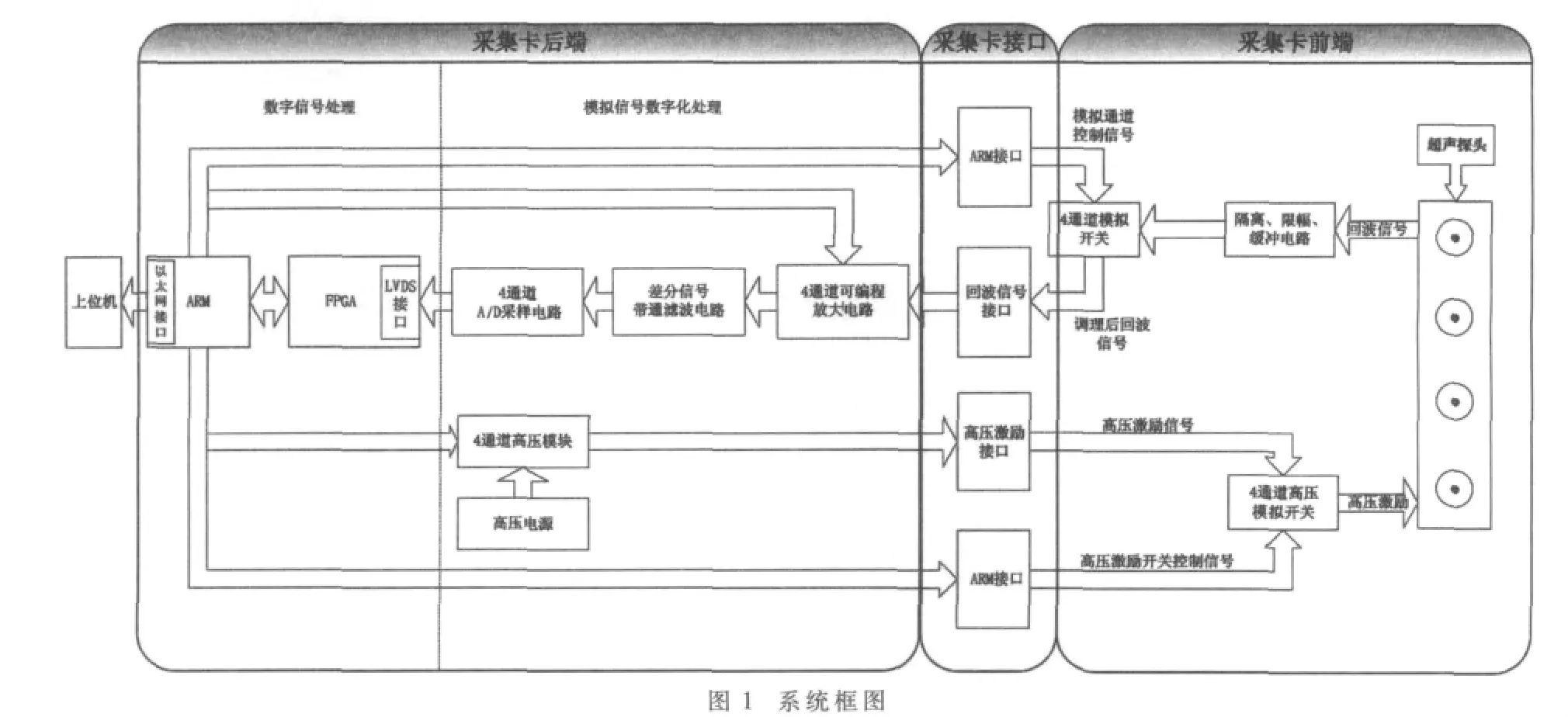

系统整体设计框图如图1所示,分为三个部分:采集卡前端、采集卡接口、采集卡后端。采集卡前端主要为超声波信号的发射与接收电路,该电路的核心包括高压激励信号的产生,超声回波信号的隔离、限幅、缓冲电路以及4通道模拟开关。采集卡前端为硬件可扩展设计,即整个系统搭建完成之后会有多块采集卡前端板卡连接在采集卡接口部分;采集卡接口部分完成连接采集卡后端与多个采集卡前端的任务;采集卡后端实现超声回波信号的放大、带通滤波、A/D转换、数据预处理以及数据融合并传输的功能。

2 功能设计与实现

2.1 硬件扩展的设计思路及实现方案

本系统硬件扩展有并联和串联两种方式。并联式扩展的实现方法是将采集卡前端、采集卡接口、采集卡后端中的模拟信号数字化部分集成在一起,以并联的方式将A/D数据接口接入FPGA中。并联扩展方式的优点:

(1)各个通道之间相互独立工作(包括超声探头的激励与超声回波信号接收)。这一点也可作为超声波相控阵技术的基础。

(2)因为没有了分时复用,大大增加了系统的数据吞吐率,使整个系统的实时性得到了提高。

同时,并联扩展方式的瓶颈和缺点也非常明显:

(1)系统的最大通道数受制于FPGA的逻辑单元数、可用I/O管脚数、片内存储器资源。

(2)系统的功耗、电路板的面积、成本随着通道数的增加而成倍地增加。

而串联式扩展是利用一块采集卡后端与多块采集卡前端通过采集卡接口达到对超声回波信号分时复用的目的。

串联扩展方式减少了器件的数量,提高了系统的集成度。在这种扩展方式下,系统按照4路一组的方式分时轮询所有通道,在满足多路超声波回波信号处理实时性要求情况下,系统的通道数会受到一定的限制。但本系统还是选择串联式扩展方式搭建整个系统。

2.2 FPGA功能实现

FPGA是本系统的核心处理器之一,其功能包括LVDS高速数据接收、超声回波信号数据存储、ARM与FPGA之间总线模拟、A/D转换器的控制以及超声探头高压激励控制信号的产生。

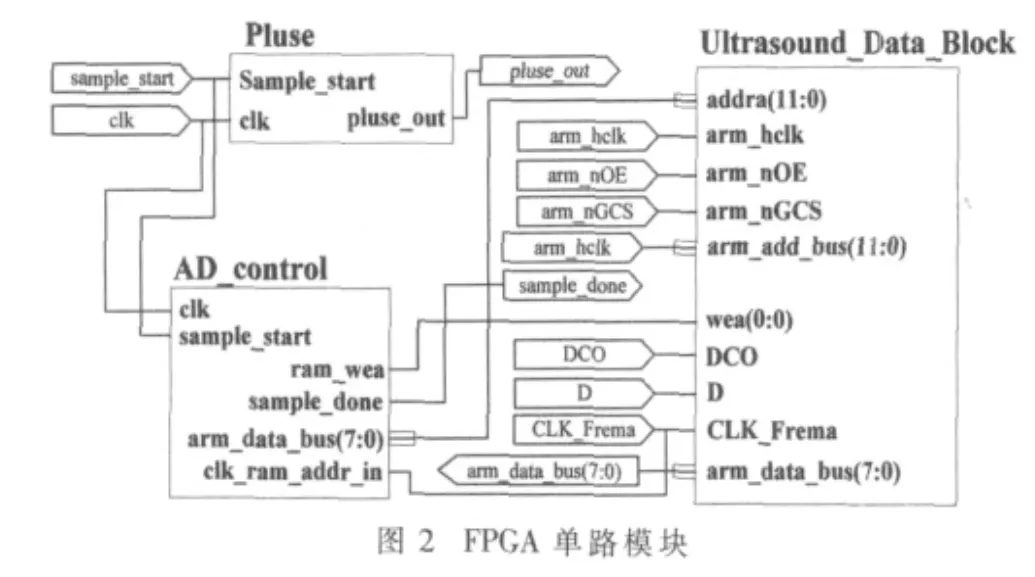

FPGA内部需要协调A/D转换器、高压激励控制信号以及RAM读写时序。以单路为例,其中A/D转换器采样的时序控制是核心。A/D转换器的控制要与超声回波信号同步工作,即当ARM给出“采样开始”信号时,FPGA控制图中Pulse模块产生一个持续 1 μs的脉冲驱动采集卡前端的负高压窄脉冲产生电路激励超声探头产生超声波,同时打开A/D采样功能并与双口RAM协同工作将超声回波信号的数字量存储起来。当存储完毕后再由A/D控制模块给出一个“采样结束”信号,标志此次采样的完成。对于本系统所完成的4路超声回波信号处理模块只需要另外添加3个Ultrasound_Data_Block模块和一个8 bit宽的数据选择模块就可方便实现扩展。

FPGA单路模块如图2所示,图中的Ultrasound_Data_Block模块负责LVDS高速数据接收、超声回波信号数据存储、ARM与FPGA之间总线的搭建。

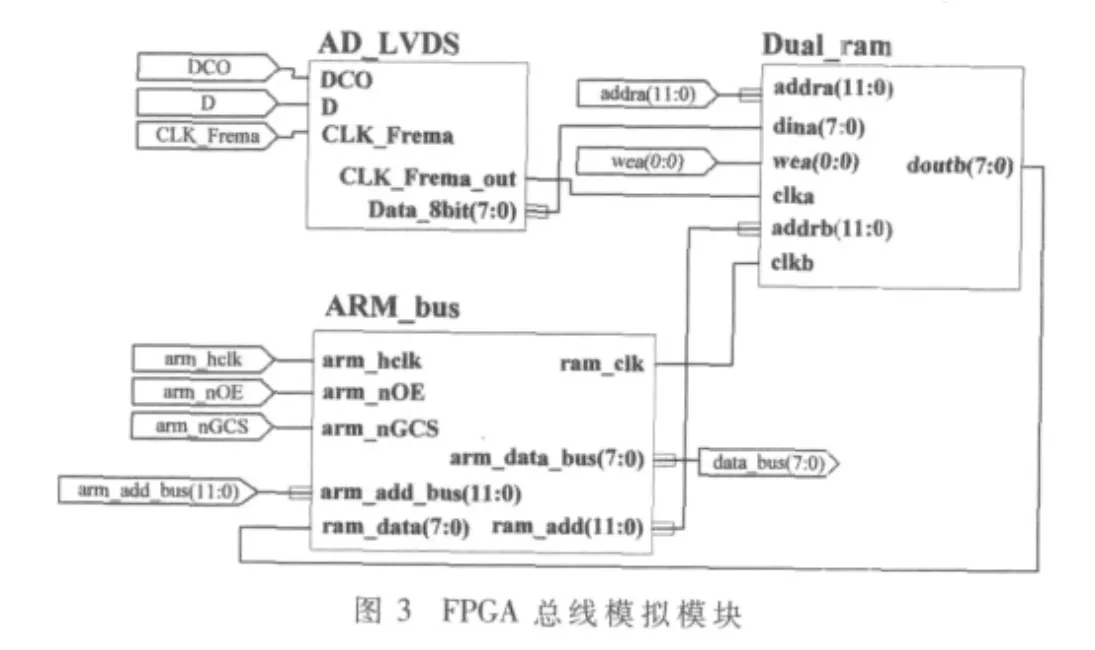

为实现系统的高集成度,本系统所用A/D转换器为LVDS输出。低压差分信号(LVDS)是高速、低电压、低功率、低噪声通用I/O接口标准[3],同时 LVDS信号数据输出采用双边沿采样,在100 MHz的采样频率下,4路LVDS数据输出均高达400 MHz。LVDS串行数据需要转换为并行8 bit数据以用于存储和传输,在FPGA内部完成数据串行转并行的工作由图3中AD_LVDS模块完成。其中DCO是LVDS时钟入,FCO是帧同步LVDS输入,D是数据 LVDS输入,Data_8b是 8 bit A/D采样数据并行输出,CLK_Frema_out是并行数据的同步时钟,用于为后级提供时钟信号。

超声回波信号的存储在本系统中选用双口RAM来实现。双口 RAM通过 Xilinx12.4的 Core Generator中的IP核产生,对应于图3中的Dual_ram。其中双口RAM的A口(地址线 addra、数据总线 dina、写使能信号 wea、时钟信号clka)负责将超声回波信号写入到双口RAM中,B口(地址线 addrb、数据输出总线 doutb、时钟信号 clkb)则负责通过ARM和FPGA之间的总线连接传输数据。

ARM与FPGA之间的总线处理模块如图3中ARM_bus所示。图中由ARM提供的信号:arm_hclk(时钟信号)、arm_nOE(使能信号)、arm_nGCS(片选信号)、arm_add_bus(地址总线)、ram_data(数据总线)通过 FPGA的高速I/O口与外部的ARM相连实现数据的交换,而ram_clk、arm_data_bus、ram_add则连接到双口RAM的B口。

2.3 ARM功能及网络接口的实现

为了通过以太网的方式实现系统控制、数据传输的功能,本模块利用ARM嵌入式系统。ARM嵌入式系统很容易提供网络支持等功能,将每台仪器通过网口实现网络互联,既可以组成局域网,实现数据的多通道采集,也可以连接至互联网,实现 Internet远程控制[4]。

本系统数据存储在FPGA内部例化的RAM上。从ARM的角度,FPGA实际上就是一段连续的RAM空间,其中地址0x18000000~0x18003FFF存放了第4个通道各自的超声回波数据,每个通道存储空间大小为4 096 B。ARM中嵌入Linux实时操作系统后,通过编写Linux底层驱动程序,解决了ARM对FPGA内部总线的驱动以及数据通信的工作。另外,运用Socket网络编程来处理以太网数据通信及控制部分。

本系统的网络传输协议采用UDP协议,其优点是[5]:基于无连接的协议,速度比TCP更快;可以使用广播的方式进行多地址发送;传输需要占用的网络带宽小。

对于4通道超声采集模块而言,每个通道的数据采样深度是4 096 B。由于UDP数据报的长度最大为1 500 B,则对于单个通道的采样数据需要进行拆分。本系统中将每个通道的采样数据分成4份,每份含有1 024 B的采样数据。同时在采样数据的末尾加入2 B的数据标识,其中第一个字节标识为“第几通道”,用来区分不同通道超声回波数据;第二个字节标识为“第几份数据”,用来表示此UDP报中的1 024 B数据是4 096个采样深度的第几份。

3 实验结果

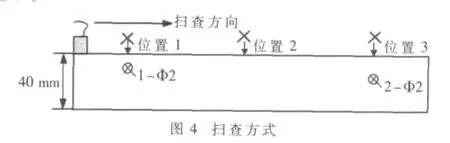

为完成具有以太网功能的大型零件超声探伤仪的测试,制定如下的实验方案:检测对象为CSK-IIA标准试块,其材质为钢。使用广东汕头超声生产的2.5P20单晶直探头,耦合介质为水,扫查方向如图4所示。其中位置1有直径为2 mm、距顶面 10 mm的缺陷,位置3有直径为2 mm、距顶面20 mm的缺陷。用TFT彩屏进行回波显示。

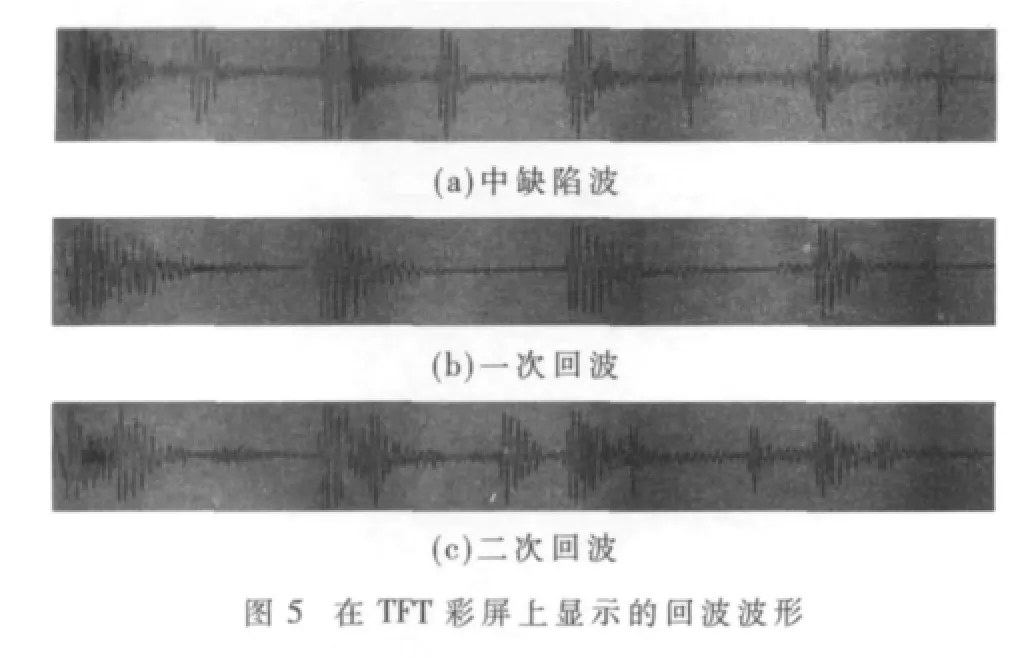

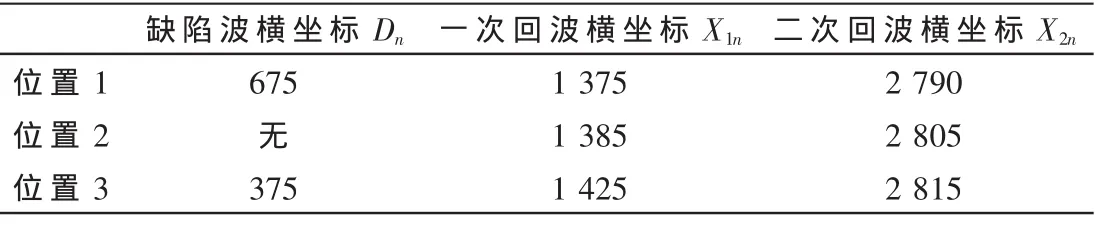

超声探头在位置1、位置2、位置3的回波波形在TFT彩屏上的显示如图 5(a)、(b)、(c)所示。 通过对 TFT显示进行标定,可以得到缺陷波、一次回波、二次回波的中心坐标,如表1所示。

对于缺陷的位置深度dn和试块的厚度 hn,可以用如下公式计算:

其中,fs为采样频率,c为超声波在试块中的传播速度。

表1 显示标定数据

将fs=20 MHz,c=5 900 m/s以及各坐标值代入,可得d1=18.9 mm,d3=10.5 mm,h1=39.62 mm,h2=39.76 mm,h3=38.92 mm,h平均值=39.43 mm。

由上述数据,可得本系统对缺陷位置的测量误差在5%以内,对试块厚度的测量误差在1%以内。系统有较高的准确性,达到了预期的设计目标。

本系统设计了4路超声最小单元采集卡,同时提出了两种用于硬件扩展的方式,并给出了FPGA和ARM功能的具体设计与实现。实验表明,整个系统工作稳定且回波信号接收质量良好,达到了预期目标。

[1]陶有恒.数字化超声波探伤仪控制系统的设计与实现[D].重庆:重庆大学,2009.

[2]邓军.基于嵌入式系统超声波探伤的研究[D].北京:北京交通大学,2008.

[3]徐孟祥,张尔杨.LVDS与高速 PCB设计[J].电子工程师,2005,31(5):38-40.

[4]常青龙.基于ARM平台的超声波自动探伤硬件系统的研制[D].南京:南京航空航天大学,2008.

[5]谢希仁.计算机网络(第五版)[M].北京:电子工业出版社,2008.