基于FPGA的多功能抢答器的设计

沈慧钧

(太原理工大学信息工程学院,山西太原030024)

抢答器可准确、公正地判断出抢答者,可通过数码显示确定第一抢答者,并已广泛应用在各种知识竞赛、文娱活动中。抢答器一般采用中规模集成电路芯片或单片机进行设计[1,2],中规模集成电路芯片设计方案选用触发器、定时器、译码器等芯片进行设计,系统硬件电路复杂,工作不稳定;单片机设计方案选用单片机作为系统控制器,硬件电路简单,性能稳定,但由于单片机管脚有限,不适于有多路输入功能要求的抢答器设计。

随着EDA技术的发展,可编程逻辑器件内部资源更加丰富,并有着并行处理及在系统可编程的灵活性,在现代电子系统设计中发挥着重要作用[3]。本文基于FPGA进行16路输入、具有抢答、计时、报警、电子计分等功能的抢答器设计。

1 设计要求

本文设计的抢答器具有以下功能[4,5]:

(1)16路输入,可供16组选手使用;

(2)具有自锁功能,在有效抢答时间内,第一路抢答信号有效后,其他组抢答信号无效;

(3)具有抢答倒计时功能,主持人复位系统后,计时显示器开始倒计时,当计时时间记到0时,发生报警信号,取消本次抢答;

(4)具有组别显示功能,通过两位数码管显示抢答选手的组号;

(5)具有3位计分功能,可显示每组参赛选手的比赛成绩,主持人根据抢答选手回答问题情况,增加或减少该组分数。

2 系统设计

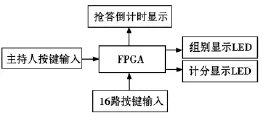

本文设计的抢答器系统结构如图1所示。

系统上电后,当开始抢答时,主持人首先按动复位按钮,输入复位信号至FPGA,复位结束后,等待参赛选手抢答,同时FPGA触发抢答倒计时模块开始到计时,初始时间设为10秒,在倒计时模块递减到0秒之前,如果有参赛选手点击按钮抢答,则FPGA锁存该路抢答信号,不再接收其他按键输入信号,并将该路抢答信号进行编码,输出至组别显示模块,用两位LED数码管显示抢答组别号;在倒计时模块显示0秒之前,如果没有参赛选手点击按钮抢答,则取消该次抢答。

每路抢答信号对应一个3位的计分显示器,参赛选手抢答结束后,如回答问题正确,则主持人通过点击“加分”按钮,可使该路选手对应的计分器加分,加分分值可设定为10分;如选手回答问题错误,主持人可通过点击“减分”按钮,使该路选手对应的计分器减分。当本次抢答结束后,主持人点击复位按钮,开始下一次抢答。

图1 系统结构

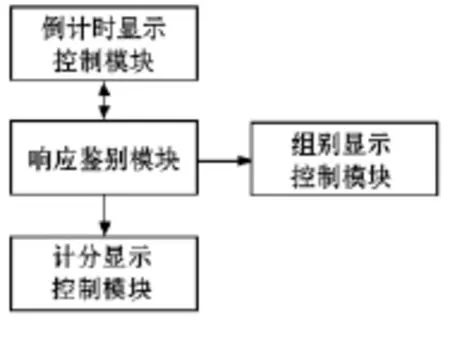

FPGA是抢答器的控制系统,按照EDA设计采用的模块化设计原则,FPGA内部功能模块可划分为:响应鉴别模块、倒计时显示控制模块、组别显示控制模块、计分显示控制模块,如图2所示。

图2 FPGA内部功能模块

2.1 响应鉴别模块

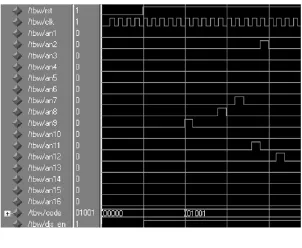

该模块接收主持人发送的复位信号,并接收参赛选手输入的抢答信号,当复位结束后,该模块准备接收抢答信号,当接收到第一组抢答信号后,锁存该组信号,不再接收其他各路输入信号,即只接收最先输入的抢答信号,体现了比赛的公平性。接收到第一路抢答信号后,对16组抢答输入信号进行编码,并将编码结果输出到组别显示控制模块,以显示抢答选手的组号。接收到复位信号后,该模块同时触发倒计时显示控制模块,以显示倒计时信号。该模块对应的波形仿真图如图3所示。

图3 响应鉴别模块仿真波形图

仿真波形图中,rst为复位信号,clk为系统时钟信号,an1…an16为16路抢答输入信号,code为16路编码输出信号,djs_en为倒计时模块使能信号,当复位信号结束后,djs_en信号即为高电平,触发倒计时模块开始工作,第一路输入的抢答信号有效,如图an9信号最先有效,则编码输出信号为“01001”,并锁存该编码信息,此后不再响应其他路抢答信号。

2.2 组别显示控制模块

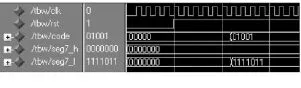

该模块接收响应鉴别模块输出的抢答信号编码数据,并将其译码,以两位共阴极七段数码管显示抢答组别号,对应仿真波形图如图4所示。

图4 组别显示模块仿真波形图

2.3 倒计时显示控制模块

该模块显示抢答倒计时信息,以确保抢答在预定时间内完成,否则取消该次抢答。当该模块接收到响应鉴别模块输出的倒计时使能信号djs_en有效后,在秒时钟脉冲同步下,将显示数值由9递减至0。该模块内部包含分频模块和计数模块,分频模块将100 kHz主时钟分频产生1 Hz计数时钟,计数模块在1 Hz时钟同步下,实现减法计数。

2.4 计分显示控制模块

该模块用于显示各抢答选手的比赛成绩,每路抢答选手对应一个3位的LED数码管,显示该组成绩。当选手抢答结束后,如果回答问题正确,则主持人点击“加分”按钮,给该组选手加分,如果回答问题错误,可点击“减分”按钮,给该组选手减分,为防止出现分数减到负值,可在初始时给每个选手设置初始分数。

由于每组抢答信号对应3个LED数码管,如果选用LED静态扫描方式,则每组需21根信号线,则16组选手就需336根信号线,大大增加了系统复杂度,所以本设计选用LED动态扫描方式,所有LED连接相同的信号线,即FPGA输出的七段数码管控制信号对应连接至所有的LED数码管,并输出使能信号控制数码管,任何时刻只有一个数码管的使能信号有效,其他均无效,根据人眼视觉惰性,每个数码管的扫描频率如果在30 Hz以上,人眼是看不出闪烁的,所以本设计采用动态扫描方式,只需23根信号线即可控制16个LED数码管,大大简化了系统连线复杂度。

3 结束语

本文采用EDA设计方法,完成了16路抢答器的设计,具有组别显示、抢答倒计时、计分显示等功能,设计采用VHDL语言实现,使用Modelsim仿真工具进行波形仿真,并在FPGA上验证。本文设计的抢答器在不改变硬件结构条件下,可根据用户实际需求增加系统功能,应用灵活。

[1]杨俊秀,赵文来,鲍佳.基于FPGA的多路抢答器设计与实现[J].浙江理工大学学报,2010,27(2):249-253.

[2]龚江涛.基于CPLD的4路抢答器设计[J].苏州市职业大学学报,2010,21(4):91 -93.

[3]潘松,黄继业.EDA技术与VHDL[M].北京:清华大学出版社,2009.

[4]刘凯,王红航.电子抢答器的EDA设计与实现[J].电子元器件应用,2010,12(8):54 -57.

[5]尹会明.基于VHDL语言的倒计时抢答器设计[J].信息化研究,2009,35(11):37 -41.