基于微程序控制器的双CPU系统的设计

章鸣嬛,叶有祥

0 引言

随着微电子技术和计算机技术的迅猛发展,尤其是大规模可编程器件,如现场可编程逻辑阵列FPGA(Field Programmable Gate Array)的出现,在苛刻的实时处理系统的要求下,出现了一种新颖灵活的技术——可重构技术。它采用实时电路重构技术[1],在运行时根据需要,动态改变系统的电路结构,主要通过对系统中的可编程器件进行重配置或部分重配置,从而使系统既有硬件优化所能达到的高速度和高效率,又能像软件那样灵活可变,易于升级。可重构体系结构[2]能够跟据不同的应用需求,灵活、快速地改变自身的结构,以便能为每个特定的应用提供与之相匹配的体系结构。

1 32位微处理器系统(实验CPU)的逻辑设计

1.1 “实验CPU”的逻辑结构

1.1.1 “实验CPU”的总体结构框图

控制器是CPU及整个处理器系统的核心,它负责指挥控制协调处理器系统的所有工作。根据微操作控制信号产生方法的不同,控制器可分为常规逻辑控制器和微程序控制器两种。

“实验CPU”采用微程序控制器的方式,其总体逻辑结构,如图1所示:

图1 实验CPU的总体逻辑框图

1.1.2 系统主要模块概述

总线:本系统采用单总线,即微处理器的内部总线和外部总线均为一条总线。采用16位地址总线;结合实验平台要求,采用两条数据总线,一条是入32位CPU的数据总线DBin,另外一条是出32位CPU的数据总线DBout。需要读内存时,连至DBin,要写内存时,连至DBout。

寄存器组:寄存器模块寄存器组中共包括R0至R31共32个寄存器。

运算器部件ALU:ALU包括含累加器A和A2、暂存器ACT、状态寄存器等,可完成各种算术、逻辑运算功能,如加减、与、或及移位等。

指令部件:指令部件模块包括指令寄存器、程序计数器(PC)及其控制电路等。

微程序控制部件:微程序控制摸块包括微指令寄存器、微程序计数器及它的控制电路(加 1、接数等)、微指令寄存器、时序控制电路、微操作信号发生电路等。

存储器:存储器为外接的RAM存储器,容量为32K*8b。

外设:为了实现外部输入信息的处理,系统中使用4*4键盘作为外设。对存储器和外设分别设置独立的读/写信号。

1.2 “实验CPU”的指令集设计

本系统指令集共设计26条常用指令,包括传送、运算、存取及跳转、栈操作、移位、子程序调用等类型,寻址方式包括立即寻址、直接寻址,间接寻址及相对寻址等。

1.2.1 指令执行流程

分别对传送及加法指令在系统逻辑框图中的执行流程进行列举,如表1所示:

表1 指令集举例及指令执行流程

1.2.2 指令编码

对表1中列举的指令进行指令编码,如表2所示:

表2 指令编码

1.3 “实验CPU”的控制器设计

“实验CPU”采用微程序控制器。将微程序控制信号以微码的形式构成微指令,编成多微指令的微程序,存于存储器中。

1.3.1 微指令编码及微程序编码

设计微处理器的微指令宽度为32位。微操作数少于32个,可采用直接表示法每一个微操作信号都由微指令相应的某一位来控制。

根据各指令在系统逻辑框图中的执行流程和微指令编码中信号的有效性,得到微程序编码[3]。以表1中的传送指令:“MOV A,Ri”为例,说明如下:

为了执行该条指令,首先必须根据表1中的指令执行流程,得到在指令执行的过程中,需要用到哪些控制信号,而后根据这些控制信号的有效与否,对控制信号进行取值。

该指令为单字节指令,因此,共需要两条微指令来执行,前条执行本条指令的功能,后条为“取指微指令”。即:

001,0111,1110,1000,1110,0011,1010,1101 17E8E3AE

001,1100,1110,1000,1101,0011,1010,0001 1CE8D3A1

1.3.2 时钟发生选择器及时钟分频器的设计

时钟发生选择器的存在是由于需要产生不同的波形,“实验CPU”连续运行时是连续的方波,单步运行时是两个脉冲,还需要产生持续的低电平用来暂停CPU。

时钟分频器的存在是由于ARM9实验平台上提供的时钟较快,加入该时钟分频器保证了在每次内存操作完成之后,实验CPU才进入下半个时钟周期。本系统中分频倍率为16777216倍,可以将60MHz的晶振频率降到0.25-0.5Hz。

2 实验CPU的逻辑综合及下载

为了利用可重构技术及可编程资源在物理上实现“实验CPU”,需要将实验CPU系统进行VHDL(Very high speed integrated circuit Hardware Description Language,VHDL)描述,形成可综合的代码[4]。

例如,微程序控制器模块功能的部分VHDL描述如下[5]:

--MCLK,MPCK,MICK

process(CLK,RESET,RUN)

begin

if(RESET='0')then MCLK<='0';

elsif falling_edge(CLK)then

if(RUN='1')then MCLK<=not MCLK;

end if;

end if;

end process;

--MCLR

process(MCLK,RESET)

begin

if(RESET='0')then MCLR<='0';

elsif rising_edge(MCLK)then MCLR<='1';

end if;

end process;

3 双CPU监控系统的硬件实现

本开发中所用的综合工具为Synplicity,它是VHDL/VerilogHDL综合软件,生成“.edf”文件后可调入任何PLD开发平台进行布线、仿真和下载。

将经过综合而生成网表文件cpu_32.edf文件,下载到目标板的可编程资源FPGA中,从而构成可重构的“实验CPU”。

4 双CPU监控系统的工作方式研究及结果展示

论文涉及的双CPU监控系统,两个处理器内核均可正常运行指令、执行任务;利用ARM9实验板平台的ARMCPU来监视用“实验CPU”的工作情况,并模拟实验CPU的内存,以实现机器码运行;通过串行口发送的指令来完成单步、运行、停止、实验CPU指令文件传送、实验CPU内存修改、内存察看等工作。本系统利用一个已知的CPU来监控可重构的另一CPU,研究双CPU监控系统,尝试对新的体系结构的研究。

4.1 数据监控的状态口及控制口

为了实现数据监控,例如地址线、微指令地址线、数据线的工作状态,及微指令数据线数值的读取,需要在对应的输出部件连上了状态寄存器(状态口),从而在程序设计中提供了查看接口;而对于“实验CPU”的“运行”与“重启”接口,进行了接上命令寄存器(控制口)的连接,从而可以控制“实验CPU”的运行与初始化。

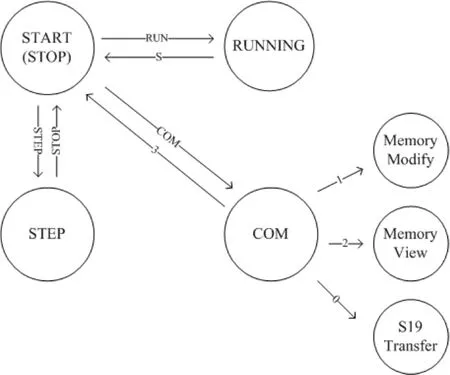

4.2 双CPU监控系统的通信状态分析

双CPU监控系统的工作内容可以分为两部分。一部分是初始化工作,其中涉及到中断服务程序的初始化、对通信口的初始化,对模拟内存的初始化等工作;另一部分是状态机,主要由4种不同的大状态组成,分别是:STOP(START),RUNNING,STEP,COM。状态之间的关系,如图4所示:

图4 双CPU监控系统的工作状态转换

(1)START状态下,32位“实验CPU”未处于运行状态。因此相关的状态是设置CPU的“重启”及“运行”均为无效状态(低电平0)。

(2)RUNNING(连续运行)状态下,32位“实验CPU”全速运行,CPU的“重启”及运行均处于有效状态。时钟发生选择器需要产生连续的方波。系统还特别设置了直接进入STOP(START)状态的快捷键。

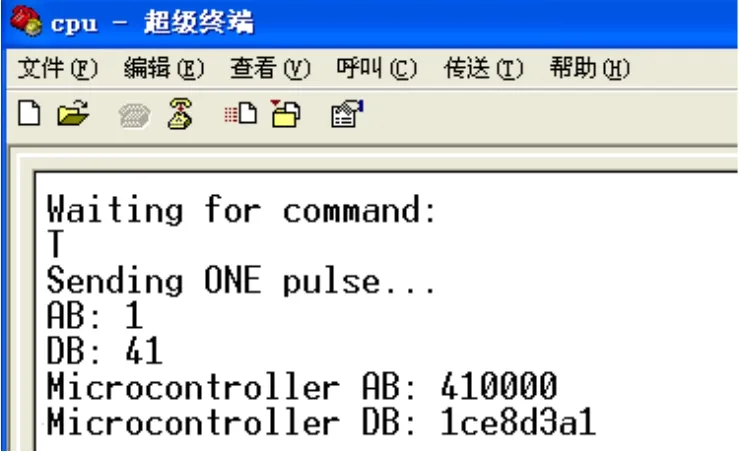

(3)STEP(单步运行)状态下,32位“实验CPU”单步运行,时钟发生选择器产生两个脉冲。之后每按一次“单步运行”快捷键T,“实验CPU“完成一个工作周期,并打印出几个监控接口的观察值。在STEP中的工作状态,如图5所示:

图5 系统进入STEP模式

(4)COM状态下,将有3个功能菜单可供选择:0选择文件(机器指令文件,即S19文件)传输,1、选择模拟内存修改,2、选择模拟内存察看,3、选择退回到执行(START)模式。在这个状态下,文件传输就是将机器指令文件通过串行口传至ARM CPU,解码后放在指定内存地址中,然后可以退回到执行模式下运行即可;内存察看的方法是,选择2即可输入地址,按回车可以查看;内存修改则输入地址和需要修改的内容即可。如图6所示:

图6 COM模式下内存查看

5 实验结果分析

5.1 双CPU监控系统的特点分析

通过上述分析,可以看出双CPU监控系统具有以下特点:

(1)该系统在工作时能够正常稳定的运行指令和执行任务,可实现处理器资源的并行处理,提高处理器的实时工作性能。

(2)在工作时,ARM-CPU能够监视“实验CPU”的工作状态,提高实验CPU工作的稳定性。

(3)本系统采用可重构资源实现,实现硬件系统的软件化,便于系统升级。

5.2 与其他设计方式的对比分析

本系统的另一特点是,32位的“实验CPU”具有较快的系统时钟,大约仅需要0.01秒即可完成一个周期,有较高的工作效率,并引入了键盘作为外设,进行内存与外设的交互。

为了节省可重构的资源,也采用了模拟内存的方式,但结果显示,速度立刻会下降。这是因为内存是模拟的,因此很多操作就会占用时间。以内存读取为例,首先,由于地址是通过放在内存中的一个变量实现的,对其读取意味着是对内存操作;其次,要读取指定地址的模拟内存的值,这又需要一次内存操作;最后将结果放置于数据总线DBin上,这也是一次内存操作。综合多方面的因素,大约需要4秒钟才能完成一个工作周期。

6 总结

本文论述采用可重构技术,利用实验平台的可编程资源,设计出简单灵活的微处理器系统,该微处理器拥有指令集和控制单元,能够正确执行所有指令;并利用该平台上的另一处理器ARM-CPU,可与已有的微处理器构成双CPU监控系统,从而获得更高可靠性和实用性系统。并可以根据根据需要添加适当的外部设备,如在扩展实验中,本研究还将外部的模拟信号引入并进行数模转换,再对得到的数字信号分析处理。

[1]章鸣嬛.基于可重构技术的双核微处理器系统的设计[J].微型电脑应用,2011,27(7):12-14.

[2]徐佳庆,邬贵明,窦勇.二维DCT在粗粒度可重构处理器上的实现[J].计算机工程,2008,34(20):257.

[3]徐允文,蔡敏.基于微程序技术的存储控制器的研究和设计[J].半导体技术,2007,32(11):997.

[4]黄洁.可编程逻辑器件及其应用前景[J].中国科技信息,2005,13:38.

[5]陈耀和.VHDL语言设计技术[M].北京:电子工业出版社,2004:7-8.