MCR和MRC指令在存储系统中的使用

王茹

摘要:ARM协处理器CP15中的MCR指令和MRC指令是非常重要的指令,担负着协处理器和主处理器之间的数据传递。对于虚拟存储来来讲作用尤为重要,它可以通过设置MMU、Cache、TLB表等操作来实现虚拟存储。MCR指令和MRC指令用法复杂,目前介绍这两个指令应用的资料不多,大多点到即止。该文主要通过具体实例介绍MCR指令和MRC指令在ARM存储系统中的使用情况。

关键词:存储系统;MCR;MRC;MMU;Cache

中图分类号:TP313文献标识码:A文章编号:1009-3044(2012)05-1190-04

MCR and MRC Instructions Used in the Storage System

WANG Ru

( Liaoning Equipment Manufacturing Technical College, Shenyang 110161, China)

Abstract: MRC and MCR instructions are very important command in the ARM coprocessor CP15, their responsible is data transfer be? tween co-processor and host processor. They are particularly important to virtual storage, it can set the MMU, Cache, TLB table and other operations to achieve the virtual storage. MCR and MRC instructions are complex instructions, Now, the application describe of these two commands is no more information. This paper mainly through concrete examples to introduced how to use MCR instructions and MRC instructions in the ARM memory system .

Key words: storage system; MCR; MRC; MMU; Cache

在基于ARM的嵌入式应用系统中,存储系统的操作通常是由协处理器CP15完成的。CP15包含16个32位的寄存器,其编号为0~15。而访问CP15寄存器的指令主要是MCR和MRC这两个指令。本文主要介绍MRC和MCR指令在存储系统中是如何使用的。

1 MRC和MCR指令格式

1.1 MRC指令格式

MRC {条件}协处理器编码,协处理器操作码1,目的寄存器,源寄存器1,源寄存器2,{协处理器操作码2}

MRC指令用于将协处理器寄存器中的数据传送到ARM处理器寄存器中,如果协处理器不能成功地执行该操作,将产生未定义的指令异常。

其中,协处理器操作码1为协处理器将要执行的操作。对于CP15协处理器来说,协处理器操作码1永远为0b000,当协处理器操作码1不为0b000时,该指令操作结果不可预知;

目的寄存器为ARM处理器的寄存器;源寄存器1和2为协处理器的寄存器;

协处理器操作码2为协处理器将要执行的操作。通常源寄存器2和协处理器操作码2两者组合决定对协处理器寄存器进行所需要的操作,如果没有指定,则将源寄存器2设置为C0,协处理器操作码2设置为0,否则可能导致不可预知的结果。

1.2 MCR指令格式

MCR {条件}协处理器编码,协处理器操作码1,源寄存器,目的寄存器1,目的寄存器2,{协处理器操作码2}

MCR指令用于将ARM处理器寄存器中的数据传送到协处理器寄存器中,如果协处理器不能成功地执行该操作,将产生未定义的指令异常。

其中,源寄存器为ARM处理器的寄存器;目的寄存器1和2均为协处理器的寄存器;协处理器操作码1和2的含义及用法同MRC指令。

2 MRC和MCR在存储器管理单元(MMU)中的使用

2.1禁止/使能MMU

CP15协处理器的寄存器C1的位[0]用于控制禁止/使能MMU。当CP15协处理器的寄存器C1的位[0]设置为0时,禁止MMU;当CP15协处理器的寄存器C1的位[0]设置为1时,使能MMU。

使能MMU的指令:MRC P15, 0 , R0 ,C1 ,0 , 0

ORR R0,R0,#1

MCR P15, 0 ,R0 , C1 ,0 , 0

禁止MMU的指令:MRC P15, 0 , R0 ,C1 ,0 , 0

BIC R0,R0,#1

MCR P15, 0 ,R0 , C1 ,0 , 0

2.2设置页表的基地址

页表存放在内存中,通常在ARM中系统协处理器CP15的C2寄存器用来保存页表的基地址。其中位[31:14]为内存页表的基地址,位[13:0]为0。

加载页表的首地址到CP15协处理器的寄存器C2的指令,例如:

MOV R3,#0X12340000

MCR p15, 0, R3, C2, C0, 0

2.3 MMU中存储访问权限控制

在MMU中,寄存器C1的R、S控制位和页表中地址转换条目中的访问权限控制位AP联合作用控制存储访问的权限。具体规则如表1所示。[1]

表1 MMU中存储访问权限控制

C1寄存器的R和S位的设置的指令,例如:

MRC p15, 0, R0, c1, c0, 0; read control register

AND R0,R0,#0XFFFFFCFF;set R=0,S=0

MCR P15, 0 ,R0 , C1 ,0 , 0; write control register

2.4 MMU中域的控制

MMU中的域指的是一些段、大页或者小页的集合。ARM支持最多16个域,每个域的访问控制特性由CP15中的寄存器C3中的两位来控制。

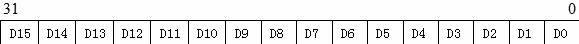

CP15中的寄存器C3的格式如图1所示。

图1 C3寄存器格式

该寄存器有效位为32,被分成16个区域,每个区域由两个位组成,含义如下:

00:当前级别下,该内存区域不允许被访问,任何的访问都会引起一个domain fault

01:当前级别下,该内存区域的访问必须配合该内存区域段描述符中AP位进行权检查

10:保留状态

11:当前级别下,对该内存区域的访问都不进行权限检查

设置域的访问权限可使用以下语句,例如:

MRC p15, 0, R0, C3, C0, 0; Read domain 15:0 access permissions

ORR R0,R0,#0X00000030 ; Set D2=0b11

MCR p15, 0, Rd, C3, C0, 0; Read domain 15:0 access permissions

2.5快表(TLB)的使用

2.5.1使快表内容无效的操作

CP15协处理器的寄存器C8是用来控制清除TLB内容的相关操作。它是一个只写寄存器。使用MRC读取该寄存器,会可能产生不可预知的效果。可使用MCR指令来写该寄存器,具体格式如下:

MCR {条件} P15,0,源寄存器,C8,目的寄存器2,{协处理器操作码2}

其中,源寄存器中位将写入C8中的数据;目的寄存器2,协处理器操作码2的不同组合决定指令执行不同的操作,具体含义如表2所示。[2]

表2使无效快表内容的指令格式

2.5.2锁定快表内容

MMU可以将某些地址变换条目锁定在TLB中,从而使得进行与该地址变换条目相关的地址变换速度保持很快。在MMU中寄存器C10用于控制TBL内容的锁定。

TLB锁定指令的具体格式:

MCR P15 , 0 ,源寄存器, C10 , C0 ,协处理器操作码2。

MRC P15 , 0 ,目的寄存器,C10 , C0,协处理器操作码2。

当系统中包含独立的数据TLB和指令TLB时,对应于数据TLB和指令TLB分别有一个独立的TLB内容锁定寄存器。上面指令中的协处理器操作码2用于选择其中的某个寄存器。

协处理器操作码2=1,选择指令TLB的内容锁定寄存器。

协处理器操作码2=0,选择数据TLB的内容锁定寄存器。

当系统中使用统一的数据cache和指令cache时,协处理器操作码2的值应为0。

例如:MCR p15 , 0 , r0 , c10 , c0 , 0;锁定数据TLB。

MCR p15 , 0 , r0 , c10 , c0 , 1;锁定指令TLB。

3 MRC和MCR在高速缓冲存储器(Cache)中的使用

3.1控制cache和写缓冲区

CP15中的寄存器C7用于控制cache和写缓冲区。它是一个只写的寄存器,使用MCR指令来写该寄存器,具体格式如下:

MCR P15, 0,源寄存器, C7,目的寄存器2,操作码2

其中,源寄存器为将写入C7中的数据;目的寄存器2,操作码2的不同组合决定执行不同的操作,如表3所示。[2]

表3 MCR指令中目的寄存器2,操作码2的不同组合决定执行不同的操作

例如:MCR p15, 0, r0, c7, c7, 0;disable ICache, DCache

3.2锁定Cache

寄存器C9是Cache内容锁定寄存器。Cache内容锁定就是将一些关键代码和数据预取到Cache后,设置一定的属性,使发生Cache块替换时,这些关键代码和数据所在的块不会被替换。[3]

Cache锁定指令的具体格式:

MCR P15 , 0 ,源寄存器, C9 , C0 ,协处理器操作码2

MRC P15 , 0 ,目的寄存器, C9 , C0,协处理器操作码2

当系统中包含独立的数据Cache和指令Cache时,对应于数据Cache和指令Cache分别有一个独立的Cache内容锁定寄存器。上面指令中的协处理器操作码2用于选择其中的某个寄存器。

协处理器操作码2=1,选择指令cache的内容锁定寄存器。协处理器操作码2=0,选择数据cache的内容锁定寄存器。

当系统中使用统一的数据cache和指令cache时,协处理器操作码2的值应为0。

例如:MCR p15 , 0 , r0 , c9 , c0 , 0;锁数据Cache

MCR p15 , 0 , r0 , c9 , c0 , 1;锁指令Cache

4结论

ARM中协处理器CP15中的MCR指令和MRC指令是非常重要的指令,担负着协处理器和主处理器之间的数据传递。对于虚拟存储来讲作用尤为重要,它可以设置MMU、Cache、TLB表实现虚拟存储。本文只对存储系统中主要的几个功能涉及的MCR和MRC指令如何使用做以介绍,希望通过具体的应用例子,读者能对MRC和MCR指令有更深的认识。

参考文献:

[1]杜春雷. ARM体系结构与编程[M].北京清华大学出版社,2005.

[2]孙晔. ARM嵌入式系统及应用[M].江苏教育出版社,2011.

[3] ARM9协处理器CP15及MCR与MRC [EB/OL]. http://6xudonghai.blog.163.com/blog/static/336406292008724103317304/.