FPGA在声发射参数提取中的应用

徐文杰,徐 静

(1.浙江联合应用科学研究院,浙江 杭州 310015;2.浙江省特种设备检验研究院,浙江 杭州 310020)

材料或结构在受外力或内力作用时,产生变形或断裂,会以弹性波的形式,快速释放出应变能,这一现象成为声发射。声发射信号的产生,是瞬态的和随机的,属于非平稳性信号。其带宽容量大,在数赫兹到数十兆赫兹之间,而且呈多模态特征。声发射技术,就是根据结构内部发出的弹性波,来判断内部损伤程度的一种新型动态无损检测方法,其工程应用受噪声影响很大,需要分析处理的信息量非常多。

1 声发射信号的分析方法

目前,分析声发射信号的方法有两种:一种是波形分析,一种是参数分析。

波形分析,受到硬件和高级信号处理技术的限制,工程上应用很少,大多应用于实验室分析。

而参数分析,则是一般工程应用普遍采用的方法。即把一列声发射信号用数个特征参数加以表示,起到简化信号、提高处理效率的作用。

声发射信号特征参数主要有:上升(前沿)时间、事件发生时间、事件或撞击、(振铃)计数、幅度、能量和持续时间等(见图1)。

图1 声发射波形及参数示意图

工程应用中,一般是通过判断是否采集到声发射信号,来判断活动缺陷的有无,进而通过对声发射信号的不同参数进行分析,来判断缺陷的性质和发展情况。

所以,采集到真正可靠的声发射信号参数,对于分析材料或构件在受力时内部缺陷的产生和发展非常重要,关系到工程检测的成败。

2 FPGA的原理

FPGA(Field Programmable Gate Array——现场可编程门列阵)采用了逻辑单元阵列LCA(Logic Cell Array)这样一个概念,内部包括可配置逻辑模块CLB(Configurable Logic Block)、输出输入模块IOB(Input Output Block)和内部连线(Interconnect)这3个部分。

现场可编程门阵列(FPGA)是可编程器件。与传统逻辑电路和门阵列(如PAL,GAL及CPLD-复杂可编程逻辑器件)相比,FPGA具有不同的结构,FPGA利用小型查找表(16×1RAM)来实现组合逻辑,每个查找表连接到一个D触发器的输入端,触发器再来驱动其他逻辑电路或驱动I/O,由此构成了既可实现组合逻辑功能,又可实现时序逻辑功能的基本逻辑单元模块。这些模块间,利用金属连线互相连接或连接到I/O模块。

FPGA的逻辑,是通过向内部静态存储单元加载编程数据来实现的,存储在存储器单元中的值,决定了逻辑单元的逻辑功能,以及各模块之间或模块与I/O间的联接方式,并最终决定了FPGA所能实现的功能,FPGA允许无限次的编程。

声发射参数的提取,绝大部分是通过设计FPGA所获得的声发射参数提取电路来实现的,是在PAL、GAL、CPLD等可编程器件的基础上,进一步发展的产物。

实际上,FPGA与CPLD的功能,具有相似性,存在一定的继承关系,都包括了一些相对大数量的可编辑逻辑单元,只是前者逻辑门的密度,比后者要多出10~100倍,能达到数万到数百万个逻辑单元。但在价格、逻辑单元规模和运算速度上,就有所差异。

根据所选器件的型号和所需实现的功能,设计时充分发挥器件的特性,就能达到想要的结果。FPGA中的寄存器资源比较丰富,适合做同步时序电路较多的设计;而CPLD中的组合资源比较丰富,适合做组合逻辑电路较多的设计。

就声发射参数而言,其产生时间短,一般在数纳秒至十多纳秒内,就会产生多个不同的声发射参数,而且要做到分别将这些参数及时存储,同时需要考虑参数的时序关系。

时序问题处理不当,会导致重要数据的遗失,甚至系统瘫痪,而无法存储后续采集的数据。

因此,在声发射参数采集时,选用功能相对强大的FPGA来设计参数提取电路,具有一定的优势。

3 FPGA的特点

目前,主流的FPGA仍是基于查找表技术的,整合了常用功能(如RAM、时钟管理和DSP)的硬核(ASIC型)模块,实际功能远远超出了先前版本。FPGA芯片一般由7个部分组成,即:可编程逻辑单元,可编程输入输出单元,完整的时钟管理,丰富的布线资源,嵌入块式RAM,内嵌底层功能单元和内嵌专用硬件模块。

其主要特点有:

(1)规模不断增加,所实现的功能不断增强,更适于片上系统(SOC)的设计。

(2)开发投资小。FPGA设计灵活,开发周期短,可直接更改设计,开发风险小,开发费用低。

(3)FPGA上写入的程序可擦除,能实现反复编程,内部有丰富的触发器和I/O引脚。在不改变外围电路的情况下,设计不同的片内逻辑,就能实现不同的电路功能。

(4)保密性能好,系统安全性高,有利于保护开发者的知识产权。

(5)FPGA开发简单,智能化程度高,功能强,易于学习,可避免设计人员在开发工具上耗费过多精力,而更能集中精力进行电路设计,提高开发效率。

(6)FPGA采用高速CMOS工艺,功耗低,可以与CMOS、TTL电平兼容。

4 FPGA解决方案的应用

FPGA芯片的输入信号为从AD转换器获得的采样信号、复位信号及系统时钟信号,而输出即为要求的声发射参数。原理如图2。

图2 FPGA声发射参数提取示意图

基于VHDL硬件描述语言的FPGA声发射信号参数采集流程图,如图3。

图3 FPGA声发射信号参数采集流程图

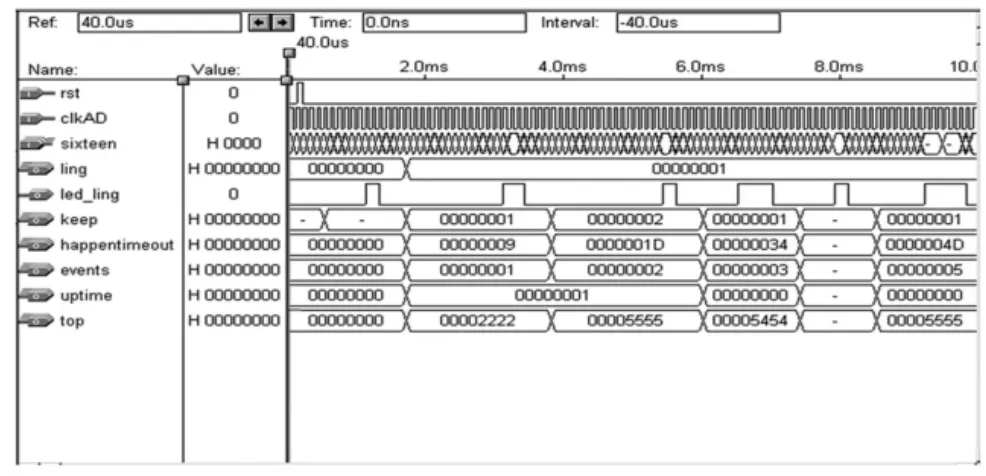

参数采集仿真时序图,如图4。

FPGA的16个I/O引脚的一个输入值为图4中AD转换后的采样值(sixteen),其为16位精度的二进制数。

图4 参数采集仿真时序图

另外,输入的信号还有系统复位信号rst(高电平有效)和系统时钟上升沿触发信号clkAD。接收到输入信号后,FPGA随后按照预置的满足要求的算法,来实现声发射参数的提取,输出结果即为声发射参数。有:事件发生时间(happentimeout)、事件持续时间(keep)、上升时间(uptime)、峰值大小(top),过门槛振铃计数(ling),10 ms内的事件发生总数(events),以及事件发生报警(led_ling)(高电平有效)。

以上英文注释为输入或输出信号的代码,仿真结果的参数列表,如图5,得到6次事件。

图4中(sixteen)为AD转换后的采样值,直接输入至FPGA的16个I/O引脚上(采样值是16位精度的二进制数),另外,输入的信号还有系统复位信号rst(高电平有效),以及系统时钟输入信号clkAD(上升沿触发),其频率数值可根据具体情况的需要,在源程序中进行修改。然后按照满足要求的算法,来实现声发射参数的提取,输出结果即为声发射参数,有:事件发生时间(happentimeout)、事件持续时间(keep)、上升时间(uptime)、峰值大小(top),过门槛振铃计数(ling),10 ms内的事件发生总数(events)(在图5中共有6次事件),以及事件发生报警(led_ling)(高电平有效)。以上英文注释为输入或输出信号的代码,仿真结果的参数列表,如图5。

图5 实验中采集的参数列表

5 结束语

FPGA具有可编程性和实现方案容易改动的特点,其可实现在其外围电路保持不变的情况下,通过更换EPROM芯片或植入新的硬件描述,就能实现新的功能,从而使得其应用方便,且高效。从某种程度上来讲,这是数字电路发展的方向。

用FPGA来提取声发射参数,实现声发射监测系统的基本功能,程序代码易于改变,为更复杂的参数的提取,创造了有利的开发环境和条件。参数采集模拟实验结果表明,该设计方法能够保证采集到相对真实的声发射信号特征参数。

[1]薛小刚,钟 信.FPGA/CPLD设计工具Xilinx ISE5.X使用详解[M].北京:人民邮电出版社,2003.

[2]沈功田,耿荣生,刘时风.声发射信号的参数分析方法[J].无损检测,2002,24(2):72-76.

[3]闫素珍,刘满仓.声发射技术及其应用[J].西安航空技术高等专科学校学报,2002,(3):37-38.

[4]刘明业,等.集成电路/计算机硬件描述语言VHDL高等教材[M].清华大学出版社,2003.

[5]林明权,等.VHDL数字控制系统设计范例[M].北京:电子工业出版社,2002.