一种高电源抑制比全工艺角低温漂CMOS基准电压源

方 圆 , 周凤星 , 张 涛 , 张 迪

(1.武汉科技大学 湖北 武汉 430080;2.德鑫微电子公司 湖北 武汉 430070)

在很多模拟芯片和数模混合芯片中都需要用到带隙基准电路提供精确、稳定的参考电压。然而在数模混合芯片中由于数字电路会产生很严重的高频噪声,通过带隙的电源耦合到带隙的输出参考电压,进而使数模混合芯片的性能受到很大程度的制约[1-2]。因此需要设计具有较高PSRR的带隙基准电路。针对该问题本文提出了用电压放大器放大带隙电压作为带隙的供电电源的方法得到了较高的电源抑制比。

目前一些文献在传统带隙的基础上提出了二阶曲率补偿,多点曲率补偿等技术使基准电压的温漂系数达到了10 ppm以下,但是这些结果都是在某种理想的工艺(比如tt)下取得的。在实际的工艺下,电阻的阻值和三极管的导通电压都会发生变化,比如从tt工艺到ff工艺电阻值会下降,三极管的导通电压会上升(smic0.35工艺)使正负温度电压不再能够抵消。从而导致实际流片出来的基准电压值是离散的,而且温漂系数很大。针对该问题本文分析了原因,并提出了通过调整决定正温度系数电压的电阻的方法来实现在不同工艺下低温度系数的参考电压的输出。

1 高电源抑制比的电路设计

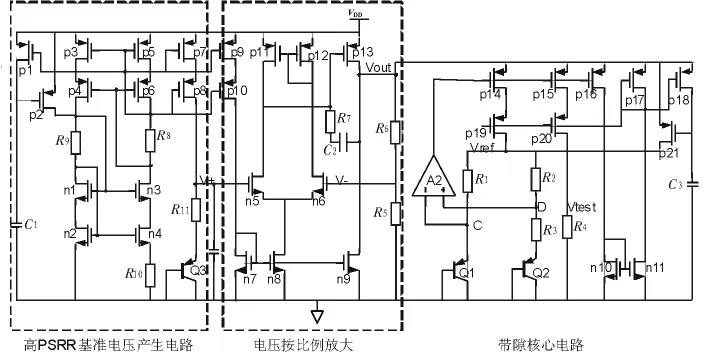

该电路由一个高PSRR基准电压产生电路、一个电压按比例放大电路、和带隙核心电路组成,高PSRR基准电压电路的输出接到了电压放大器的正向输入端(图中V+端),运放的输出端(图中Vout端)通过R6,R5电阻分压接到了运放的负向端(图中V-端)以产生负反馈,运放输出端Vout为带隙核心电路供电。

图1 高PSRR带隙基准电路结构Fig.1 High PSRR bandgap voltage reference circuit

高PSRR基准电压产生电路采用了共源共栅电路结构,为了得到p4、p6以及n1、n3管的偏置电压,采用了电阻自偏置结构。该结构避免了p3、p5、n2、n4的沟道调制效应所导致的产生电流的电源依赖性,使输出电流达到很高的PSRR。P7,p8的电流是p5,p6电流的镜像,仿真发现该电流随温度升高线性上升,所以P7支路的电流流过R11将产生随温度成正比的电压。该支路的PNP三极管Q3的Veb具有负温度系数。适当调整R11的值即可使R11的正温度电压和Q3的负温度电压相抵消,从而在V+端得到零温度系数的基准电压。仿真得到该电压在-45~80℃的值为1.25~1.26 V,并且具有60 dB的电源抑制特性。

电压按比例放大器采用了常规的两极放大器。考虑到该运放的输出端的电流主要流向带隙电路,可以将n9宽长比适当减小,避免多余的电流消耗。R7和C2产生了一个可控的零点适当调节R7可以将位于左半平面的第二极点抵消,即使驱动较大的电容负载,运算放大器仍然具有很好的稳定性。仿真时要保证在加上真实负载(即带隙核心电路,包括电路中的寄生电容负载)的情况下任然可以达到60度以上的相位余量以保持反馈系统的稳定。

在带隙核心电路中运放A2也采用了普通的两极放大结构,考虑到p沟道管输入的两极放大器的正的PSRR要大于n沟道管输入的两极运放,而且衰减频率也比n沟道管输入的两极运放高得多。另外由于运放A2的输入共模电位在1 V以下,而n沟道管输入的两极运放正常工作的共模电位范围难以达到这么低。根据以上两个因素A2选择了使用p沟道管输入的两极运放。

带隙核心电路可以使p14管产生随温度成正比的电流,p15即是用来复制这个电流,并使该电流流过R4以产生一个随温度成正比的电压(即图中Vtest),以供测试。由于p15的沟道长度调制效应,Vtest的电压也会影响到p15的电流,为了避免这种影响所以采用了P14,p15,P19,p20为共源共栅结构以保证流过R4的电流是p14管电流的精确复制。图中p16,n10,n11,p17,组成了偏置电路,为 p19,p20 提供了电压偏置。

P18,p21,c3是带隙的启动电路,当Vout电压建立起来之后,c3两端电压为零,即p31栅极为低电位是p21管导通,为带隙提供启动电流。带隙启动后,p17管建立了偏置电压,使p18管导通,导通电流给c3充电至高电平,随后p21管截止。

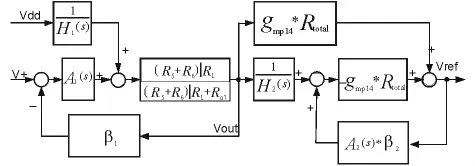

将图1的电压按比例放大电路与带隙核心电路的小信号数学模型归纳如图2所示。

图2 电压按比例放大电路与带隙核心电路的小信号数学模型Fig.2 Small signal mathematical model of voltage amplifier and bandgap core circuit

图中H1(s)为电压放大器A1空载时电源Vdd的噪声通过运放A1内部通路传递到Vout端的传递函数。

A1(s)为电压放大器 A1的差模增益。

β1为放大器A1负向端比上Vout端的电压的系数。

Ro1为放大器A1的空载输出电阻。

RL为带隙核心电路对Vout端的等效负载电阻。

gmp14为p14管的跨导。

Rtotal为Vref端到地的总电阻。

A2(s)为电压放大器 A2的差模增益。

H2(s)为Vout通过运放A2内部通路传递到A2输出端的传递函数。

β2为运放A2的正向差模输入端的电压比上Vref端的电压的系数。

要考虑的是电源电压Vdd的变化量对Vref变化量的影响。由于V+是由高PSRR基准电压产生电路产生的,可以认为变化量很小,将其置零忽略。在工作时,电源电压Vdd的变化(即噪声)会迫使P13管的栅极跟着变化,进而通过P13的栅漏电容耦合到Vout输出端,(H1(s)即是这种效应的度量)进而使输出基准电压Vref受到电源噪声的影响。但是,由运放A1和电阻组成的负反馈结构有效的抑制了噪声通过A1中p13管对系统输出造成的影响。准确的Vdd与Vref的比例关系(电源抑制比)为

该式(1)表明较之单独的带隙核心电路,由于采用了电压放大器供电,在公式的分子中增加了 H1(s)A1(s)β1项,由于该项在低频时的值很大,使得低频电源抑制比大大增加。由(1)式还可以看到,通过增加运放A2的增益或者减小p14管的跨导可以进一步增大电源抑制比。

2 全工艺角低温漂电路的实现

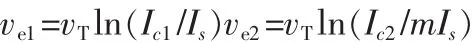

首先分析一下本文设计的带隙基准核心电路在tt工艺下,得到零温度系数基准电压的原理。在图1中三极管Q2的发射极面积是Q1的m倍,设Q1的反向饱和电流是Is,则Q2的反向饱和电流是mIs。运放A2保证了C、D两端的电位相等,设R2/R1=n,则流过三极管Q1,Q2的集电极电流之比Ic1/Ic2=n。两个三极管发射极的电位分别是

可以得出两个三极管的发射极电位差即R3两端的电压是

式中vT=KT/q,m、n均为常数。所以三极管发射极电位的差值呈现正的温度系数:

可以看出该系数是个常数,不受温度和集电极电流的影响。

同时三极管Q1的发射极电位ve1具有负温度系数:

由式(3)可以看出发射极电位的温度系数受发射极电位本身以及温度的影响。其中m=-3/2,当ve1=750 mV,T=300 K时,∂ve1/∂T≈-1.5 mV/K。

则输出基准电压的温度系数为

在实际的电路工艺中,由于电阻、和三极管的工艺偏差,将导致电流、以及ve1的不同,从而使式(6)中的第一项的负系数发生变化,由式(6)可以看出可以调整R3的值以调整第二项的正系数,来保证基准电压的温度系数为零。通过仿真发现,用这种方法可以在不同工艺角下都能得到5.6×10-6V/℃以下的温度系数。

3 仿真结果与讨论

该设计在SMIC的0.35μm标准CMOS工艺下实现,使用相应的工艺库文件在Cadence virtuoso下面进行仿真,得到电路的主要性能参数。

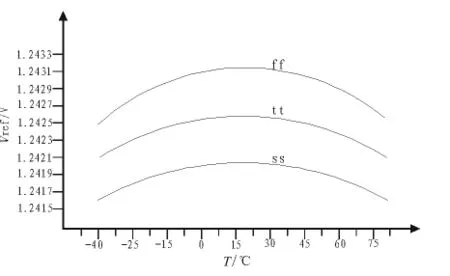

3.1 带隙输出电压的温度特性曲线

当电源电压是 4 V 时,在不同工艺角下包括(tt,ss,ff)对温度进行扫描。在每种工艺角下调整R3到最佳状态,得到的温度特性曲线如图3所示。可以看出,在-40~80℃范围内,3个工艺角的温度系数分别为 5.6×10-6V/℃,4×10-6V/℃,3.7×10-6V/℃。由此可见通过调整R3可以在全工艺角下得到低温度系数的基准电压。

图3 本文带隙输出基准电压在不同工艺角下的温度特性Fig.3 Temperature characteristics of the proposed bandgap voltage reference at different process corner

3.2 电源电压调整率

在27℃下,对电源电压进行DC扫描仿真结果如图4所示。从图中可以看出当电源电压高于2.2 V时,电路可以建立稳定的输出电压,当电源电压在2.2~5 V范围内变化,带隙输出电压的调整率为438.1μV/V。

图4 本文带隙基准电压的电压调整率Fig.4 Voltage regulation of the proposed bandgap voltage reference

3.3 PSRR特性

电源抑制比的仿真结果如图5所示。在4 V电源,27℃下,PSRR 达到-109 dB(10 Hz),和 -64 dB(10 kHz)。

4 结 论

图5 电源抑制比Fig.5 Power supply rejection raio

文中通过结合电压放大器,和带隙基准核心电路,设计出了高PSRR的带隙基准电路,可以有效减小电源噪声对带隙基准电压的影响。通过调节电阻来调节正温度系数的电压,使电路在不同工艺下得到低温度系数的基准电压。该电路具有-109 dB(10 Hz)的低频电源抑制比,5.6×10-6V/℃以下温度系数,最低工作电压为2.2 V。本电路可以广泛用在模数、数模转换电路,模拟偏置电路中,具有较高的实用价值。

[1]吴宗桂,邓爱枝,秦水介,等.一种具有高电源抑制比的带隙基准电压源[J].微电子学,2009,39(4):500-502.WU Zong-gui,DENG Ai-zhi,QIN Shui-jie,et al.A bandgap voltage reference with high power supply rejection ratio[J].Microelectronics,2009,39(4):500-502.

[2]汪宁,魏同立.一种具有高电源抑制比的低功耗CMOS带隙基准电压源[J].微电子学,2004,34(3):331-333.WANG Ning,WEI Tong-li.A low-power high PSRR CMOS bandgap voltage reference[J].Microelectronics,2004,34(3):331-333.

[3]韩荆宇,杨兵.一种高电源抑制的基准源的设计[J].电子设计工程,2011,19(7):169-171.HANJing-yu,YANGBing.Design of ahigh PSRRreference[J].Electronic Design Engineering,2011,19(7):169-171.

[4]张彬,冯全源.一种高电源抑制比带隙基准源[J].微电子学,2010,40(1):59-61.ZHANG Bin,FENG Quan-yuan.A high PSRR bandgap reference circuit[J].Microelectronics,2010,40(1):59-61.

[5]吴志明,黄颖,吕坚,等.高电源抑制比的CMOS带隙基准电压源[J].电子科技大学学报,2008,37(3):454-456.WU Zhi-ming,HUANG Ying,LV Jian,et al.High PSRR COMSbandgap voltage reference[J].Journal of University of Electronic Science and Technology of China,2008,37 (3):454-456.

[6]Gray PR, Hurst PJ, Lewis SH,et al.Analysis and design of analog integrated circuits[M].New York:Wiley,2001.

[7]Behzad Razavi.Design of analog CMOSintegrated circuit[M].McGraw.Hill,2001.

[8]Phillp E.Allen,Douglas R.Holberg.CMOS Analog Circuit Design[M].New York:Oxford,2002.

[9]Tham K M.Nagaraj K.A low supply voltage high PSRR voltage reference in CMOS press[J].IEEE J Sol Sta Circ,1995,30(5):586-590.