一种数字量的安全输入/输出模块的设计与实现

陈海燕,穆建成,马连川

(1.北京交通大学 轨道交通控制与安全国家重点实验室,北京 100044;2.铁道部 科技司,北京 100844)

安全计算机作为主要技术手段是保障轨道交通信号设备安全的基础设备。目前,我国铁路的安全计算机系统多采用3取2、2取2乘2的冗余结构[1]。为了提高系统的安全性和可扩展性,安全计算机向分布式结构发展,采用基于可编程逻辑实现时钟级同步的2取2结构安全I/O模块的设计方法,能缩短安全响应时间,使用可编程逻辑和硬件描述语言VHDL实现安全I/O模块,能避免通用MCU或CPU实现时钟级同步安全I/O模块所遇到的问题,且有设计周期短、开发费用低、风险小等优点。

1 安全I/O的设计与实现

1.1 安全I/O的结构与功能

本文针对可扩展的安全计算机平台,提出了一种基于FPGA的智能安全I/O模块的设计方案。安全I/O模块是以硬件逻辑保证平台与应用之间的数据传输安全。

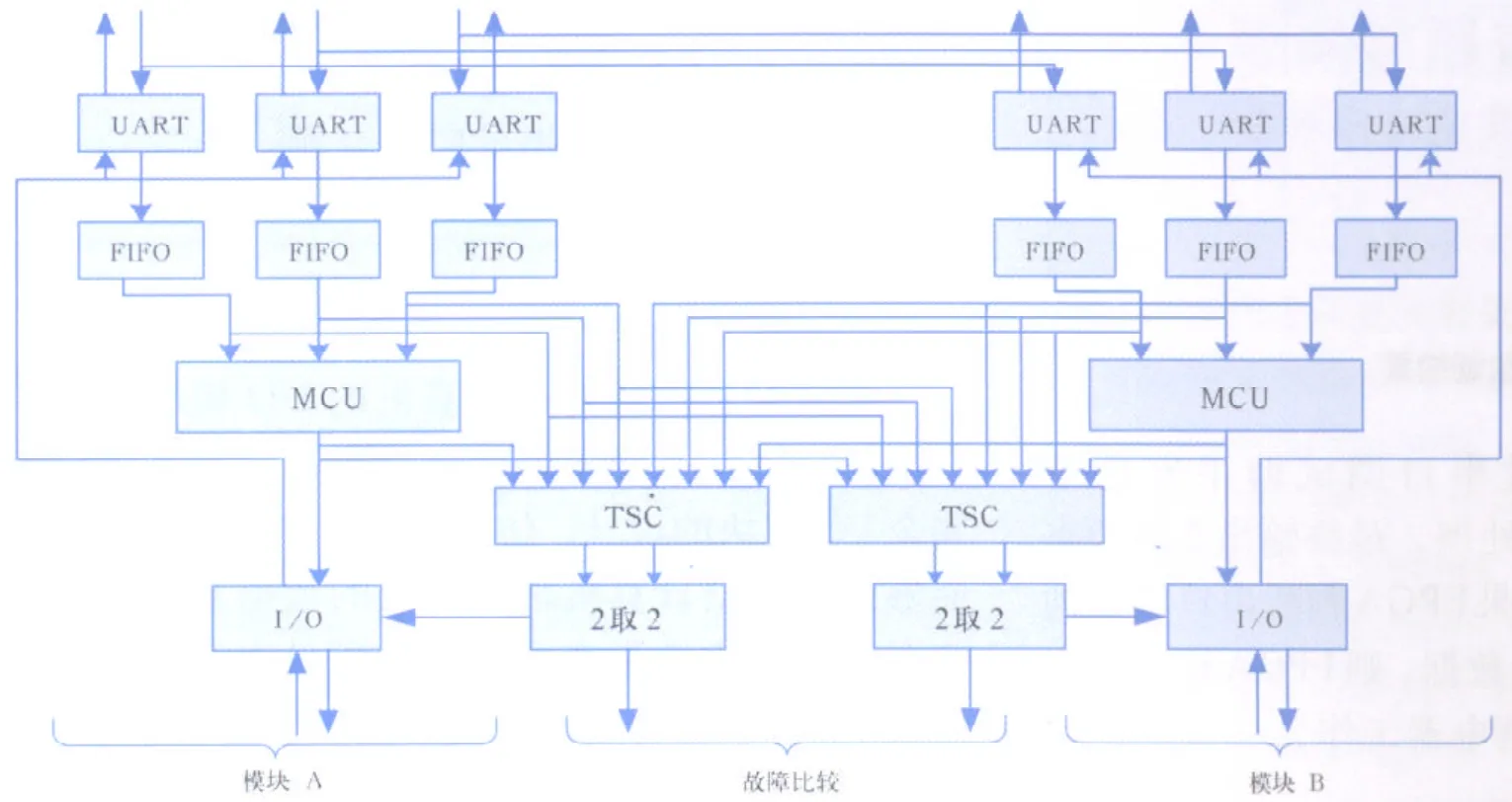

安全I/O模块主要是由2个完全相同的模块A、B和一个故障比较器组成。安全主机输出的数据传送到安全I/O模块中,分别在2个模块中完成3取2的表决运算,保证安全I/O模块的可靠性。在2个模块之间,利用比较电路实现2取2故障检测,保证模块的安全性。当比较器输入一致时,安全I/O模块输出周期性的脉冲。当比较器输出不一致时,I/O模块输出固定的0或者1,作为安全侧的输出。安全I/O模块将安全主机通过通信总线输出的数据转换为数字量安全输出,同时也可以将外部设备输入的数字量通过通信总线传输到安全主机。

FPGA主要由发送/接收部分(UART),存储部分(FIFO),微控制单元(MCU),接口部分(I/O),完全自校验电路(TSC),故障检测部分(2取2)组成。具体原理框图见图1。

图1 安全I/O原理框图

各个部分功能如下:

(1) UART:完成数据并/串之间的转换。

(2) FIFO:存储处理转化完的数据,供MCU读取。

(3) MCU:完成3取2的表决运算,控制数据传输的方向。

(4) I/O:在允许信号开放的情况下完成数据的读写操作。

(5) TSC:将待比较的数据转化为2比特数据输出。

(6) 2取2:监测MCU所有数据的输入/输出,完成2取2表决,实现故障安全原则。

1.2 FPGA逻辑仿真

利用硬件描述语言VHDL对FPGA的各个模块进行描述,然后通过顶层文件将所有模块连接在一起,仿真结果如图2。

图2 仿真结果

1.3 基于PSL的断言验证

(1)断言方案

安全I/O模块较多且与安全相关,因此采用基于硬件特性描述语言(PSL)的断言验证,不仅可以加速整个验证工作的速度,而且能够保证设计正确性。根据安全I/O模块内部各子模块性质、功能、设计方法和模块间信号传递的原则,详细设计了验证方案如表1。验证内容涉及到数据传输、存储器读写、状态转换、数据比较及模块间通信等。

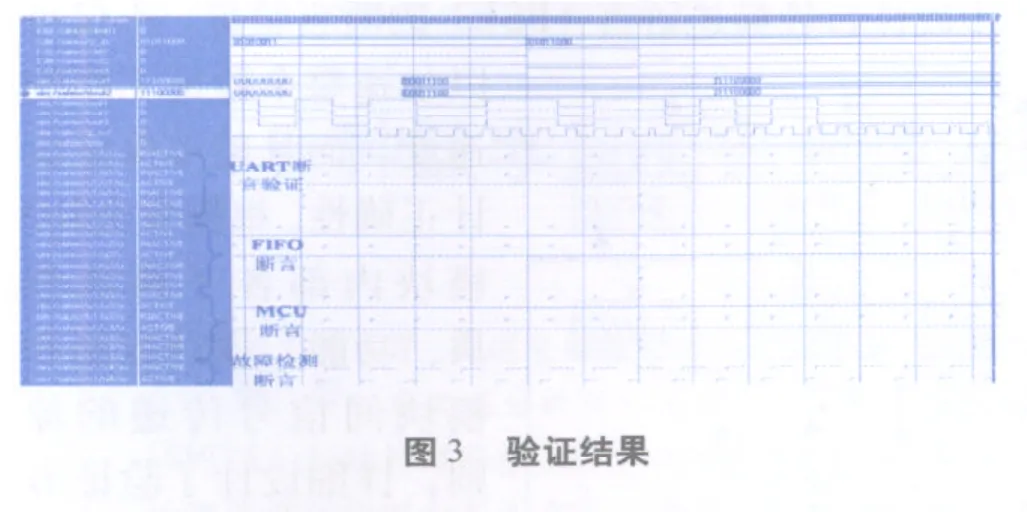

(2)验证结果

将表1中每个断言方案用PSL语句描述,并嵌入到模块的VHDL语句中,软件自动完成验证。验证结果如图3,由图可知每个断言都正确,从而有效的验证了安全I/O模块设计的正确性。

表1 安全I/O硬件设计的断言验证方案

1.4 原型实现

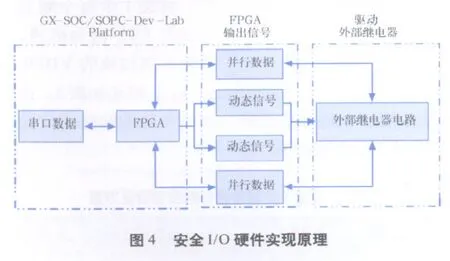

在电子设计自动化(EDA)开发实验平台上实现了安全I/O模块的硬件电路,如图4。运行EDA软件,将编译好的VHDL程序代码下载到FPGA中。

图3 验证结果

3组串口数据通过串口调试助手发送给FPGA,FPGA经过逻辑处理,最终输出2组动态信号和2组并行数据。如果FPGA判断串口调试助手输入的3组数据为安全数据,则FPGA输出的周期性脉冲信号驱动外部继电器工作。

图4 安全I/O硬件实现原理

长时间稳定性测试表明安全I/O模块的正确性和安全性。安全性测试时,人为使安全I/O模块中的模块A、B输出的比较数据不一致,安全I/O模块能够正确地使输出导向安全侧。

2 结束语

本文对可扩展安全计算机的I/O模块进行了专门的设计,完成了基于可编程逻辑时钟级同步安全I/O模块的设计、仿真、验证和实现。该模块能够保证安全计算机输入输出的数据和外部设备交互的高可靠性和高安全性,所付出的硬件和软件成本较低,具有较好的实用性,能推广到其它安全系统。

[1]马连川,高倍力.一种高安全容错控制计算机的设计与实现[J]. 中国安全科学学报,2004(8):101-l05.

[2]员春欣. 铁路信号容错技术[M]. 中国铁道出版社,1997.