90 nm CMOS工艺下p+深阱掺杂浓度对电荷共享的影响*

刘凡宇 刘衡竹 刘必慰 梁 斌 陈建军

(国防科技大学计算机学院微电子与微处理器研究所,长沙 410073)(2010年4月15日收到;2010年7月24日收到修改稿)

90 nm CMOS工艺下p+深阱掺杂浓度对电荷共享的影响*

刘凡宇 刘衡竹 刘必慰 梁 斌 陈建军

(国防科技大学计算机学院微电子与微处理器研究所,长沙 410073)(2010年4月15日收到;2010年7月24日收到修改稿)

基于3维TCAD器件模拟,研究了90 nm CMOS双阱工艺下p+深阱掺杂对电荷共享的影响.研究结果表明:改变p+深阱的掺杂浓度对PMOS管之间的电荷共享的影响要远大于NMOS管;通过增加p+深阱的掺杂浓度可以有效抑制PMOS管之间的电荷共享.这一结论可用于指导电荷共享的加固.

电荷共享,单粒子效应,p+深阱掺杂,双极晶体管效应

PACS:61.80.Jh,61.72.U - ,85.30.De,87.64.Aa

1.引 言

当辐射环境中的高能粒子轰击半导体器件灵敏区时将会引起单粒子效应(single event effect,SEE)[1,2]. 长期以来,国内外学者对单粒子效应进行了大量深入研究[3—7]:Levinson等结合模拟和实验,发现质子诱导的单粒子闩锁(single event latchup,SEL)与 单 粒 子 翻 转 (single event upset,SEU)的机理有很大不同;Schrimpf等通过准确描述大量单个粒子反应的方法准确预测了单粒子效应的软错误率;刘征等[7]采用 TCAD模拟发现深亚微米下双极晶体管效应在单管单粒子瞬变(single event transient,SET)电流脉冲中占主要成分.这些研究对抗辐照加固有重要的指导意义.

随着工艺尺寸的不断缩小,单粒子引起的电荷共享问题变得越来越严重,已经成为了国际上备受关注的可靠性问题[8].电荷共享 (charge sharing)是指单粒子轰击产生的电荷同时被多个敏感节点收集.电荷共享能导致系统的软错误率增加,加大抗辐照加固的难度[9].文献[10]研究了双阱工艺下器件距离、粒子的LET以及晶体管类型对电荷共享的影响,并用激光第一次实现了电荷共享实验.文献[11]通过3维 TCAD模拟发现130nm CMOS双阱工艺下温度的升高会导致电荷共享加重,进而导致 SRAM单元MBU阈值降低.文献[12]通过数值模拟得出,深亚微米下电荷共享的机理主要包括漂移、扩散和双极晶体管效应.

p+深阱掺杂浓度对电荷共享的影响目前还没有相关研究.有研究证实,重掺杂的p+深阱可以提高SRAM 单元的 SEU翻转阈值[13].通常,p+深阱对器件的I-V特性影响不大,却能有效减少衬底对阱电势影响[14].而阱电势又是影响漂移、扩散和双极晶体管效应最重要的因素.因此,通过研究不同p+深阱掺杂浓度下的电荷共享的变化趋势,有助于我们通过改变p+深阱掺杂浓度达到抑制电荷共享的目的.

本文基于90 nm CMOS双阱工艺,在不同的p+深阱掺杂浓度下进行了 TCAD 3维器件模拟,分别研究了p+深阱掺杂浓度对 PMOS管之间以及对NMOS管之间电荷共享的影响,发现 p+深阱掺杂浓度对电荷共享的影响主要是增大或减小衬底电荷收集,进而增强或减弱双极晶体管效应.这对于电荷共享的建模和加固具有重要的指导作用.

2.模拟设置

2.1.TCAD模型校准

模拟中使用了两种电路结构:1)两个输入为“0”反相器:两NMOS漏端相邻并采用3维器件模型,而两PMOS管采用电路模型,如图1所示,2)两个输入“1”反相器:两 PMOS漏端相邻并采用3维器件模型,而两NMOS管采用电路模型.这两种电路结构都广泛地存在于各种电路设计中.器件模型的p阱杂质为硼,而 n阱杂质为砷.通过调整漏轻掺杂(LDD)浓度、阈值电压(VT)注入和源漏掺杂的浓度等工艺参数,对NMOS和PMOS器件模型进行了工艺校准.该模型获得了与90nm CMOS双阱工艺相一致的电流电压特性曲线(Ids-Vds),如图2所示.

图1 电荷共享模拟使用的NMOS管器件结构

2.2.模拟建立

模拟中,我们采用 Synopsys公司的 Sentaurus TCAD构建了3维器件模型.NMOS管和PMOS管的尺寸分别为:Wn∶Ln=200 nm∶90 nm 和 Wp∶Lp=480 nm∶90 nm.管子间距为 140 nm,阱接触距NMOS和PMOS的距离为280nm,使用STI隔离两个晶体管.工作电压设置为1.2 V.

重离子轰击的 LET值为10 MeV·cm2/mg,并在轨迹上保持不变.粒子轨迹的深度和半径分别为5 μm 和 0.05 μm. 这与 SRIM(stopping and ranges of ions in matter)软件得到的Cl离子入射硅的辐射参数相当.假定粒子轰击的位置为漏极的中心,且垂直轰击器件结构的表面.

图2 90 nm CMOS工艺校准获得的ID-VD曲线 (a)NMOS;(b)PMOS

使用的物理模型包括:1)Fermi-Dirac统计;2)禁带变窄模型;3)掺杂相关的SRH复合和Auger复合;4)掺杂、电场和载流子浓度对迁移率的影响;5)轰击的重离子是采用 Gaussian分布建模,且Gaussian时序分布有0.25 ps的延迟;6)流体动力学模型用来模拟载流子输运.如果没有其他特别指定,其他的模型和参数为Sentaurus TCAD默认.

在混合模拟中,使用的 SPICE集约模型是BSIM3V3.晶体管的尺寸与器件模型一样.其他重要的尺寸(如源区/漏区面积,p阱接触面积,p阱接触与主器件的距离等)是由版图规则设定.

下面的讨论中,我们将使用文献[12]中定义的概念.直接被粒子轰击的器件称为主器件,而发生电荷共享的器件称为从器件.将校准的p+深阱掺杂浓度作为基准,然后改变掺杂浓度的峰值,进行模拟并比较结果.表1给出了模拟中使用的最大和最小p+深阱掺杂浓度峰值.

所有的模拟都是在16核心128G内存的高性能服务器上运行的.整个器件模拟的面积为10 μm ×10 μm ×5 μm,且器件模型包含 100,000—150,000个网格点.8个线程的器件模拟的平均时间大约为1天.

表1 电荷共享模拟中使用的p+深阱浓度值

3.模拟结果及分析

3.1.NMOS

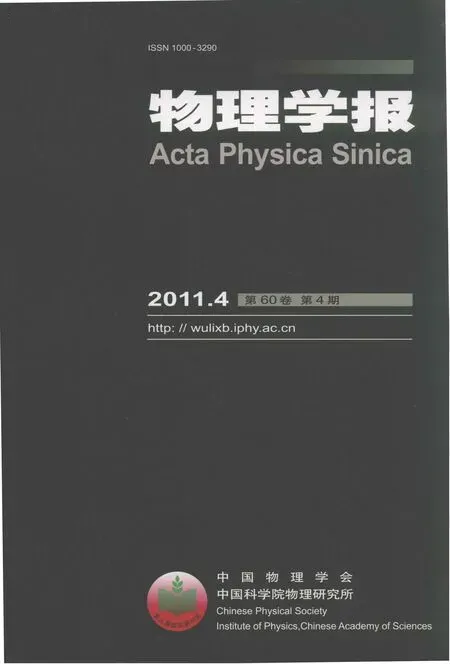

对NMOS而言,图3显示了在不同p+深阱掺杂浓度下主NMOS的漏端电流.图4显示了不同p+深阱掺杂浓度下从NMOS的漏端和源端电流.

p+深阱掺杂浓度从 5×1017cm-3增大到5×1018cm-3,主NMOS电荷的收集变化很小,如图3所示.比较图3和图4(a),p+深阱掺杂浓度的变化对从NMOS漏端电荷收集的影响要略大于主NMOS.

图3 不同p+深阱掺杂浓度下主NMOS漏端电流(Active Drain,即主器件漏极;Passive Drain,即从器件漏极;Active Source,即主器件源极;Passive Source即从器件源极)

3.2.PMOS

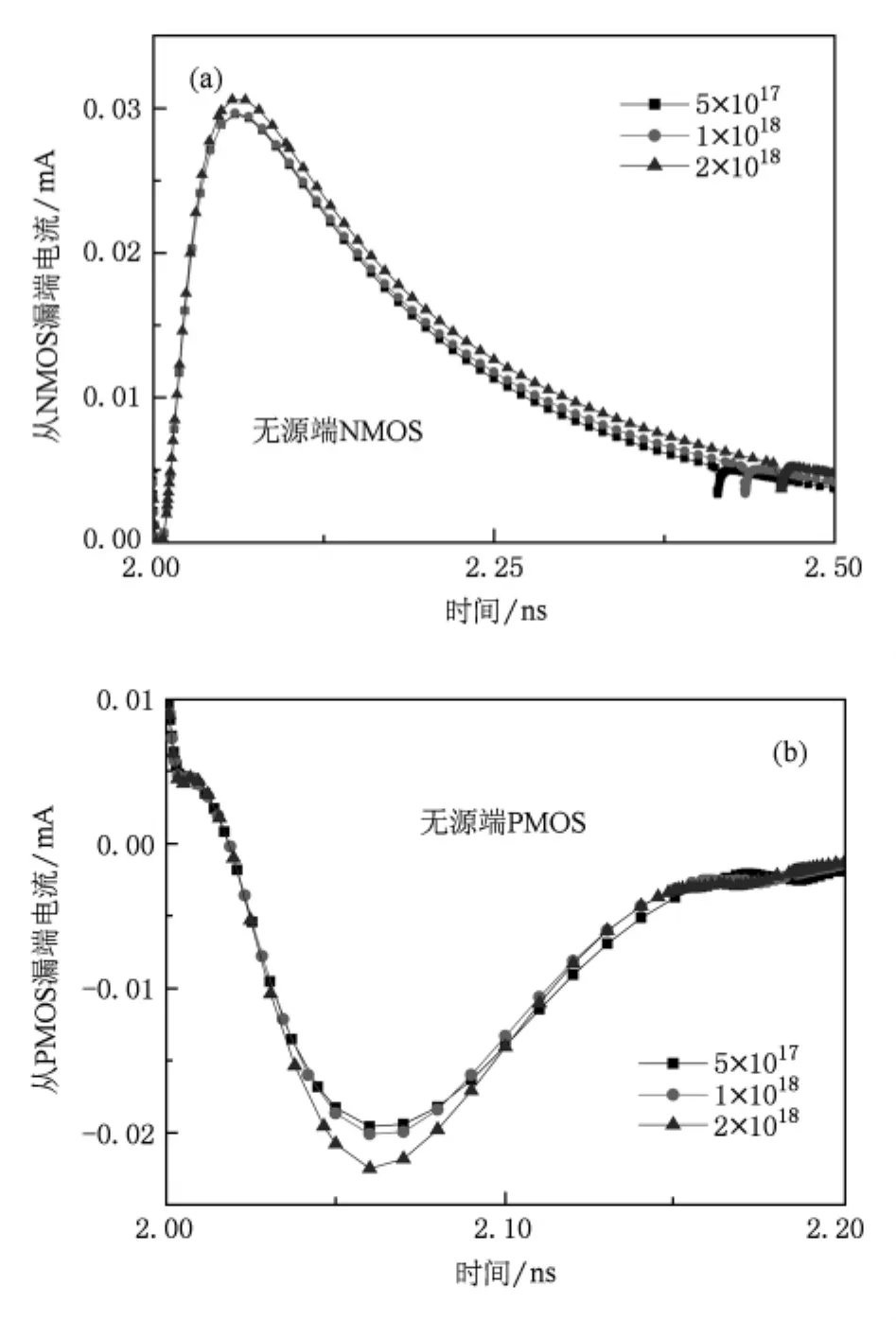

对PMOS而言,图5显示了不同p+深阱掺杂浓度下主PMOS的漏端电流.不同p+深阱掺杂浓度下从PMOS的漏端和源端电流则如图6所示.

图4 不同p+深阱掺杂浓度下从NMOS漏端和源端电流 (a)漏端;(b)源端

图5 不同p+深阱掺杂浓度下主PMOS漏端电流

根据图3和图5,p+深阱的掺杂浓度对主PMOS漏端电流的影响较主NMOS大.对主PMOS漏结而言,随着p+深阱的掺杂浓度的增加,电流脉冲持续时间减少,如果采用国际上通用的半高宽(电流峰值的一半)作为电流脉冲宽度,则当p+深阱掺杂浓度从5×1017cm-3增大到5×1018cm-3时,电流脉冲宽度从0.22 ns减小到0.14 ns,约降低36%;对从 PMOS漏结而言,漏端和源端的电流峰值和持续时间都降低,故漏端收集的电荷和源端注入n阱的电荷也降低.当 p+深阱掺杂浓度从5×1017cm-3增大到5×1018cm-3时,漏端收集的电荷从11.1 fC减少到3.62fC,约降低67%;源端注入n阱的电荷从14.8 fC减少到3.76 fC,约降低74.6%.总之,p+深阱掺杂浓度的变化对PMOS电荷共享的影响要远大于NMOS.

图6 不同p+深阱掺杂浓度下从PMOS漏端和源端电流 (a)漏端;(b)源端

4.讨 论

影响电荷共享的机理主要有两个:一是漂移扩散;二是双极晶体管效应.区分掺杂对这两种机理的影响是重要的.前人的研究证实[12],NMOS的电荷共享机理主要是扩散,而PMOS则主要是双极晶体管效应.从电离轨迹到从器件漏极附近的电荷扩散几乎不受p+深阱掺杂的影响;但衬底的电荷收集显著地受到p+深阱浓度的影响,进而影响阱电势扰动,从而对双极晶体管效应产生影响.下面我们将从理论上探讨p+深阱对电荷共享的影响.

4.1.对电荷产生的影响

杂质浓度对电荷产生的影响主要是禁带变窄.杂质浓度与禁带变窄的关系为[15]

其中,Eref和 Nref是材料参数,Oldslotboom模型默认为 9.0 ×10-3eV 和 1.0 ×1017cm-3,Ntot是掺杂浓度.每产生一对电子空穴需要能量ε为[16]

故p+深阱掺杂浓度从5×1017cm-3增大到5×1018cm-3,ε从3.51 eV减小到3.35 eV,约降低4.6%.p+深阱掺杂的改变对电荷产生的影响可以忽略.

图7 PMOS和NMOS的垂直剖面图 (a)PMOS管的n+-p-p+-p-结构;(b)NMOS管的 p+-n-p+-p-结构

4.2.对PMOS电荷共享的影响

对于PMOS,P漏、n阱、p+深阱和衬底构成 p+-N-p+-p-结构,该结构由两个pn结和一个浓度结构成,如图7(a)所示.重离子轰击前,P漏电势为低电平,n阱接高电平,衬底接地.根据文献 [17,18],重离子轰击主PMOS后将在其轨迹上发生漏斗收集过程,这个过程与电势分布有关:电离的电子将向高电势漂移,空穴将向低电势漂移.因此,n阱将收集电子,而衬底和 P漏将收集空穴.又根据文献[17,19],衬底浓度越高,其与阱形成的结耗尽区宽度越窄,电荷收集也越少.对于 p+-n-p+-p-结构,增大p+深阱浓度,相当于增大衬底浓度.因为 n阱掺杂浓度为1×1017cm-3,p+深阱 -n阱结为 pn结,所以当 p+深阱浓度从 5×1017cm-3增大到 5×1018cm-3,n阱 -p+深阱结耗尽区明显变窄,因而漏斗收集过程中衬底对空穴的收集变少,n阱对电子收集变少,即衬底对电子收集增多[17].图8显示了重离子轰击50ps后垂直从PMOS漏极中心方向的电子和空穴的浓度.随着 p+深阱浓度增大,n阱内电子浓度降低.图9显示了不同 p+深阱掺杂浓度下NMOS和PMOS的衬底收集的电子空穴量.对PMOS而言,当 p+深阱掺杂浓度从5×1017cm-3增大到5×1018cm-3时,衬底收集的电子从158 fC增加到211 fC,约增加33.5%,而空穴从475 fC减小到390 fC,约降低17.9%.因此,对 PMOS而言,随着 p+深阱掺杂浓度的增加,衬底收集的电子增多,空穴变少.

图8 重离子轰击50 ps后,三种 p+深阱掺杂浓度下,垂直从PMOS漏极中心方向的电子和空穴浓度 (a)电子;(b)空穴

随着p+深阱浓度增加,衬底收集空穴变少、n阱内电子浓度降低,n阱的电势扰动将变小[19],双极晶体管效应也就变弱了,如图10所示.下面我们将讨论p+深阱掺杂浓度对PMOS双极晶体管效应的影响是主要的.双极晶体管效应,指重离子的轰击引起阱电势的扰动,导致开启寄生双极型晶体管,从而使源区向阱区注入少数载流子(对 NMOS而言注入的是电子,对PMOS而言是空穴),增大漏极电荷的收集.为了分析p+深阱掺杂对双极晶体管效应的影响,在原模拟电路结构的基础上,去掉从器件的源注入和栅极,这样从器件就变成一个二极管.目前国际上很多学者都采用无源端器件来研究电荷收集中的双极晶体管效应[7,10—12]. 无源端器件与有源端器件相比,没有横向寄生晶体管,因此去除了双极晶体管效应.

图9 NMOS和PMOS衬底收集的电子和空穴随p+深阱掺杂浓度的变化 (a)电子;(b)空穴

图10 重离子轰击50 ps后,不同 p+深阱掺杂浓度(5×1017cm-3,1×1018cm-3和 2×1018cm-3)下垂直从 PMOS的源极中心方向的电势

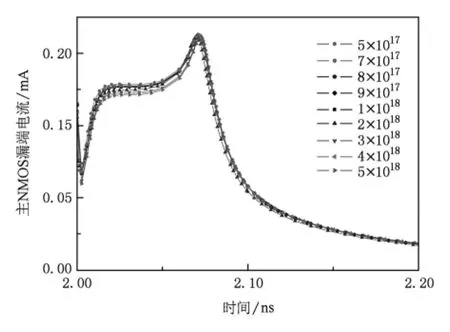

图11 不同 p+深阱掺杂浓度(5×1017cm-3,1×1018cm-3和2×1018cm-3)下无源端的从NMOS和从PMOS的漏端电流

图11(b)显示了无源端的从PMOS在三种p+深阱掺杂浓度下的漏端电流.比较图6和图11(b),随着 p+深阱浓度的变化,从 PMOS在有源端的情况下比无源端的情况下电流的变化要大得多.根据前面的分析,我们知道,无源端器件与有源端器件最大的区别是:有源端器件存在双极型晶体管效应.这就证实了 p+深阱掺杂浓度主要通过影响PMOS的双极晶体管效应来影响其电荷共享.n阱电势扰动降低,双极晶体管效应变小,故漏端电荷收集减少,而无源端的从PMOS由于去除了双极晶体管效应,因而从PMOS漏端电荷收集随p+深阱浓度变化不明显,如图12.

总之,增大p+深阱浓度,衬底收集电子增多、空穴减少,而n阱内电子浓度降低,从而导致n阱电势扰动减小,双极晶体管效应减弱,而PMOS电荷共享的主要机理是双极晶体管效应,所以从PMOS漏端收集电荷减少.

4.3.对NMOS电荷共享的影响

图12 在有源端和无源端情况下NMOS和PMOS漏端收集电荷随p+深阱浓度的变化

对于NMOS,N漏、p阱、p+深阱和衬底构成 n+-p-p+-p-结构,该结构由一个pn结和两个浓度结构成,如图7(b)所示.重离子轰击前,N漏电势为高电平,p阱和衬底接地.因此,大量电子将被N漏收集,而空穴大部分将被p阱接触收集,少部分被衬底收集[17]. 同样根据文献[17,18],由于衬底掺杂浓度为 1×1016cm-3,p阱掺杂浓度为 1 ×1018cm-3,所以当 p+深阱浓度从 5×1017cm-3增大到 5×1018cm-3,两个浓度结的耗尽区变化很小;又根据文献[19],p+深阱浓度对 NMOS 的 n+-p-p+-p-结构的电场扰动很小,因此p+深阱浓度变化对衬底电荷收集影响不大,如图9所示.对NMOS而言,当p+深阱掺杂浓度从 5×1017cm-3增大到 5×1018cm-3时,衬底收集的电子从 410 fC减少到 397 fC,约降低3.2%,而空穴从 324 fC减少到 315 fC,约降低2.8%.因此,p+深阱浓度对 NMOS衬底电子空穴的收集的影响基本可以忽略.

图13 重离子轰击50 ps后,不同p+深阱掺杂浓度下垂直从NMOS的源极中心方向的电势

随着p+深阱浓度的增加,NMOS衬底对电子空穴的收集影响不大,p阱内电子和空穴的浓度变化也不大,p阱电势扰动也不大[19].图13给出了三种p+深阱掺杂浓度下垂直从PMOS的源极中心方向的电势.下面我们说明p+深阱掺杂浓度对从轰击轨迹上扩散到被从NMOS漏端收集的电荷没有影响.图11(a)显示了无源端的从NMOS在三种p+深阱掺杂浓度下的漏端电流.比较图4和图11(a),在有源端和无源端两种情况下,从NMOS电荷收集变化不大.又由图12知,有源端和无源端的从 NMOS漏端电荷收集随着p+深阱掺杂浓度的增加变化都不大.且NMOS电荷共享的主要机制是扩散,因此p+深阱掺杂浓度对电荷扩散影响不大,进而对NMOS电荷共享影响也不大.综上所述,p+深阱掺杂浓度改变基本不会改变NMOS衬底的电荷收集,因而对p阱电势扰动也很小,加之p+深阱掺杂对电荷扩散没有影响,所以p+深阱掺杂浓度对NMOS的电荷共享影响很小.

5.结 论

本文研究了90nm CMOS双阱工艺下p+深阱掺杂浓度对电荷共享的影响.通过TCAD 3维模拟,发现p+深阱的掺杂对PMOS电荷共享的影响比NMOS大得多,这是因为p+深阱掺杂会影响衬底电荷收集,进而影响双极晶体管效应.更大的p+深阱掺杂浓度将会有更大的衬底电子收集、更小的空穴收集,从而导致更弱的双极晶体管效应.因此,为了抑制PMOS的电荷共享,我们可以适当增大p+深阱掺杂浓度.

目前电荷共享的加固主要通过版图技术来实现,如添加保护环,增大阱接触等,这些技术都增加了面积和功耗[18].调整 p+深阱掺杂不仅解决了这一难题,同时又不使工艺变得复杂.3维数值模拟可以分析p+深阱掺杂对电荷共享的影响机理,还可以利用该结论指导电荷共享的加固,为宇航级集成电路的设计和制造提供理论支持.

[1] J derstr m H,Murin Y,Babain Y,Chubarov M,Pljuschev V,Zubkov M,Nomokonov P,Olsson N,Blomgren J,Tippawan U,Westerberg L,Golubev P,Jakobsson B,Gerén L,Tegnér P E,Zartova I, BudzanowskiA, Czech B, Skwirczynska I,Kondratiev V,Tang H H K,Aichelin J,Watanabe Y,Gudima K K 2008 Phys.Rev.C 77 2813

[2] Dodd P E,Massengill L W 2003 IEEE Trans.Nucl.Sci.50 583

[3] Levinson J,Akkerman A,Victoria M,Hass M,Ilberg D,Alurralde M,Henneck R,Lifshitz Y 1993 Appl.Phys.Lett.63 2952

[4] Cellere G,Paccagnella A,Visconti A,Bonanomi M 2004 Appl.Phys.Lett.85 485

[5] Schrimpf R D,Weller R A, Marcus H M, ReedR A,Massengill L W 2007 Nucl.Instr.and Meth.B 261 1133

[6] Zhang K Y,Guo H X,Luo Y H,He B P,Yao Z B,Zhang F Q,Wang Y M 2009 Acta Phys.Sin.58 8651(in Chinese)[张科营、郭红霞、罗尹虹、何宝平、姚志斌、张凤祁、王园明 2009物理学报 58 8651]

[7] Liu Z,Chen S M,Liang B,Liu B W,Zhao Z Y 2010 Acta Phys.Sin.59 649(in Chinese)[刘 征、陈书明、梁 斌、刘必慰、赵振宇2010物理学报 59 649]

[8] Olson B D,Ball D R,Warren K M,Massengill L W,Haddad N F,Doyle S E,McMorrow D 2005 IEEE Trans.Nucl.Sci.52 2132

[9] Massengill L W,Amusan O A,Dasgupta S,Sternberg A L,Black J D,Witulski A F,Bhuva B L,Alles M L 2007 InternationalConference on Integrated Circuit Design and Technology 213—216

[10] Amusan O A,Casey M C,Bhuva B L,McMorrow D,Gadlage M J,Melinger J S,Massengill L W 2009 IEEE Trans.Nucl.Sci.56 3065

[11] Liu B W,Chen S M,Liang B,Liu Z,Zhao Z Y 2009 IEEE Trans.Nucl.Sci.56 2473

[12] Amusan O A,Witulski A F,Massengill L W,Bhuva B L,Fleming P R,Alles M L,Sternberg A L,Black J D,Schrimpf R D 2006 IEEE Trans.Nucl.Sci.53 3253

[13] Saxena P K,Bhat N 2003 Solid State Electronics 47 661

[14] Hsu S,Fiez T S,Mayaram K 2005 IEEE Trans.Elec.Dev 52 1880

[15] Synopsys Corporation 2009 Sentaurus Device User Guide Version A-2009.06-SP2.

[16] Emery F E,Rabson T A 1965 Phys.Rev.140 2089

[17] Dussault H,Howard J W,Block R C,Pinto M R,Stapor W J,Knudson A R 1993 IEEE Trans.Nucl.Sci.40 1926

[18] Dodd P E,Sexton F W,Winokur P S 1994 IEEE Trans.Nucl.Sci.41 2005

[19] Hsieh C M,Murley P C,O’Brien R R 1981 IEEE Elec.Dev.Lett.EDL-2 103

[20] Amusan O A,Massengill L W,Baze M P,Bhuva B L,Witulski A F,Black J D,Balasubramanian A,Casey M C,Black D A,Ahlbin J R,Reed R A,McCurdy M W 2009 IEEE Transaction on Device and Materials Reliabilty 9 311

PACS:61.80.Jh,61.72.U - ,85.30.De,87.64.Aa

Effect of doping concentration in p+deep well on charge sharing in 90nm CMOS technology*

Liu Fan-Yu Liu Heng-Zhu Liu Bi-Wei Liang Bin Chen Jian-Jun

(Computer School,National University of Defense Technology,Changsha 410073,China)(Received 15 April 2010;revised manuscript received 24 July 2010)

This paper deals with the effect of doping concentration in p+deep well on charge sharing in 90nm dual well CMOS technology.TCAD simulation results show doping concentration in p+deep well has a more significant effect on charge sharing in PMOS tube than in NMOS tube.By increasing doping concentration of p+deep well appropriately,the charge sharing in PMOS can be restrained effectively,which is useful for reinforcing the charge sharing.

charge sharing,SEE,p+deep well doping concentration,bipolar amplification effect

*国家自然科学基金重点项目(批准号:60836004),国家自然科学基金(批准号:61006070)资助的课题.

E-mail:liufanyu986412@hotmail.com

*Project supported by the Key Program of National Natural Science Foundation of China(Grant No.60836004),the National Natural Science Foundation,China(Grant No.61006070).

E-mail:liufanyu986412@hotmail.com