基于FPGA的卫星数字频率信号处理关键技术研究与实现

罗来金,曾连荪

(上海海事大学 信息工程学院,上海 200135)

近年来FPGA以其硬件并行处理的高速性和可重配置性,在电子设计中得到了大规模的应用。伴随着制作工艺和不断进步及IP内核概念的出现,FPGA正在从传统的系统粘合逻辑应用转移到系统核心处理应用上来。

文中分析了传统频率信号处理方法的优缺点,采用ALTERA的Cyclone II系列FPGA完成某型卫星陀螺组合X、Y、Z轴方向的角速和温度传感器发送来的频率信号的测量与处理,并通过RS-422串口通信总线实现了与主控计算机的双向通信。相比于以往采用单片机、DSP等器件实现数字脉冲频率的测量及其数据处理,采用FPGA以及特定的算法来实现数字脉冲频率的测量及其数据处理,后者具有高速、高稳定度、高精度和高集成度的特点,不会出现程序跑飞的情况,满足航天系统对频率信号测量的特定要求。

1 频率测量方法分析[1]

1.1 测频法

测频法就是在确定的时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:Fx=Nx/Tw。该种测量方法会产生±1的计数误差,测试精度与计数器的记录值Nx有关,频率越高精度越大,因此该测量方法适用于高频信号的测量。

1.2 测周法

测周法需要有标准的数字基准时钟频率Fs,在待测信号的一个周期Tx内,记录标准信号的周期数Ns。则被测信号的频率为:Fx=Fs/Ns。该种测量方法Ns同样也会产生±1的计数误差,测试精度与计数器的记录值Ns及标准频率稳定度有关,适用于低频信号的测量。

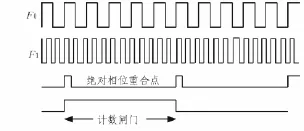

1.3 相检宽带测频

相位检测法利用两个频率之间的周期性规律来产生计数闸门,这种周期性规律就是两个频率的最小公倍数周期,如图1所示。

图1 相位检测法频率测量原理图Fig.1 Schematic diagram of phase detection frequency measurement

理论上在这样一个计数闸门时间段内对标准频率和被测频率的计数都不会存在±1的误差,没有时间误差,因此理论上精度无限高[2]。但实际上“绝对相位重合点”是不可能的,而且外加实际电路器件的延时,计数闸门也会存在相应的时间误差,导致实际测量精度与理论有一定的差距。在此基础上不少学者也提出并实现一些新的相位重合点检测技术,精度在一定程度上得到提高,但算法复杂。

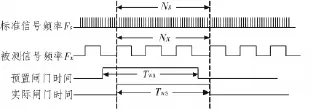

1.4 等精度测量法

等精度测量原理如下:在预置闸门信号的上升沿时不立即进行计数,而是等到被测信号脉冲的上升沿到来时开始计数,在闸门的下降沿到来时也不立即关闭计数,而是等到被测信号的上升沿到来时停止计数。等精度测频的原理图如图2所示。

图2 等精度测量原理Fig.2 Principle of equal precision measuring

误差分析如下:

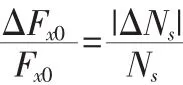

假设待测信号频率是Fx,标准信号频率是Fs,在实际闸门时间TWS内的计数值分别为Nx和Ns,则可得到下式:

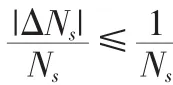

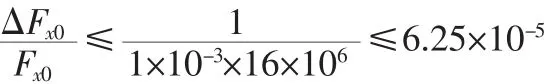

所以

由于待测信号Fx的计数时间是由它本身的上升沿控制的,所以在闸门时间内计数得到的Nx不存在误差,而误差产生只能是Ns带来的,在TWS内对标准信号Fs计数得到的Ns可能相差 1,即|△Ns|≤1,假设待测信号的准确值为 Fx0,则可得到下式:

所以

采用等精度法进行频率测量可以使得测量相对误差在6.25×10-5以内。

2 频率信号测量及处理系统

采用FPGA实现数字频率信号的测量及处理的系统结构如图3所示。

图3 系统框图Fig.3 Block diagram of system

该系统下位机主要包括:频率信号的测量、频率信号的计算、数据通信、同步信号的产生4部分,全部在一片FPGA芯片上实现。RS-422串口通信总线采用SN75174和SN75175分别作为传输线驱动器和传输线接收器。上位机采用MOXA公司的CP-132UL型RS-422卡,用VC++6.0提供的MScomm控件编写测试程序,实现了工控机和下位机的高速率双向通信。

2.1 频率测量模块

该部分主要包括预置闸门时间产生、闸门时间同步、计数器、数据锁存器、清零信号产生模块。其中关键是解决时序问题,为保证计数的稳定输出,需要在完成计数后进行锁存并输出,同时计数器清零,重新开始计数。如图4所示,在设计中利用预置闸门时间和实际闸门时间的“相位时差”完成清零信号的产生,产生必要的清零信号。

图4 清零信号的产生Fig.4 Clear signals generated

2.2 数据处理模块

数据处理是本系统实现的关键之一,本系统需要进行计算的过程比较多,主要包括多位的乘法、除法以及数值比较、定点数与32位浮点数之间的转换、32位浮点乘法,需要实现的数据处理过程顺序如下:

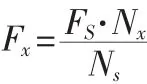

第一步:待测信号的频率计算。

其中Fs为标准信号频率16 MHz,Nx与Ns为计数器所得值。

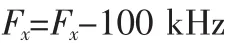

第二步:频率归一化。

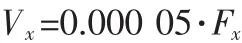

第三步:电压值计算。

第四步:角速度值计算。

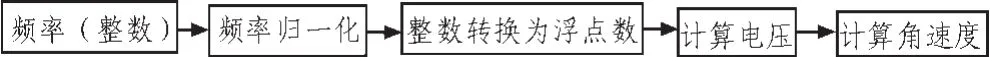

Wx要求为32位单精度浮点数,由于FGGA很难实现小数的乘法,所以需要转换成定点数或者浮点数乘法来实现[3]。在第二步和第三步之间进行定点数到32位浮点数转换,采用32位单精度浮点数实现电压值和角速度值的转换,实现框图如图5所示。

图5 FPGA数据处理方框图Fig.5 Block diagram of FPGA data processing

伴随着FPGA的发展,如今用它来实现定点数的乘除法是很方便,直接调用基本宏模块提供的定点数乘除法IP核,进行相应参数的设置即可实现[4]。并且有的FPGA芯片还可以提供32位甚至64位的浮点数乘法器。方案使用的FPGA芯片是Altera公司提供的CycloneⅡ系列,该系列芯片提供了32位单精度的浮点数乘法器的基本宏模块,利用其IP核及硬件乘法器可以加快产品的研发和提高系统的性能,因此在本模块中采用了定点乘法器、定点除法器、定点数到单精度浮点数转换等实用的IP核来解决系统中关键的运算模块,大大提高了系统数据处理的性能[5]。

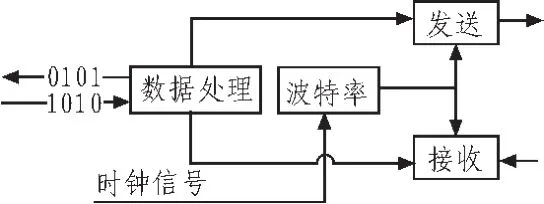

2.3 RS-422通信模块

频率信号采集系统需要与主控计算机进行通信,该系统中采用了RS-422串口通信总线。RS-422总线是一种单机发送、多机接收的单向、平衡传输规范,将传输速率提高到10 Mbit/s,克服了RS-232通信距离短、速率低的缺点,满足航天系统的特定要求[6]。下位机FPGA实现串口通信框图如图6所示。

图6 串口通信模块Fig.6 Serial communication module

该部分主要由波特率产生模块、发送与接收模块、数据处理模块组成。数据处理模块完成数据发送和接收缓冲、CRC-16校验及奇偶校验。波特率发生模块用于产生特定的时钟信号。接收和发送模块则完成数据的串行接收和串行发送。为了提高数据判决的准确性,采用16倍于波特率的时钟信号对接收和发送波形进行采样。

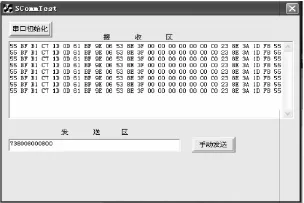

3 实验结果及分析

频率输入信号采用标准的信号发生器产生,同步信号输出用LED灯指示。如图7所示,将FPGA烧结文件下载到实验系统上。每当上位机用串口调试软件发送88请求命令(附带CRC-16校验码),FPGA系统就会以0X55作为帧头和帧尾,发送实时采集到的4组48位数据到上位机。

图7 串口通信调试Fig.7 Debugging of serial communication

该系统经过地面卫星测试实验环境中的长时间实验,表明基于FPGA的卫星数字频率处理系统工作稳定,成功实现了卫星数字频率信号的测量、处理、通信过程。

4 结 论

采用ALTERA公司的Cyclone II系列FPGA,使用VHDL语言编写FPGA代码实现了对某型卫星4路频率信号测量、数据处理、通信过程,频率测量精度达到1.562 5×10-5。相对于MCU、DSP,采用单片FPGA完成卫星频率信号的测量、处理和发送,具有低成本、低功耗、高速、高集成度、抗干扰的特点,具有无可比拟的优势。

随着FPGA技术和IP核技术的发展,今后可以采用速率更高,精度更高效的算法来实现频率信号的测量及处理,将SOC技术应用到现代电子系统中。

[1]National Instruments.Frequency measurements:How-to guide[EB/OL]. (2011-03-18).[2011-04-10].http://zone.ni.com/devzone/cda/tut/p/id/7111.

[2]王海,周渭,宣宗强.高精度频率测量技术及其实现[J].系统工程与电子技术,2008,30(5):981-983.

WANG Hai, ZHOU Wei, XUAN Zong-qiang.High accuracy frequency measurement scheme and its implementation[J].Systems Engineering and Electronics,2008,30(5):981-983.

[3]Lee B,Burgess N.Parameterisable floating-point operations on FPGA[J].Conference Record of The Thirty-sixth Asilomar Conference on Signals, Systems, and Computers,2002(2):1064-1068.

[4]Altera.CycloneⅡ Device Handbook,Section 1.CycloneⅡdevice family data sheet[EB/OL].(2008-02)[2011-04-23].http://www.altera.com.cn/literature/hb/cyc2/cyc2_cii5v1_01.pdf

[5]Altera.Floating-point megafunction user guide[EB/OL].(2011-05)[2011-05-23].http://www.altera.com.cn/literature/ug/ug_altfp_mfug.pdf.

[6]丁云霞,曾连荪.基于VC++6.0的RS-422串口通信设计[J].信息技术,2010(9):73-75.

DING Yun-xia,ZENG Lian-sun.RS-422 serial communication based on VC++6.0[J].Information Technology,2010(9):73-75.