基于FPGA的RS232/422多通道接口设计与实现

徐 智,张义涛

(1.中航工业直升机设计研究所,江西景德镇 333001;2.陆航驻景德镇地区代表室,江西景德镇 333000)

0 引言

RS232/422串口是目前最常用的一种工业标准,它具有技术成熟、性能可靠、操作简单等优点,在民用和军用航空领域被广泛应用。

传统的RS232/422总线接口大都采用专用的总线板卡,这种方案集成度低、成本高。当面对多设备时,就需要通过增加板卡数量来满足多设备的要求,故而增加了系统的体积和重量。为了在最小系统中实现多通道RS232/422总线的收发和降低占用CPU时间,笔者基于FPGA设计了多通道RS232/422总线接口,使多路信号的收发和处理变得灵活、有序。

1 技术方案

1.1 RS232/422 协议简介

基本的UART通信只需要两条信号线(RXD、TXD)就可以完成数据的相互通信,接收与发送的全双工形式,其中TXD是 UART的发送端,RXD是UART的接收端。UART基本特点是:在信号线上有两种状态,可分别用逻辑1(高电平)和逻辑0(低电平)来区分。在发送器空闲时,数据线应保持在逻辑高电平状态,发送器是通过发送起始位来开始一个字符的传送,起始位使数据线处于逻辑低电平状态,提示接收器数据开始传输,数据位一般为8位一个字节的数(也有6位、7位的情况),低位(LSB)在前,高位(MSB)在后,校验位一般用来判断接收的数据位有无错误,一般是奇偶校验,停止位在最后,用以标志UART一个字符传送的结束,它对应于逻辑1状态。

1.2 结构原理

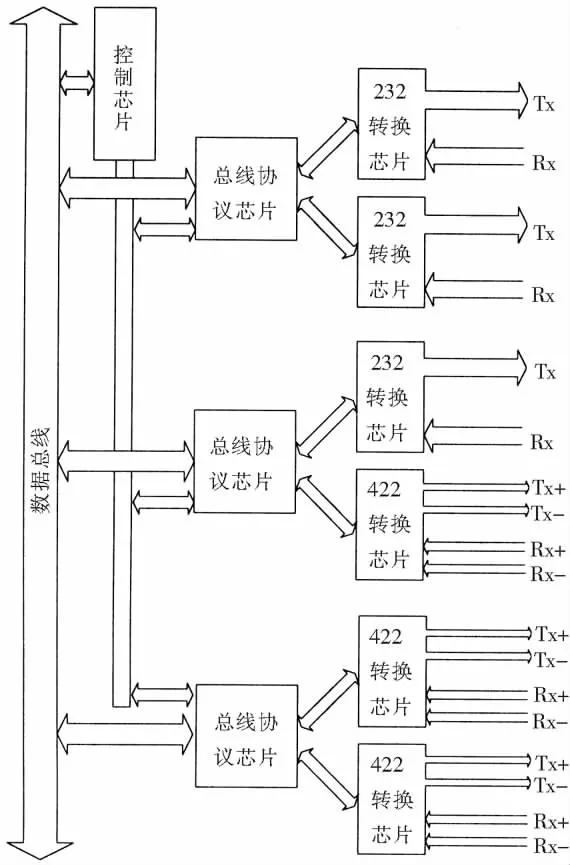

RS232/422总线是计算机与各任务设备之间进行数据交互的通道,完成数据信号的收发。它由控制芯片、总线协议芯片和电平转换芯片组成。控制芯片从数据总线接收来自CPU的数据指令,对总线协议芯片进行配置和逻辑控制。总线协议芯片接收完数据后,将中断信号和完整的数据信号发送给控制芯片。控制芯片通过数据总线将数据信号发送给CPU。它的结构原理如图1所示。

图1 接口结构原理图

1)总线协议芯片

总线协议芯片TL16C754是4通道,每通道有64B FIFO的UART,通过3个总线协议芯片可以构成12个通道的UART。在FIFO工作模式下,每通道的发送和接收FIFO深度可以设置,减少了CPU的中断/查询频率,提高了系统的效率。TL16C754输出LVTTL电平,对4个通道TX,RX进行电平转换,可以扩展成RS422或RS232口。在本接口电路中共选用了3片TL16C754来提供12路UART。

2)转换芯片

Max3033,Max3093是4路 RS422电平转换芯片。Max3033接收来自TL16C754的串行数据,转换成满足RS422协议的差分输出信号。Max3094接收外部的RS422差分输入信号,将信号转换成串行数据传输给TL16C754。本接口电路中共提供了8路RS422。

Max3232是2路全双工RS232电平转换芯片。Max3232接收来自TL16C754的串行数据,转换成满足RS232协议的串行输出信号;同时Max3232接收来自外部的RS232的串行输入信号,将信号转换成串行数据传输给TL16C754。本接口电路中共提供了6路RS232。

3)控制芯片

控制芯片实际上就是通过硬件描述语言[1],在可编程逻辑器件(FPGA)上设计实现的芯片。FPGA内部资源丰富,通过它能有效提高系统的集成度,缩小系统体积,降低成本。FPGA是RS232/422多通道接口电路的核心[2],任务是接收CPU的指令,对3片TL16C754协议芯片进行初始化,并将接收到的数据由CPU指定的通道输出。在接收到协议芯片的中断信号后,对中断源进行判断,提醒CPU到相应的通道接收新的总线数据。依据该设计原理,FPGA中提供了时钟发生模块、数据寄存器、地址寄存器、中断辨识寄存器以及控制逻辑转换的状态机。

2 多通道总线收发的实现

2.1 协议芯片的初始化

TL16C754的串行通道由控制寄存器 LCR、IER、DLL、DLM、MCR和FCR编程。这些控制字决定字符长度、停止位的个数、奇偶校验、波特率以及调制调解器接口。控制寄存器可以以任意顺序写入,但是IER必须最后一个写入,因为它控制中断。本系统中波特率设置为19200,系统工作在DMA模式1中。以设置通道A为例:

FPGA接收到数据总线上的配置字,依次配置DLL、DLH(除数锁存寄存器)、EFR(增强功能寄存器)、MCR(调制调节器控制寄存器)、TLR(触发等级寄存器)、FCR(FIFO控制寄存器)、LCR(线路控制寄存器)和IER(中断识别寄存器)。通过配置上述寄存器,可将串行通道设置为19200波特率,8位有效数据位,1位停止位,无奇偶校验。

2.2 发送/接收模块的设计

发送模块主要由发送FIFO缓存构成,由于协议芯片两端连接的总线传输速率不同,因此用发送FIFO作为数据缓存。各个通道都有64个字节长度的发送FIFO缓存结构。只要发送FIFO中有数据,它就通过发送逻辑模块发送出去,同时产生奇偶校验和停止位。通过TLR寄存器可以设置触发等级,当发送FIFO中空闲空间达到触发等级的条件时,TXRDY信号被协议芯片给出。在本系统中,各个通道的发送是通过CPU定时器分时发送的。

接收模块主要由接收FIFO缓存构成,由于协议芯片两端连接的总线传输速率不同,因此用接收FIFO作为数据缓存。每个通道的接收FIFO也是64字节的空间。通过TLR寄存器可以设置触发等级,当接收FIFO中接收到的数据达到触发等级时,RXRDY信号被协议芯片给出。

2.3 多通道的切换

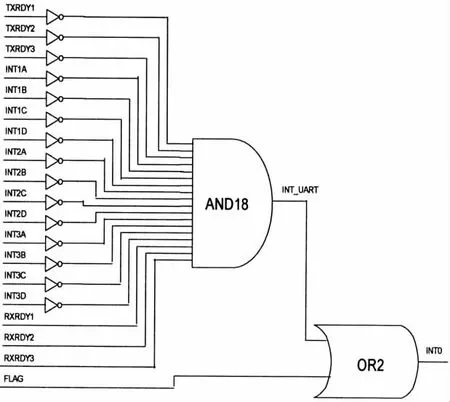

本系统中使用了3片协议芯片,每个协议芯片中有1个 TXRDY,1个 RXRDY和4个 INT信号。如图2所示,将18个信号与在一起,产生一个中断信号INT_UART,INT_UART和FLAG或在一起,产生中断信号INT0,INT0与CPU相连,取其下降沿为中断触发信号。如图2所示。

图2 中断信号

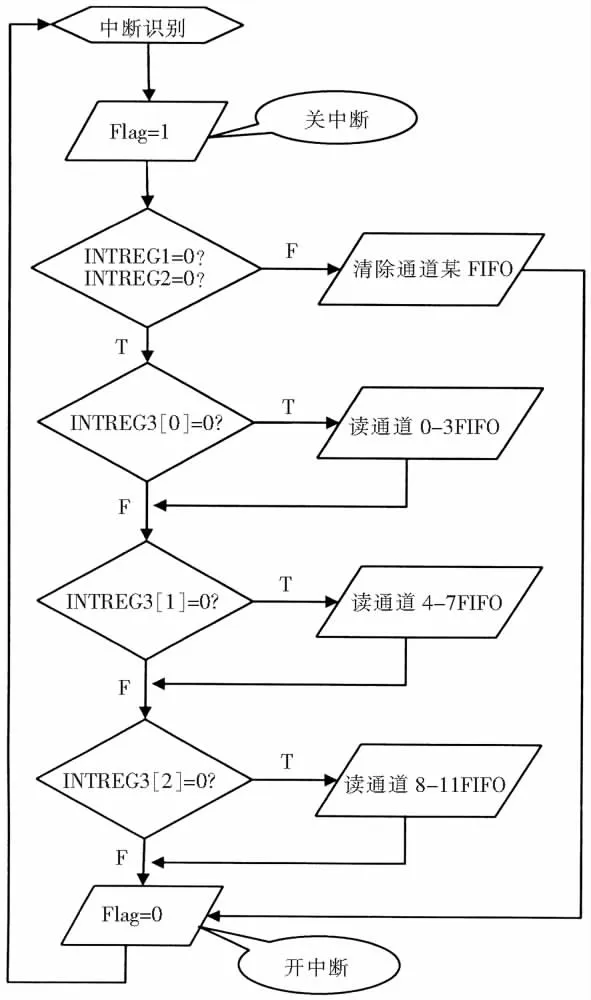

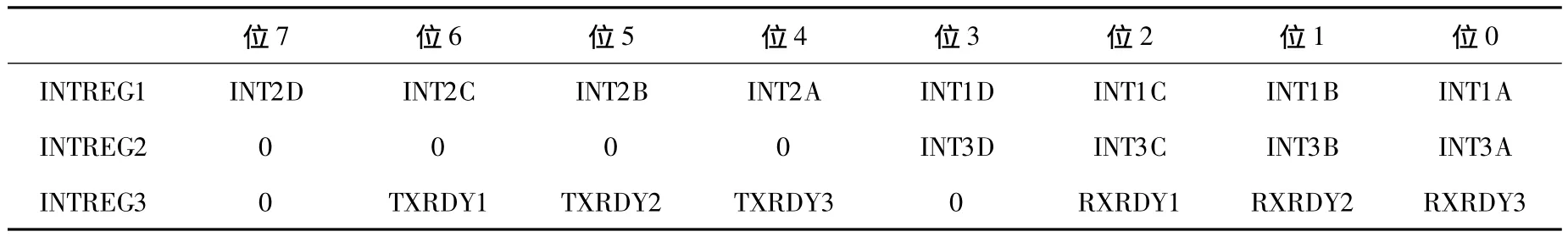

当CPU接收到INT0的中断信号后,CPU将FLAG信号置高,从而屏蔽18个中断源。此时,CPU进入到中断服务程序。在中断服务程序中,CPU读取FPGA提供的3个中断辨识寄存器INTREG1,INTREG2和INTREG3,如表1所示。CPU首先对INTREG1和INTREG2进行判断,当它们全为0时,说明接收FIFO中的数据都是正确的,不存在成帧,奇偶校验、数据溢出错误。INTREG3中的低3位,表示接收FIFO中的数据到达了触发等级,CPU可以对FIFO进行读取。CPU通过对INTREG3中低3位的判断,可以清楚的知道哪个协议芯片的数据准备就绪,然后对指定的通道进行数据读取操作。

这种中断机制的引入减少了底层数据对CPU的中断次数,使得CPU有更多的时间去进行任务调度管理。中断服务流程如图3所示。

图3 中断服务程序流程图

表1 中断辨识寄存器

3 结果分析和结束语

将该系统的发送接收端口接到PC机的串口端,利用PC机超级终端可以正确显示系统通过任意UART端口发送出来的数据。本接口系统已经成功运用在某型号无人直升机航空信号仿真平台中。

本文基于FPGA技术,设计并实现了多通道的RS232/422接口电路,通过通道的选择和切换,提高了系统的处理能力。通过测试确定,多通道接口转换的信号符合UART规范。这种设计思路可以方便地应用到其他类型的总线通信模块的设计中。

[1]潘松,王国栋.VHDL实用教程[M].成都:电子科技大学出版社,2001.

[2]曹会华,贺占庄.基于有限状态机实现全双工可编程UART[J].计算机技术与发展,2007,17(2):54-56.