基于MultiSim10的MCU实时性仿真与研究

张小进

(闽江学院 计算机科学系,福州350108)

0 引 言

随着EDA技术的不断发展,电子产品的设计过程从模型的建立,到包括电原理图、PCB板图、MCU及接口、MCU控制程序、FPGA的构建、仿真、外观界面、热稳定分析、电磁兼容分析在内的物理级设计,再到PCB钻孔图、自动贴片、焊膏漏印、元器件清单、总装配图等生产所需资料等等全部在计算机上完成,发达国家目前已经基本上不存在电子产品的手工设计[1].

单片机系统的开发需要经历软、硬件设计、调试,以及制作后的联合统调;以上的任何一个步骤一旦存在错误就要回朔到前一个或若干个步骤进行修改设计,这导致了开发费用高、开发周期长等问题.美国NI公司推出的MultiSim9开始引入了MCU系统设计与仿真,它不但可以设计、仿真 MCU系统,也可以对外围的接口进行设计与仿真,还可以支持C或汇编的软件开发及断点调试、MCU的内存、寄存器查看等;从而使得单片机系统的开发可以更好地借助于计算机的辅助设计.

1 实时性仿真问题

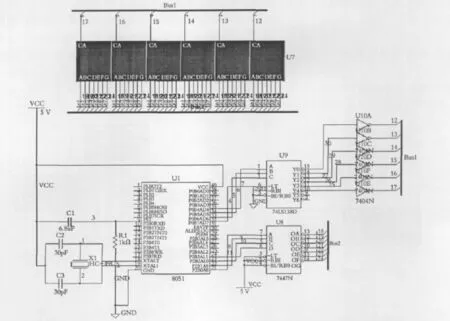

单片机系统通常应用于各种控制领域,它的实时性是一个极其重要的指标;主要体现在时钟定时中断、信息的动态显示和数据的输入等方面.无论是做系统开发还是辅助教学,设计者都希望自己的设计能在实现前进行很好地仿真,以检验设计中存在的软硬件错误、逻辑功能上的问题和实时性的效果.那么利用MultiSim软件对单片机系统进行辅助设计能否满足实时性仿真的要求呢?以常用的七段数码管显示系统时钟为例,在单片机系统中为了节省有限的I/O端口,数码管的显示一般采用动态显示技术,它利用人眼的视觉暂留现象,快速地轮流点亮各个数码管以达到稳定显示信息的目的[4-5].众所周知,只有位选通轮转的频率至少达到24/秒次才能看到连续的信息,而要看到稳定的信息需至少要达到48/秒次.实现一个六位七段数码管动态显示的硬件系统如图1所示.

这个系统采用7447N作为BCD-段码的译码输出,而不使用查表法;利用74LS138D输出位选通信号;用共阳七段数码管显示时、分和秒信息.

软件系统的算法流程如图2、图3、图4所示.

图1 数码管显示硬件系统

定时器工作于定时的方式1,利用其每隔50ms中断一次,寄存器计数累计到20次为1s时间到.按照以上的软硬件设计,仿真的结果应该是显示设置的时、分、秒,并实时更新时间,但是在仿真中我们会发现存在两个问题,导致仿真的结果与实际情况大相近庭.第一,没有实现连续、稳定的显示时间,而只是像跑马灯地显示;第二,仿真显示的时间与实际的时间相差很大,即显示的时钟走时慢了很多.

在MultiSim中,可以通过修改“仿真”菜单下的“交互式仿真设置”菜单项上的“默认瞬态分析”选项卡上的“设置初始时间步长”的值来改变仿真的速度,但是这个值的改变对数码管的动态显示仿真基本没有作用,表1是对该值选择不同时以上系统中某个数码管被选通的次数比较.

表1 设置初始时间步长

从表1统计的数据可以看出,在六位数码管动态显示系统中,50次/min的选通显然不能满足正常显示的条件;另外,初始时间步长的改变对动态显示效果的改善基本无效.

2 动态显示的极限测试

为了测试MultiSim下数码管动态显示的极限值,需要排除软件执行所花费的时间;因此,设计一个环形计数器用于产生数码管动态显示所需要的位选通信号[6-8],让数码管段码引脚固定连接“高”或“低”电平以显示某些数字,其测试硬件电路如图5所示.连接于P0口的数码管(内部带有译码电路)用于显示定时的数值;连接于P2口的数码管用于在定时时间到时显示选通脉冲的个数.

图5 动态显示极限测试

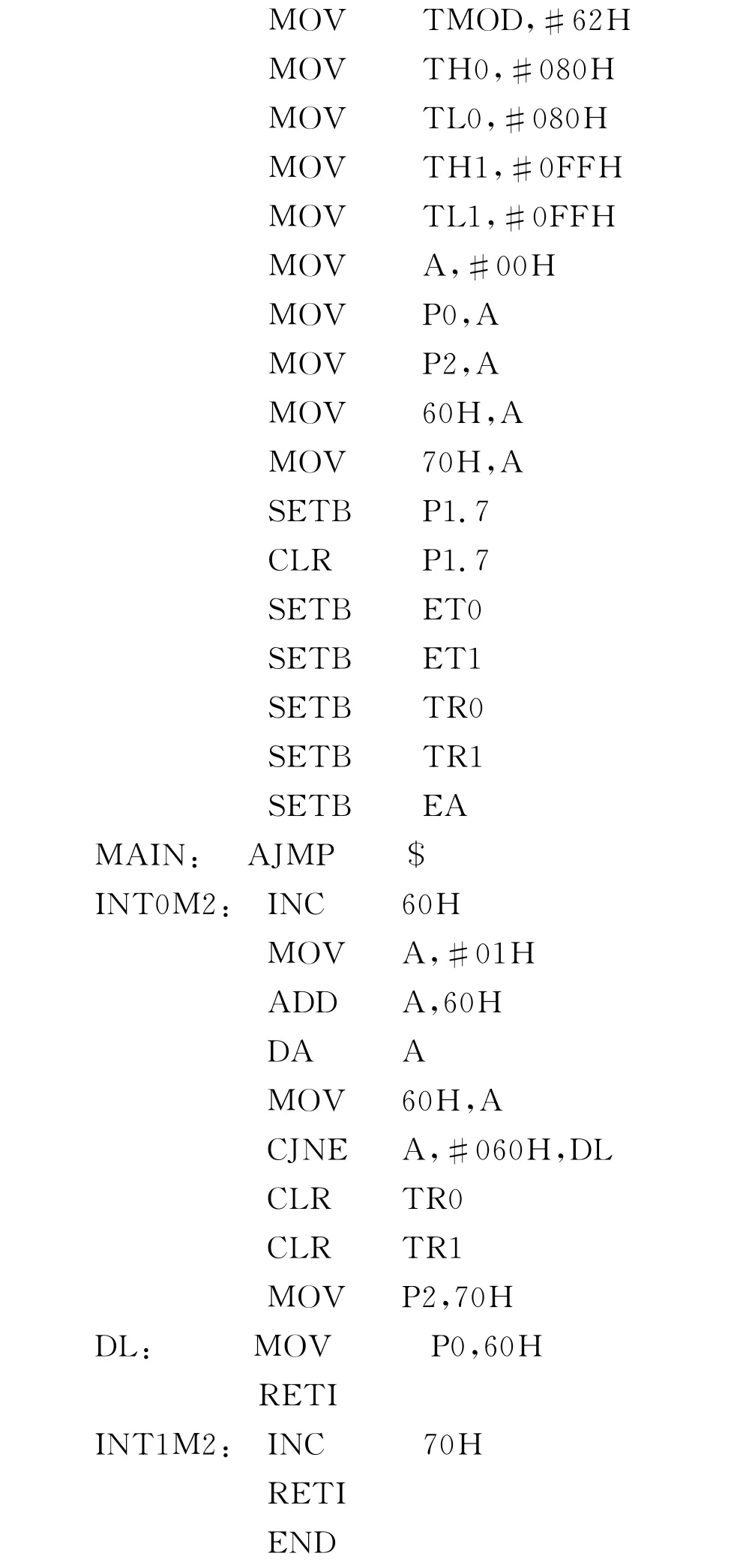

单片机用MultiSim默认的晶振频率12MHz,利用T0定时器定时以产生与实际时间相同的一分钟定时;利用T1定时器对环形计数器的输出,即位选通信号脉冲进行计数,测试出在实际时间1min内某位数码管被选通的次数.

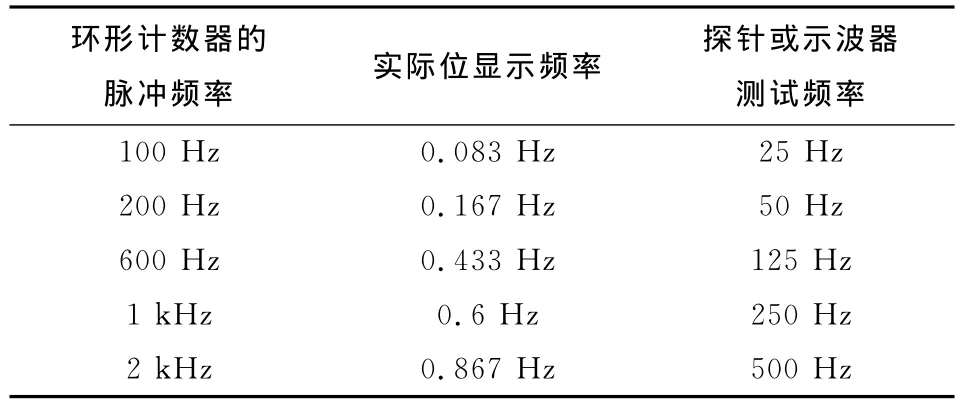

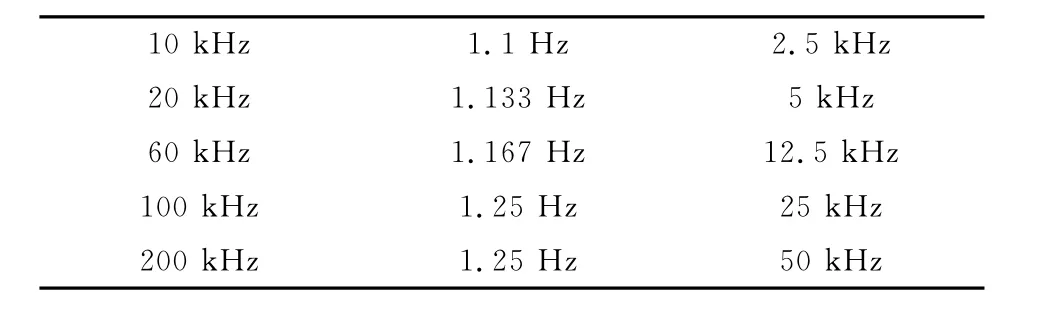

在MultiSim默认的仿真条件下,通过改变环形计数器的脉冲频率(占空比为50%),测试数码管某位实际显示的频率,表2是实际位显示频率测试的结果.

表2 极限测试实际位显示频率的变化

10kHz 1.1Hz 2.5kHz 20kHz 1.133Hz 5kHz 60kHz 1.167Hz 12.5kHz 100kHz 1.25Hz 25kHz 200kHz 1.25Hz 50kHz

从表2的结果可以看到,当环形计数器的脉冲频率达到100kHz后,实际位显示的频率已经无法提高了.

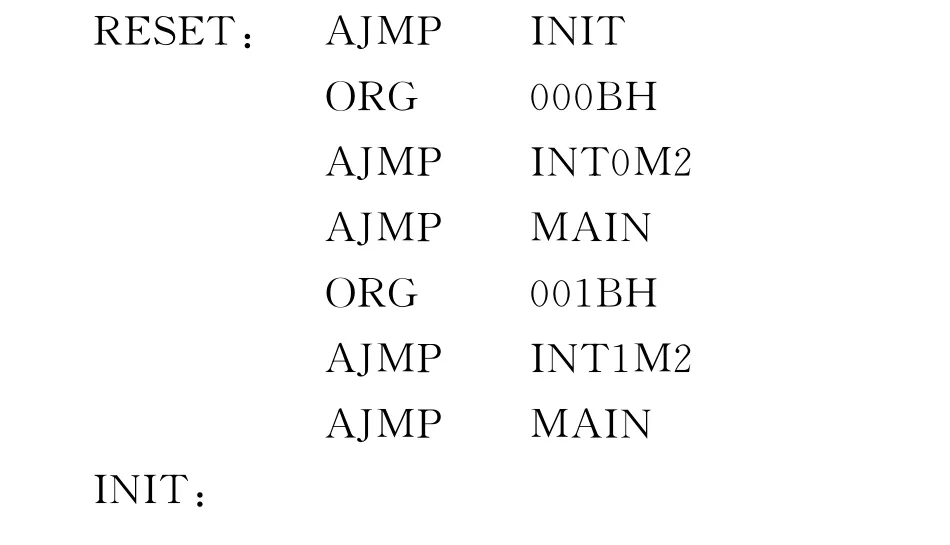

测试所用的程序代码如下:

在程序设计中,让T0、T1都工作于方式2,自动重装初值以减少误差.在纯硬件实现四位动态显示的条件下,环形计数器计数脉冲频率为100kHz,按照MultiSim默认的“设置初始时间步长”值,测试结果为75次/min,即1.25次/s;当“最大时间步长”和“初始时间步长”都设置为80s时,测试结果为96次/min,即1.6次/s;显然这都是无法满足连续地显示仿真,但是这并不代表该软件不能实现数码管的动态显示仿真,因为在数码管的位选通引脚上只要接上“测量探针”就可以检测到位选通脉冲的频率,如图2中所示.因此,尽管看不到实际仿真的实时效果,但只要该频率大于48Hz,在实际系统中是一定可以实现动态显示的.

在单片机系统中,定时器的计数初值计算公式是:

(2n-X)机器周期(μs)=定时时间(μs)

式中n的取值为0、1、2,分别对应定时器的各种方式;由于在MultiSim中8051默认的晶振频率是12MHz,所以机器周期是1μs.在使用定时器仿真时由于线程时间配额的关系,定时器初值计算值的定时结果在仿真的实际效果中会大大延长;具体延长多少与不同的PC硬件、操作系统、当时运行的进程、以及是否正在做I/O操作等因素是有关的;在双核的Intel(R)Pentium(R)Dual e2140@1.60 GHz CPU、Windows XP的操作系统下,大约100 μs的定时时间相当于实际时间的1s;之所以是大约的值,是因为与PC系统开启的进程多少,如是否播放音频、视频等有关.

3 MultiSim实时性分析

Multisim运行于多用户、多任务的操作系统平台下,其设计的仿真作为一般用户进程中的线程分时轮转地使用操作系统的线程时间配额.对于Windows 2000/XP操作系统而言,每个线程都有一个优先级和时间配额.

3.1 线程优先级

在Windows 2000/XP操作系统下线程分为32个线程优先级,优先数是0到31,优先数越大优先级越高.其调度是基于内核级线程的抢占式调度,调度策略是采用动态优先数多级反馈队列,每个优先数都对应于一个就绪队列[2].线程优先数在31~16范围的属于实时优先级,用于通信和实时任务;线程优先数在15~1范围的属于可变优先级,用于用户的交互式任务;线程优先数为0的属于系统线程优先级,用于系统中的页面任务.

在Windows 2000/XP操作系统中可以通过任务管理器修改进程的基本优先级,相应的线程会继承进程的优先级.如果用户有权限,可以将 Multi-Sim的进程优先级升高到“实时”,由于硬件中断的优先级高于任何线程,所以它不会阻塞硬件中断处理,但是它可能阻塞关键系统线程(如存储管理器、缓存管理器、本地和网络文件系统和设备驱动程序等)[3].因此,在仿真过程中会看到,当优先级设置为“实时”后仿真可能处于不稳定的状态;另外,在仿真过程中不能有I/O操作,例如,移动鼠标、敲击键盘等,因为这些操作的中断处理将优先进行,会导致仿真中线程暂停和时钟定时的严重滞后.

3.2 线程时间配额

时间配额是一个线程从进入运行状态到 Windows 2000/XP检查是否有其他优先级相同的线程需要开始运行之间的时间总和[3].缺省状态下,线程开始的时间配额为6,每个时钟中断减少的时间配额为3,因此一个线程的缺省运行时间为2个时钟中断间隔.对于X86单处理器系统的时钟中断间隔为10ms.换而言之就是在Windows 2000/XP(专业版)平台下线程缺省的运行时间是20ms.如果一个进程只有一个或几个线程,线程优先级为“实时”且仿真运行时不进行I/O操作的话,那么至少是可以满足数码管连续的动态显示.

然而,通过任务管理器可以看到MultiSim运行时有二十几个线程,且操作系统中还有相当数量较高优先级的系统进程和后台进程(每个进程有至少1个的线程),通过简单的推算可以估计出一个仿真线程最快的情况下需要约500ms轮转一次,也就是最快2次/s;这与动态显示的极限测试的结果是基本吻合的,因此,在MultiSim下仿真要看到数码管动态显示符合实际的效果是不可能的.

4 结 语

本文主要针对MultiSim下MCU系统的实时性仿真存在的问题进行分析与研究,设计了数码管动态显示的极限测试硬件电路和测试代码,对极限测试的结果从MultiSim运行的平台,即 Windows 2000/XP操作系统的角度分析了其实时性仿真的局限性和造成仿真中与实际效果不符的原因.

由于仿真中MCU的定时时间显示效果与实际时间差别较大,因此在MultiSim使用仿真时,为显示需要所调用的延迟子程序可先注释掉,以利于显示效果.

[1] 王冠华.Multisim10电路设计及应用[M].北京:国防工业出版社,2008:20-23.

[2] Abraham Silberschatz.[美]等.操作系统概念[M].北京:高等教育出版社,2002:114-122.

[3] 孙钟秀.操作系统教程[M].高等教育出版社,2003,(3):153-161.

[4] 张毅刚.新编 MCS-51单片机应用设计[M].黑龙江:哈尔滨工业大学出版社,2006:153-157.

[5] 周立功.单片机与CPLD综合应用技术[M].北京航空航天大学出版社,2003:338-340.

[6] 黄 丽.基于Multisim仿真的超声波测距系统的设计与实现[J].湖南工程学院学报,2009,19(2):27.

[7] 刘 超,等.基于NI Multisiml0MCU模块的单片机仿真[J].应用天地,2008,27(8):58-59.

[8] 石嘉顺.基于Multisim环境下的电路设计与仿真[J].计算机仿真,2007,24(12):307-308.