基于FPGA的数字下变频(DDC)设计

徐小明, 蔡灿辉

(国立华侨大学 信息科学与工程学院,福建 厦门 361021)

0 引言

软件无线电系统[1]的基本思想是在一个标准的、通用的、模块化的硬件平台上,通过软件来实现其各项功能,从面向用途和基于硬件的设计方法中解放出来。软件无线电系统拟解决的关键问题是后端DSP器件的运算速度,因为经过模数(AD,Analog to Digital)转换芯片高速采样后的数据对于DSP器件的处理速度来说是个沉重的负担。目前解决这一问题的通用方法是:高频模拟信号先经过模拟下变频到适当中频,然后在中频阶段对其进行AD采样以输出高速的数字中频信号,最后经过数字下变频技术的抽取和低通滤波处理后,使其变为低速率的基带信号再送给后端DSP器件进行实时处理。这一过程同时降低了前端AD芯片和后端DSP器件的性能要求。

DDC技术连接着前端AD芯片与后端DSP器件,起着桥梁的作用,其性能的优劣会对整个软件无线电系统的实用性、可靠性、稳定性产生直接影响[2]。可以说, DDC是软件无线电系统中必不可少的技术之一。

在利用具有功能强大的、灵活性高的、可重复编程等优势的FPGA芯片的基础上,再参考一些专用的甚至已经商用化的DDC芯片,从而设计出合适的数字下变频器,这成为如今采用FPGA+DSP模式来设计软件无线电系统的一种主流思想[2]。

1 数字下变频器的结构原理

现有的DDC系统的设计方案基本上采用的一种通用固定的结构[2-4]:即模拟输入信号经过AD芯片高速采样形成数字化的、高速率的数据,其在与NCO输出的正余弦信号进行混频后形成正交的I、Q2路。由于数据具有很高的速率,只有在通过了抽取滤波器使得其速率大大降低后,才便于送给后端DSP设备进行实时处理。例如对一个宽带为5 MHZ的信号,以100 MHZ的速率进行采样,即使每个采样值运算100次,其运算量就达到10000 MIPS,这就要求DSP设备具有相当高的处理能力,就目前DSP设备的技术水平来说是不现实的。

在图1所示的数字下变频结构中,虚线框之外的各个模块说明了上述过程。其中抽取滤波器的功能是对混频后数据进行抽取降低数据速率以及滤除倍频分量和干扰信号。它由CIC滤波器、HB滤波器和FIR滤波器进行级联的方式来实现的。其中各方面都具有较好的性能积分梳状滤波器和半带滤波器实现了抽取降速的功能,而FIR滤波器则较好的完成整形滤波的功能。

文中通过对典型DDC系统结构进行深入分析,在此基础上对各个模块的实现提出了新的方法。图1中,虚线框标明参数控制模块是本文设计提出的新想法之一。该模块使得NCO的输出可以是不同的频率、不同位宽的正余弦信号,而且该模块还对CIC滤波器的阶数、级数以及延迟等参数进行可编程控制。这恰恰体现了软件无线电的基本思想。对于HB滤波器和FIR滤波器模块,本文采用了Matlab的FDAtool工具箱,并配合Xilinx FPGA设计中的IP core生成工具来实现。可视化的FDAtool工具箱和这些经过严格测试和优化过的IP core大大提高了设计的可靠性和可操作性。

图l 数字下变频结构

2 数字下变频器的各模块设计

2.1 NCO的FPGA设计

NCO的性能优劣将直接决定着数字下变频器的性能,NCO的用途是产生稳定的、正交的、频率可控的正余弦信号。NCO的实现方法通常有2种:坐标旋转数字计算(CORDIC,Coordinated Rotation Digital Computer)算法和查表法,2种方法均有各自的优缺点。本设计采用的是查表法,其基本原理:根据NCO的各个相位值事先计算好与其相对应的正余弦数据值,并将正余弦数据值存储在只读存储器(ROM,Read Only Memory)中。系统工作中把相位作为地址索引信息来访问ROM,从而输出相对应的正余弦数据值[5]。

NCO的输出频率:上式中,fclk是系统基准时钟,BΔθ是频率控制字,N是相位累加器的数据位宽。可知输出频率与频率控制字成正比,如果在已知fout的情况下,可计算出频率控制字BΔθ。

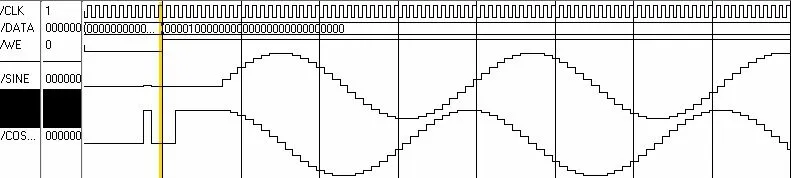

该设计的NCO模块是在Xilinx公司的ISE开发环境下采用Verilog硬件描述语言编写[6-7],经过ISE综合后在Modelsim中对其进行仿真。得到如图2所示的仿真结果:图中系统时钟fclk为100 MHz,其中参数控制模块配置相位累加器的数据位宽N为30位,若频率控制字BΔθ为0h2000000,由(1)式得出输出频率为系统时钟的1/16(6.25 MHz)标准的正余弦信号。

图2 NCO在Modelsim中的仿真结果

2.2 CIC滤波器的FPGA设计

CIC滤波器常常应用于高速抽取或内插系统中,其能对高速数据流进行任意抽取因子的抽取处理。不用进行乘法运算是CIC滤波器的最大优点。高速数据流通过CIC滤波器抽取后降到较低速率的数据后,将便于后级的HB滤波器抽取和FIR滤波。因此CIC滤波器常处于多级抽取中第一级的位置。

单级的CIC滤波器的冲激响应如式(2)所示:

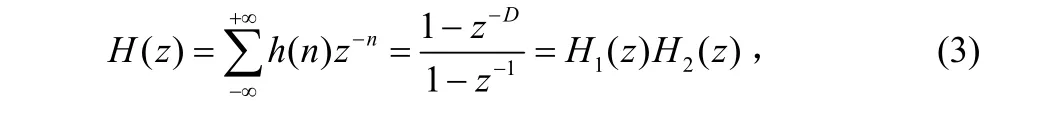

上式中,D为单级CIC滤波器的阶数,有时也称为抽取因子。且由Z变换的定义得出CIC滤波器冲激响应的Z变换为:

图3 CIC滤波器的等效结构

从图3中可以看出,H1(z)实际上就是一个累加器,也常被称为积分器;H2(z)则称为梳状滤波器。由于单级CIC滤波器的旁瓣电平较大,阻带衰减和过渡带的综合特性都不是很好。为降低旁瓣电平,可采用多级CIC滤波器级联的方式来实现。但综合考虑带内平坦度等原因,实际中CIC滤波器的级数是有限的,不宜过大,一般为5级为限。

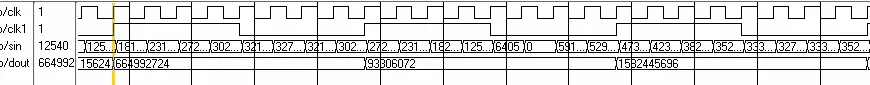

本设计中参数控制模块配置产生一个5级8倍CIC滤波器,并采用Verilog语言对图3所示积分部分和梳状部分进行分模块编写。经过ISE综合后并在Modelsim中仿真,得到如图4所示的仿真结果:仿真过程中,输入信号为混频器的输出信号,采样速率设为100 MHz,从仿真波形可以看出:CIC滤波器对输入数据每8个为一周期进行抽取,图中还可知CIC滤波器在实现了抽取功能的同时,也使得采样速率变为原来的1/8即12.5 MHz。

图4 CIC滤波器在Modelsim中仿真结果

2.3 HB滤波器的FPGA设计

要用到第二级抽取的原因是综合考虑到带内平坦度和阻带衰减度等因素使得第一级CIC抽取滤波器的级数和抽取因子不宜过大。

HB滤波器的带内平坦度好,计算效率高,在高速率信号处理中发挥着重要的作用。在抽取因子等于2的幂次方的场合更是如鱼得水。常将其作为第二级低通滤波和抽取。

单级的半带滤波器的冲击响应如式2-4所示:

由式(4)可以看出半带滤波器的冲激响应h(n)具有偶对称性质,即h(n)=h(-n),长度N=2L+1,其偶数点(零点除外)均为零。所以HB滤波器只需一半的计算量就能达到变换数据采样率的目的,特别适用于实时处理的场合。

半带滤波器的频率响应H(jω)有如下关系:

式中ωC为通带截止频率,ωA为阻带起始频率,δP为通带波动,δS为阻带波纹。HB滤波器的通带宽度(ωC)和阻带宽度(π-ωA)是相等的,且通带和阻带波纹也相同,如图5所示。

图5 半带滤波器幅频特性

在半带滤波器的设计中采用的是结合Matlab的FDAtool工具箱和Xilinx FPGA设计中的IP core生成器[9]这两个工具,然后在ISE中通过Verilog语言进行例化处理。其具体步骤为首先在FDAtool工具箱中设计好半带滤波器参数,本次设计采用凯撒窗实现,其中通带为6.25 MHz,采样率为100 MHz。在FDAtool中设计完后,然后导出滤波器参数(后缀名为.coe)文件。最后在Xilinx FPGA设计中的滤波器IP core导入该系数文件并完成一些参数配置。其经过ISE的综合后在Modelsim仿真的结果如图6所示。

图6 半带滤波器仿真结果

图6中的输入信号是CIC滤波器的输出数据,由图可以看出HB滤波器不仅完成了输入数据的2倍抽取,并使得输出信号的采样频率变为输入采样频率的一半。

2.4 FIR滤波器的FPGA设计

数字下变频的最后一级是FIR滤波器,FIR滤波器不做抽取功能,只负责对信号进行整形滤波。FIR滤波器的设计目标是在满足通带波纹和过渡带宽尽可能窄的同时使得阻带衰减尽可能大,若FIR滤波器的阶数越高,滤波器的通带波纹、过渡带带宽、阻带衰减等特性就越好。而经NCO混频后的基带信号由CIC滤波器和HB滤波器的抽取降速后输入到FIR滤波器中。由于此时的数据速率相对较低,所以FIR滤波器在保证对数据进行实时处理的前提下,是可以适当提高FIR滤波器阶数以满足设计的性能要求。本文设计FIR滤波器采用的方法和设计HB滤波器的方法类似。也是通过采用窗函数思想,结合FDAtool工具箱和Xilinx FPGA设计的IP core生成器这2个工具来完成的,这里就不详细介绍。

3 系统仿真

该系统实现的数字下变频具体处理流程为:频率为10 MHz的中频信号由AD器件以频率为100 MHz采样时钟实施采样,然后把采样后的数据送入到FPGA中:FPGA内部控制NCO的参数使其产生频率为6.25 MHz的正余弦两路信号与采样数据进行的混频。混频后得到3.75 MHz正交的I、Q2路第二中频信号;信号通过8倍抽取的5级CIC滤波器得到12.5 MHz采样率的信号;再通过一级半带滤波器2倍抽取变为6.25 MHz采样率的信号;最后经过FIR整形滤波后输出低采样速率的信号供后级的DSP进行处理。其仿真波形如图7所示。

图7 系统仿真

由图7可以看出,高速率的信号再经过了CIC滤波器和HB滤波器之后,输出信号变成了较低速率的信号,而FIR滤波器则对输出信号进行了整形滤波。以上的仿真结果验证了本文所设计的数字下变频器在 功能上是满足理论要求的,且符合了设计的最初设想。

4 结语

综上所述, 数字下变频技术是保证DSP设备实现实时处理的关键,文中所提出的这种通用的数字下变频实现方案能行之有效的完成下变频器的基本功能且在实现方法上具有较高的灵活性和可操作性。将其应用于软件无线电系统中则免去了使用专业数字下变频芯片的麻烦,即能有效的实现所期望的功能和价值。

[1]BURACCHINI E. The Software Radio Concept[J].IEEE Communications Magazine, 2000,38(09):138-143.

[2]陈卓. 基于FPGA的软件无线电DDC设计[D]. 成都:成都理工大学,2008.

[3]严家明,李瑾,胡楚锋. 基于正交混频的数字下变频技术研究[J].计算机测量与控制, 2009,17(01):200-202.

[4]屈有萍. 基于FPGA的数字下变频研究实现[D]. 西安:西安电子科技大学,2007.

[5]赵宏峰. 中频数字化接收机中的下变频器研究[D]. 南京:东南大学,2006.

[6]田耘,徐文波,张延伟. 无线通信的FPGA设计[M].北京:电子工业出版社,2008:215-252.

[7]夏宇闻.Verilog HDL高级数字设计[M].北京:北京航空航天大学出版社,2008:130-210.

[8]石蔚,黄佩伟. CIC滤波器的FPGA实现[J]. 信息安全与通信保密,2005,6:28-30.

[9]Xilinx lnc. Xilinx V-4 user Guide[EB/OL].(2008-12-01)[2010-10-22]. http://www.xilinx.com.