高性能NAT-PT应用层网关设计

安勤玲

烟台市食品药品检验所 山东 264000

0 引言

网络地址转换-协议转换(NAT-PT)是一种IPv4/IPv6过渡时期采用的转换技术,通过NAT-PT网关设备连接IPv6网络和IPv4网络,可以实现纯IPv6节点和纯IPv4节点之间的透明通信。当IPv4和IPv6节点之间通信时,NAT-PT网关实现两种IP协议的格式翻译和地址的映射:NAT-PT网关将维护一个IPv4地址池,支持为IPv6网络中的节点动态分配IPv4地址和端口,并通过建立 NAT表维护地址端口映射关系,完成IPv4协议和IPv6协议的转换。

NAT-PT技术对 v4/v6网络两端的主机是透明的,运行在不同版本网络协议上的应用程序不需做修改就能完成业务,较好地解决IPv4和IPv6的互通问题。但对于需要在应用层协议的负载中携带IP层信息的应用,可能会导致不能正确通信,如DNS地址查询应答报文中对应被查询域名的IP,在跨越v4/v6网络时需要转换成对应协议格式,FTP协议在其控制连接中携带有FTP数据连接相关的IP地址/端口信息,SIP协议 INVITE应答等消息中也携带该对应主机所在网络版本的IP地址,这些信息不做相应的转换翻译在另一端将不能被正确识别,因此这些转换工作都需要对应的 ALG功能实现。

本文不侧重于NAT-PT协议和应用层网关ALG功能的具体实现,而侧重于从整体上讨论具有广泛参考意义的基于网络处理器的高性能应用层网关设计。

1 NAT-PT实现基础框架

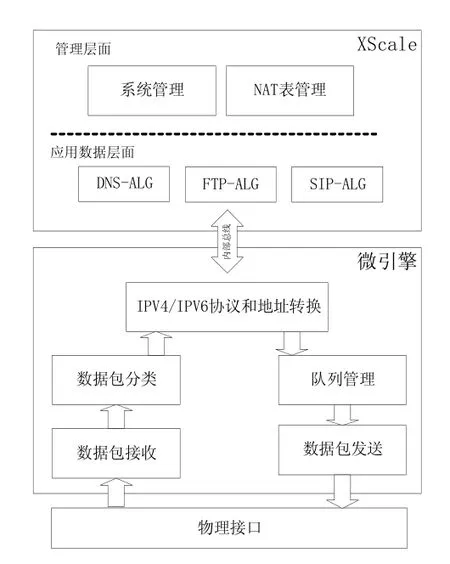

传统的网络设备的开发,在硬件体系结构上一般采取通用CPU和专用标准设备组成,或者采取基于ASIC的设计方案。第一种方案主要依靠软件来实现功能,可扩展性较强,但是其缺点也十分明显的,处理能力较低,无法适应现代高速网络的要求。第二种方案以硬件的方式实现功能,能够有效提高网络设备的处理性能和速度,但是缺乏了灵活性,且成本较高。近年来,网络处理器(Network Processor,NP)的出现给网络设备的设计带来新的选择。网络处理器采用了与传统的处理器不同的设计,既有ASIC的高速处理能力,又有完全的可编程特性,是一种具备线速转发和智能处理的方案。为了设计一个高性能的NAT-PT网关设备,使之能够适应高速的网络环境,能够达到线速1Gbps的要求,并且能够对 ALG数据处理进行较为复杂的处理,我们采用 Intel IXP2400网络处理器及其提供的IXA SDK软件框架来做为NAT-PT设备的基础框架。系统参考原型的系统框架结构图如图1所示。

在NAT-PT系统原型的设计中,主要参考INTEL提供的IXP SDK设计模型,利用IXP2400网络处理器中的8个微引擎(Micro Engine,ME)进行普通网络数据包的快速翻译和收发功能,利用IXP2400的Xscale处理器进行应用层数据(异常)包的处理和实现系统的管理功能,其中异常包的处理包括需要进行较为复杂转换的 ALG数据包的处理。经过测试,基于网络处理的NAT-PT网关设备,能够很好的达到了普通数据包1Gbps线速转发的要求。但是,其应用层网关(ALG)的处理性能不很理想,吞吐率低,不足 10Mbps。根据已有的网络流量统计数据表明,网络中数据流量的6%的数据属于ALG处理的数据范畴,因此以设计总吞吐率为1Gbps的 NAT-PT设备为标准,ALG的吞吐率要求至少要达到60Mbps。

ALG功能是保证NAT-PT能够顺利进行IPv4/IPv6网络互联互通的关键,因此如何设计出高性能的ALG,是NAT-PT网关设备能否成功的关键之一。下节将以FTP数据包从数据从输入到输出经过的处理流程为例,逐步分析整个 ALG处理流程中可能的性能瓶颈,并提出对应的解决方案。本系统支持的其他需要做应用层翻译的协议,如 SIP、DNS,对数据包的处理流程基本相同,对 FTP-ALG性能的分析和设计也适用于SIP-ALG,DNS-ALG。

图1 原系统参考框架结构图

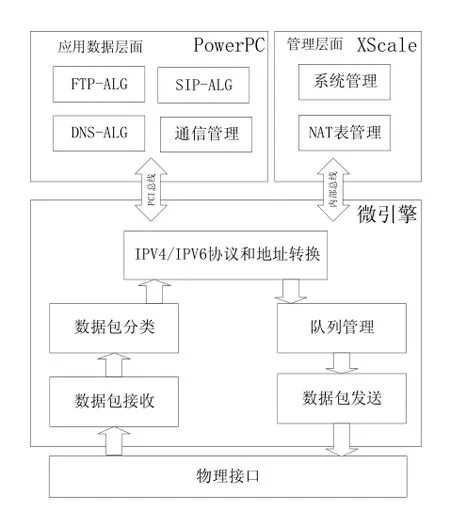

图2 新设计系统体系结构图

2 高性能应用层网关(ALG)设计分析

2.1 ALG处理流程分析

以FTP数据包的流程为例,数据包的处理主要经过以下处理流程:

(1) 底层微引擎执行数据包的接收和解包工作,并对数据包进行分类,若此数据包需要ALG处理,则将此数据包的描述符通过 IXA 3.1 SDK的消息机制传递到Xscale层;

(2) Xscale接收到处理ALG的消息之后,通过IXP2400系统内部总线读取数据包缓冲,进行IP头部的V4/V6转换,分析数据包的负载,将负载中需要翻译的字段进行数据转换,并更新其传输层相关字段,此为 ALG的主要功能。最后进行路由表的查找;

(3) Xscale将处理之后的ALG数据包描述符通过消息机制发送到ME,由ME查L2(MAC层)表,组成完整的以太网帧,从相应的端口发送。

2.2 Xscale处理能力分析

IXP2400中的核心部件是8个ME,ME拥强大的指令执行单元,并且每个微引擎内部有8个硬件线程,ME上的程序由微码实现。经测试,ME在接收包、解封装包、包分类以及发送处理过程中可以达到 1Gbps的处理能力,相对与10Mbps的ALG流量而言,ME并不是ALG处理流程中的瓶颈。ALG处理功能大部分属于字符串处理,ME使用的是类汇编的微码来编程,不适合处理较为复杂的 ALG功能,因此必需传递给Xscale进行处理。 Xscale主频为600M,属于嵌入式精简指令集处理器,虽然能够使用高级语言编程进行通用数据处理,但是其处理能力比其它通用CPU存在差距,同时Xscale还负责执行整个系统的管理功能。经过测试试验表明,在ALG输入吞吐率从0-10Mbps的过程中,Xscale的负载迅速提高,当到达吞吐率达到10Mbps时,其CPU使用率接近100%,因此Xscale有限的处理能力是制约NAT-PT设备处理ALG性能的瓶颈之一。

为了解决Xscale的处理能力瓶颈,在单NP(1个Xscale+8个ME)的基础上,我们提出基于PMC方式外接了一个处理能力更强的通用CPU(PowerPC,主频1G, 512M DDR内存,内存总线64bit/133MHz,PCI总线64bit/66MHz)的方案,将ALG的处理功能任务转移到PowerPC上,当ME接收到数据包,并判断其为 ALG数据时,不再提交给 Xscale,而直接提交给PowerPC进行ALG处理,利用PowerPC在通用计算上的优势解决Xscale处理能力的瓶颈问题。新的系统框架结构图如图2。

在新设计的系统中,在BSP驱动层面将IXP2400的内存直接映射到PCI地址空间之上,因此PowerPC可以直接通过PCI总线访问到 IXP2400的内存空间。同时也将原来的在Xscale的管理层面和应用数据层面分开,使系统模块功能更为清晰和独立。

2.3 数据包拷贝性能分析

在系统原型的设计中,Xscale和ME通过系统内部总线共享内存,因此当Xscale读取数据包的缓冲数据时,访存延迟低。而在新的设计中,PowerPC作为IXP 2400的一个外部设备,PowerPC只能通过PCI总线访问IXP 2400的内存。在PowerPC处理ALG数据之前,必需通过PCI总线读取对应数据包的数据,在处理结束之后再次通过PCI总线将新的数据包写回,提交给ME进行转发。其中PrPMC的PCI总线的频率仅为66MHz,因此PowerPC在拷贝数据包的过程中访存延迟比Xscale直接通过系统内部总线大。

为了更好测试拷贝对整体 ALG处理性能的影响,我们首先对 PowerPC在没有数据包拷贝的情况下进行纯数据翻译处理,然后再加上数据包的功能进行测试,比较不同包拷贝方式之间的性能差异。

测试结果表明PowerPC在没有数据包拷贝的条件下,至少能够达到每秒处理15,000个FTP数据包的性能,若每个FTP数据包为72byte,则吞吐率超过100Mbps。在此基础之上,加入通过PCI总线,以PIO(Programmable I/O)方式进行数据包拷贝的处理,并使用长度为72byte的FTP包进行测试,测试结果显示PowerPC吞吐率下降至34Mbps。因此数据包拷贝的性能是整个新系统ALG处理吞吐率的瓶颈。

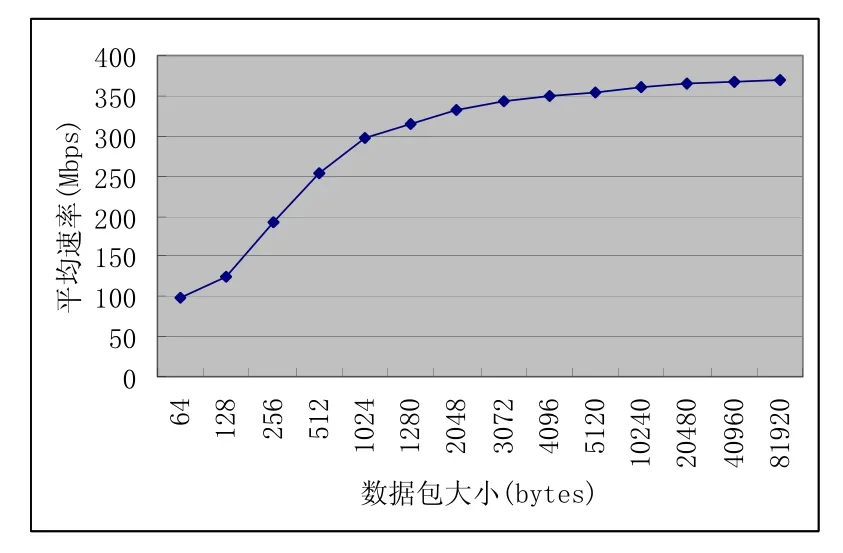

DMA(Direct Memory Access)是一种无需CPU的参与就可以让外设与系统 RAM 之间进行双向数据传输的硬件机制,使用DMA可以使系统CPU从实际的I/O数据传输过程中摆脱出来,从而大大提高系统的吞吐率。经过测试,以DMA方式代替PIO方式进行数据包拷贝,PowerPC处理ALG的吞吐率可以提高到50Mbps。DMA方式是提高数据包拷贝速度的有效途径,但是DMA方式的读写优势体现在处理大数据量的时候。在测试中,每次 DMA读取的数据大小仅为72Bytes,因此并没有发挥DMA的最佳性能。通过测试单纯的DMA数据读取,每次读取的数据大小从逐渐变大,可以统计出DMA读取性能与读取数据大小之间的变化趋势。测试时每一种大小的数据包大小均进行 10次测试,记录下每次读取所消耗的时间,然后取其平均值作为读取此该数值大小的数据包所消耗的时间,并根据计算出平均传输速率。图 3为各种数据包大小与其平均速率之间的变化曲线图。

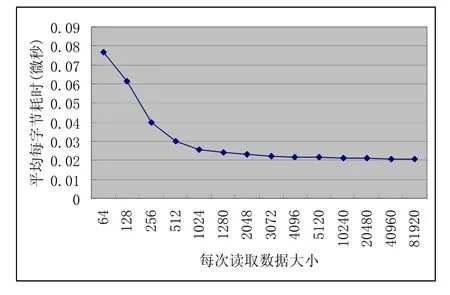

测试结果中证明了DMA读取速度随着每次读取数据的大小增大而提高,同时随着每次读取数据大小的增加,DMA读取的速度提高的幅度也随之减小。图4是根据测试结果计算出的平均读取每一个字节的耗时变化趋势。不难得出如下结论:当每次读取大小增加到一定程度之后,再增加每次读取数据的大小,对提高平均读取速度已经没有太多作用,其平均每字节耗时已经趋于稳定。在DMA读取中,为了保证高速读取,PowerPC端的缓冲区必需是在SRAM中分配的,而PowerPC的SRAM是片内的二级缓冲,预留给应用程序使用的空间很小,因此必需选择一个合适的缓冲大小,使其发挥最大效率。当平均增加一个字节带来的速率提高小于1Kbps的时,我们认为没有实际性能提高。因此,通过计算我们确定每次读取大小为 5120Bytes的数据能够发挥 DMA读取方式的最佳性能。

图3 DMA数据读取速率测试结果

图4 每字节平均耗时变化趋势

ALG要处理的数据包一般大小在 64Bytes到 512Bytes之间,采取组包之后再使用DMA方式进行拷贝的方案可以充分利用DMA读取的性能。即在IXP2400中利用ME先将多个数据包组合成大小为5120Bytes的数据包集,并将此数据包集拷贝到指定的内存空间中,然后再发送消息给PowerPC,通知其从指定内存地址中使用 DMA方式整体拷贝到PowerPC的本地内存,再进行逐个数据包的拆分处理。经过测试,在输入数据包大小为72Bytes时,组包DMA拷贝方式的ALG处理吞吐率能够达到65Mbps。此性能指标较好的满足系统对ALG的吞吐率的要求。

2.4 对ALG处理算法的优化

影响 ALG处理性能除了硬件体系结构上的因素之外,程序本身的效率也是关键因素之一。在设计 ALG过程中,针对IXA3.1的SDK中一些如计算Hash值的算法进行了优化,以及优化的系统函数调用,避免内存波动等措施。优化后的测试表明,通过算法层面的优化,能够提高 ALG处理的性能。

3 性能测试结果

本节对NAT-PT网关设备ALG性能进行全面的测试,主要考察在各种设计方案实施前后NAT-PT对FTP-ALG处理性能。以 Spirent公司的 SmartBits作为测试工具,通过SmartBits给NAT-PT发送v4 FTP数据包,同时接收转化后的v6 FTP数据包,不断提高发送速率,以NAT-PT开始出现丢包时 SmartBits的发送速率作为最高吞吐率。试验连接图如图5所示。

图5 测试环境拓扑结构

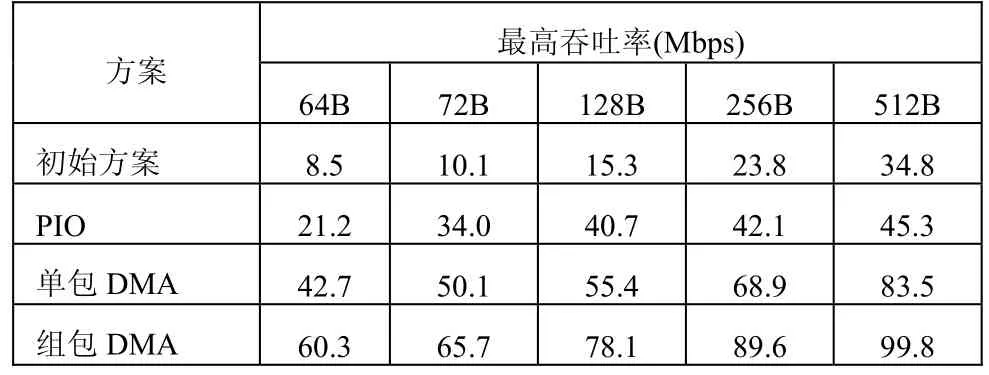

表1 改进方案测试统计数据

由于 ALG数据大多属于控制信息,因此单个数据包比较小,因此我们选取64Bytes,72Bytes,128Bytes,256Bytes和512Bytes的包作为性能测试包,可以较好的反应出系统的实际性能。表1为具体的测试数据结果。

4 结论

本文从网络设备的硬件体系结构分析开始,逐步分析制约NAT-PT 实现ALG的性能关键瓶颈,得出Xscale是网络处理器中在进行大量通用计算处理时瓶颈的结论,提出了以外接方式添加通用处理器(PowerPC)的方案,以弥补 Xscale的处理能力不足;为了解决PowerPC与网络处理之间数据通信速度的问题,提出以DMA方式进行数据读取方案,并通过一系列的测试,分析测试数据确定出DMA方式数据读取的最佳性能的参数,最后结合 ALG的具体实现,进行的相关程序算法优化,完成整个NAT-PT网关设备处理ALG性能的提升。最终经过测试,证明按照方案实现的 ALG处理性能比原型系统提高了6倍,最小包达到60Mbps的性能,较好的达到系统要求。同时也给出基于网络处理器的高性能网络设备设计提供了参考。

[1] Tsarists G,Srisuresh P.Network Address Translation-Protocol Translation (NAT-PT).RFC 2766.2000.

[2] P.Srisuresh,G.Tsirtsis.DNS extensions to Network Address Translators (DNS_ALG).RFC 2694.1999.

[3] M.Altman,NASA Lewis/Sterling Software,S.Oysterman.FTP Extensions for IPv6 and NATs.RFC 2428.1998.

[4] 陈沫.基于IXP2400网络处理器的高性能IPv4/IPv6互通网关.计算机工程.2006.

[5] 张宏科.网络处理器原理与技术.北京:北京邮电大学出版社.2004.

[6] Brayant,R,E.Computer System a Programmer’s Perspective深入理解计算机系统.北京:中国电力出版社.2004.