可变参数数据采集控制电路的FPGA实现

李 媛,王 畅,郭建新,刘尚峰③

(①空军工程大学 电讯工程学院,陕西 西安 710077;②华北水利水电学院,河南 郑州 450011;③空军雷达学院,湖北 武汉 430019)

0 引言

数据采集处理技术是现代信号处理的基础,广泛应用于雷达、通信、遥测遥感等领域。随着信息科学的飞速发展,人们面临的信号处理任务愈来愈繁重,对数据采集处理系统的要求也愈来愈高[1]。数字采集卡[2]是现代数字通信接收机和信号分析处理的常用设备,其基本功能就是对接收到的模拟信号进行受控采样,获得满足要求的数字信号。常用的数据采集方案往往采用单片机(MUC)或数字信号处理器(DSP)作为控制器,以控制模数转换器(AD)、存储器和其他外围电路的工作,但因单片机自身指令周期及处理速度的影响,很难达到多通道高速数据采集系统的要求,虽然 DSP可以实现较高速的数据采集,但在提高其速度的同时,也增加了系统成本[3]。由于FPGA[4]技术具有工作频率高,设计灵活,可编程性好,适合于时序、组合逻辑电路应用等特点,使得FPGA在实现数据采集上有着不可比拟的优势。基于FPGA平台,运用VHDL语言[5]设计并实现数据采集控制电路系统,最大限度地提高信号采集和处理能力。

1 设计需求

系统的设计需求如下:

①采样率:20 MHz和20.32 MHz可选,通过外部选择信号控制;

②采样位宽:12 bits;

③采样开始条件:支持软件软触发和外部硬触发;

④采样批次控制:通过控制可以实现一次采1、2、4、8或16批数据;

⑤采样深度控制:每一批深度可分别为128、256、512、1024、2048、4096、8192、16384。

⑥采样时延控制:接收到采样开始命令后,要延时规定时间才能进行采样,延时时间为 16、32、64、128、512、1024、2048、4096个采样时间。

2 实现方案

2.1 系统组成与总体流程

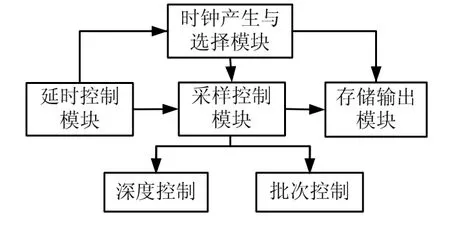

采用自顶向下的设计思路,将控制电路各功能对应到各个具体设计模块,将系统划分为以下4个模块:时钟产生与选择模块、延时控制模块、深度和批次控制模块、存储输出模块。其组成如图1所示。

图1 系统组成

其中,时钟产生与选择模块的主要功能是对外部输入的2个时钟信号源进行选择,并输出其中一个作为整个控制系统的主时钟;时延控制模块的主要功能是接收到触发脉冲后,对其进行规定时长延迟处理后,输出使能信号至采样深度和批次模块;深度和批次控制模块的主要功能是在时延控制模块使能信号的控制下,按照规定深度和批次对信号进行采样,并产生写地址、读地址和存储输出使能控制信号至存储和输出控制模块;存储和输出模块的主要功能是在深度和批次控制模块写地址、读地址和存储输出使能信号的控制下,对输入采样信号进行缓存和输出。

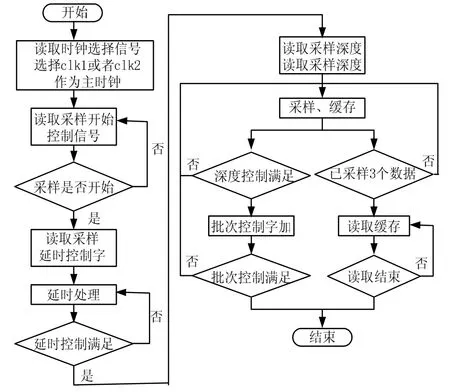

系统工作流程如图2所示,可归纳为4步。①读取时钟选择信号,进行主时钟选择;②等待采样触发信号,收到,系统跳入下一步,否则等待;③读取采样延时控制字,并延时处理,满足控制要求跳入下一步,不满足则继续延时处理;④读取采样深度和批次控制字,对输入信号进行采样、缓存、读取处理,满足控制要求停止操作转入初始等待状态,不满足则继续处理。需要指出的是,存储操作和读取操作之间有3个时钟差,外部表现为RAM存储操作第3个采样数据后,读取操作开始。

2.2 各模块实现方案

2.2.1 时钟产生与选择模块

该模块在设计时采用模块库中的ALTCLKCTRL元件。其工作原理是通过时钟选择器通过电平变化控制20 MHz和20.32 MHz时钟输出。

2.2.2 延时控制模块

延时控制模块的工作原理是接收到采样使能信号后,通过比较器对计数结果与延时控制字进行比较后,到达延时规定时间时产生采样开始使能信号,并输出至后续模块,延时时间为16、32、64、128、512、1024、2048、4096 个采样时间。

图2 系统总体流程

2.2.3 深度和批次控制模块

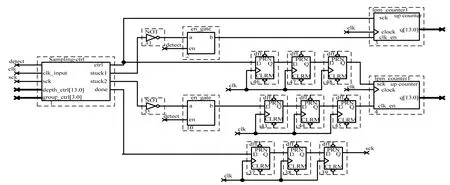

如图3所示是深度和批次控制模块的设计原理图,可看到该模块由深度和批次控制部分、写地址产生器、读地址产生器3部分组成。

图3 深度和批次控制模块

深度和批次控制部分由非门、D触发器、“sampling_ctrl”和 “en_gate”块构成。现对“sampling_ctrl”4 个输出端口的功能进行简要说明:①“ctrl”:当完成1个批次的采样后,输出一个脉冲,对地址产生器进行清零。完成全部批次采样后,保持高电平“1”;②“stuck1”:经过非门和“en_gate”处理,产生写计数器和写存储器的使能信号“wren”;③“stuck2”:经过非门、“en_gate”和延迟处理,产生读计数器和读存储器的使能信号“rden”;④“done”:采样结束后,产生清零脉冲,输出至延时计数、地址计数、存储输出等模块。

地址产生器,利用模块库中的LPM_COUNTER元件,将时钟、使能和清零信号“ctrl”分别接入对应端口,实现对存储输出模块的地址选择。

2.2.4 存储输出模块

该模块采用模块库中的LPM_RAM_DP元件,其工作原理是在写地址、读地址和存储读取使能信号的共同控制下,对端口输入的采样数据进行缓存和读取输出。

3 实验验证

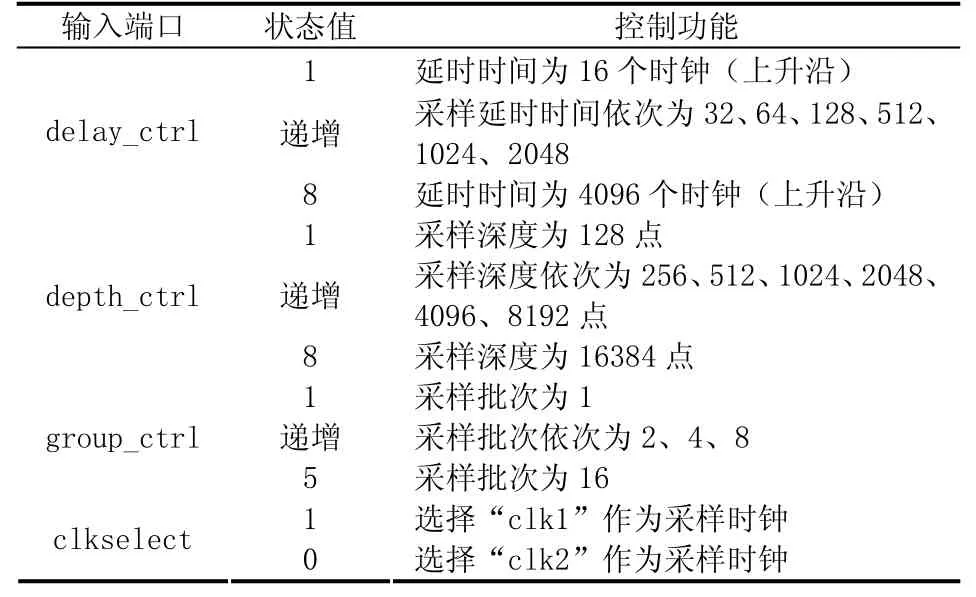

采用Quartus Ⅱ[6]Simulator进行时序仿真和功能验证。如表1所示。

表1 主要控制端口功能说明

通过对上述控制端口的选项进行逐个测试,时序仿真结果均满足预定的各项要求。

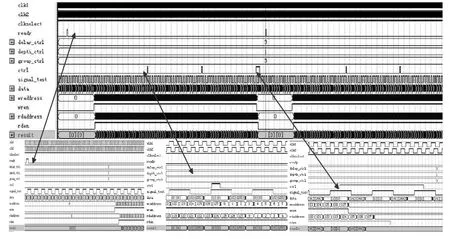

现选择时钟“clk1”,延时64个时钟、深度控制128点、批次控制3为例进行仿真验证。结果如图4所示,在对“ready”触发脉冲进行 64个时钟延迟后,采样控制电路对测试信号进行采样存储操作,经过3个时钟的延迟处理后,对存储的采样数据进行同步读取。

在每批次完成后,写地址和读地址计数器分别进行清零操作,值得注意的是由于读地址计数器计数开始时间稍晚于写地址计数器,故其清零也较写地址计数器有所延迟。最后,在所有采样缓存、读取操作完成后,各控制端口收到清零信号,恢复等待状态。

图4 系统时序仿真验证

对其他参数做了相应仿真验证,实现了此控制电路的各项功能,限于篇幅,不再赘述。

4 结语

基于FPGA平台,采用原理图设计输入和硬件描述语言设计输入相结合的方式,实现了可变参数数字采集器的多采样率、多深度、多批次以及多采样时延控制功能。电路的设计提高了数据采集的直观可控性,参数调节方便,有重要的应用价值,进一步可增加其他如显示、绘图、打印的功能并可实现可视化的人机界面。实际测试和应用表明,可广泛应用各种过程控制和自动化过程中。

[1] 牛国朋,袁洪,范建军.一种基于FPGA和DSP的高性能PCI数据采集处理卡设计[J]. 《微计算机信息》(嵌入式与 SOC)2006(22):137-139.

[2] 朱志亮,邱绍峰.基于FPGA的STM-1数据采集卡的硬件设计[J].通信技术,2007,40(11):262-264.

[3] 王永水,任勇峰,焦新泉.基于FPGA的160路数据采集系统设计[J].国外电子元器件,2008(10):4-5.

[4] 乐健,陈绍伟,吴婷婷.基于FPGA的PCI接口的设计与实现[J].信息安全与通信保密,2010(05):41-43.

[5] 姜立东.VHDL语言程序设计及应用 [M]. 第2版.北京:北京邮电大学出版社,2004:152-168.

[6] 褚振勇 齐亮.FPGA设计与应用 [M].第2版.西安:西安电子科技大学出版社,2006:139-179.