一种板间高速传输系统的设计与实现

刘丽格,李天保,石鑫刚

(1.中国电子科技集团公司第五十四研究所,河北石家庄050081;2.河北先控电源设备有限公司,河北石家庄050035)

0 引言

随着数字信号处理技术的飞速发展,数字信号处理设备的速度和复杂度不断提高。相应地,系统对数字信号传输带宽的要求也不断增加。对一个数字处理设备而言,板间数据传输带宽已经成为限制设备性能的瓶颈之一。

提升并行传输带宽需要解决2个问题,一是提高FPGA输入输出接口的比特速率,另一个是解决多路并行信号间的时延不一致的问题。

1 实现方法

由于FPGA内部逻辑单元处理速率有限,要实现数据的高速传输需要利用FPGA内部与每一个输入输出(I/O)单元相连的并串转换核(OSERDES)和串并转换核(ISERDES),OSERDES可以把FPGA内部的并行低速数据转换为高速串行数据,ISERDES可以把输入的高速串行数据转换为低速并行数据。如果把多路这样的串行数据并行进行传输,就可以实现更大的传输带宽。

然而,通过底板并行高速传输数据不可避免地造成了数据线与时钟线之间、数据线与数据线之间时延不一致的问题。为解决此问题,可以利用FPGA每一个I/O管脚的输入输出延时(IODELAY)单元。IODELAY相当于是一段延迟线,该延迟线以大约78 ps为步进单位,最大可实现64阶时延。因此,通过调整延迟线的时延,可以精确控制输入信号到达FPGA内部的处理逻辑单元的相位,进而对多路信号之间在底板上传输的时延不一致进行补偿。

2 设计方案

板间高速同步并行数据传输的示意框图如图1所示。发送方将较低速率的并行数据送入发送模块,发送模块将其转换为的高速数据信号,并以低电压差分信号(LVDS)标准的双数据速率(DDR)接口形式通过底板发送到接收方。接收方的接收模块将每一组数据恢复成原始的并行数据及相应的时钟,并以该时钟存入先进先出存储器(FIFO),并利用同一个读时钟和统一的复位信号将各路信号完全同步恢复。

图1 板间高速数据传输的框图

板间高速数据传输的方案中主要包括发送模块、底板、接收模块和跨时钟域同步模块几个部分组成。

2.1 发送模块

在发送模块内部,输入的64 bit数据按8 bit分组,分成8组。每一组8 bit数据送给FPGA内部的OSERDES模块转换成8倍数据速率的单比特信号,再送给单端转差分单元从FPGA管脚送出。而时钟需要通过双数据速率输出(ODDR)模块和单端转差分单元从FPGA管脚送出。因此发送模块内部不需要更多的逻辑控制,仅仅是工作数据和训练序列之间需要一个选择器,由监控选择将哪一种数据送出。通常在系统初始化阶段控制将训练序列发送出去,在检测到接收方已完成校准后再切换到工作数据流。

2.2 底板传输模块

LVDS差分信号线在底板上传输不需要额外的驱动电路,也不需要差分端接电阻,只需要将所有差分信号线引入到接收方的FPGA即可。因为在FPGA内部存在差分转单端的硬件单元,该硬件单元有一个高直流输入阻抗,几乎所有的驱动电流都将流经100 Ω终端电阻产生约350 mV电压。其特有的低振幅和恒流源驱动模式只产生极低的噪声,消耗很小的功率。但底板的设计中必须考虑信号线的阻抗设计和等长设计。尽管在接收方将对数据传输时延进行校准,但由于FPGA内部的校准范围是有限的,还是需要尽可能在设计中保证信号时延在可调整的范围以内。

2.3 接收模块

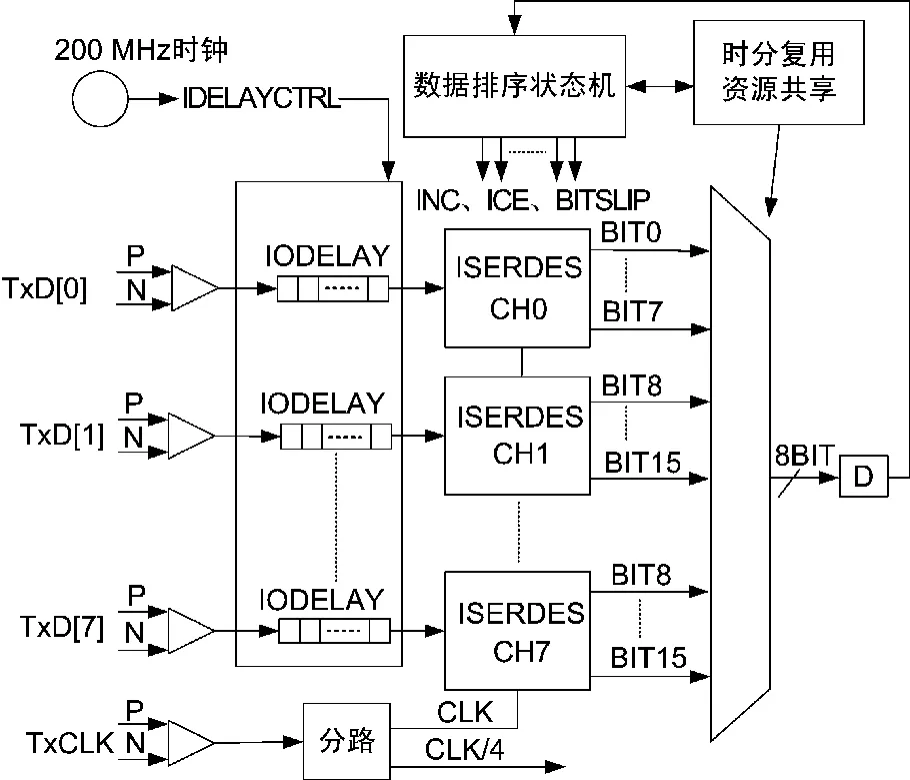

接收方首先需要对输入数据按照与发送方相反的流程执行差分转单端、DDR转单数据速率(SDR)和串行化转并行的步骤以外,还需要进行时延校准、比特排列(BIT ALIGNMENT)、字排列(WORD ALIGNMENT)及跨时钟域数据同步等操作。其中接收模块的实现示意框图如图2所示。

图2 接收模块实现示意框图

图中每一个ISERDES都会将输入的单高速数据转换为8 bit低速并行数据,8个ISERDES接收从底板传来的8位高速数据,转换为64 bit低速数据。所有的8组8 bit数据都被送入一个数据选择器,由一个时分复用/资源共享控制模块在一段时间内选择一组数据送入数据排序模块,以减少逻辑资源的消耗。数据排列状态机产生3个控制信号,分别是INC、ICE和 BITSLIP。其中 INC和 ICE能够造成IODELAY产生对输入信号以75 ps步进递增和递减的时延。而BITSLIP可以使ISERDES将并行输出数据比特的顺序进行循环移位,进而实现与训练序列的比较。

数据排序状态机是整个接收模块的核心控制部分,它主要实现2部分功能:一是比特对齐;二是字对齐。比特对齐就是通过调整数据信号的时延把时钟的采样沿尽量对准数据窗口的中心。而字对齐是为了确保ISERDES输出的并行数据位以正确的排列顺序输出。比特对齐的步骤如图3所示。

图3 比特对齐步骤

整个比特对齐过程会测量出一个完整的数据眼图(以78ps数据时延为步进),并返回到该眼图的中心点。其中搜寻跳变点需要考虑数据传输过程中的抖动问题,从而避免第2个跳变点的错误检测。

为了正确判断出跳变的位置,需要考虑2种数据抖动的情况。第1种情况是随机抖动的情况。在这种随机抖动的情况下,通过把当前采样值与上一次采样值作比较,从比较结果就可以决断出跳变的起始和结束时刻。第2种情况是确定性的抖动,在这种情况下,FPGA程序检测不到前后2次采样值的不同,但是采样值与已知的训练序列是不同的。这就需要利用ISERDES的BITSLIP特性。

比特对齐确保数据位被可靠地获取,但数据位的顺序可能与发送方所期望的顺序有所不同。字对齐操作利用ISERDES单元的BITSLIP功能实现顺序调整。由于在系统初始化校准阶段发送方发送的是训练序列,这对于接收方是已知的。接收方就不断执行比特滑动直到ISERDES输出的数据与训练序列完全一致为止。

2.4 跨时钟域同步模块

所有的发送方数据在送入接收方后经各自的接收模块恢复出了低速的64 bit的数据和与之对应的时钟。尽管所有发送方的时钟都是由同一个时钟源产生的,在频率上完全相同,但由于路径的不一致会造成各路时钟会存在相位差。为了用同一个时钟对所有数据进行处理还需要进行同步化操作。这种操作是利用FPGA内部的异步FIFO来实现的。异步FIFO是指用一种时钟执行写入操作,而用另外一种时钟执行读出操作,这2种时钟是异步的。每一路数据都以其随路时钟被写入到一个异步FIFO中,所有FIFO的读操作都采用同一个时钟。这个时钟可以是与发送方同源的另一种时钟,也可以直接从接收过来的多个时钟中选出一路使用。因而确保了读时钟的速率与写的速率一致,不会由于时钟频差累积造成FIFO的写满或读空。

3 测试结果

设计中发送方与接收方都采用赛灵思(Xilinx)公司的Virtex4系列XC4VLX160型号FPGA芯片,底板接插件也采用标准CPCI的接插件。在一台21槽CPCI工控机上进行实验,对20个槽位的板间互连进行测试。以单根数据线的比特传输速率为参考,采用传统的并行传输方式测试,传输速率最高可达到400 Mbit/s,而有的板卡间只能达到约200Mbit/s,这与布线和接插件造成的时延一致性有关。而采用该文中的高速板间传输技术,全部的板间传输测试都达到800 Mbit/s,测试30 min无误码。特别重要的是,由于带有硬件的自动校准功能,调试工作量大大减少。

4 结束语

数据传输性能是设备硬件设计必须充分考虑的基本问题之一,如何挖掘硬件平台的数据传输潜力,寻找有效增加传输带宽的方法,成为了一项非常具有现实意义的课题,也是衡量硬件性能的一项重要指标。这种板间高速传输技术降低了对硬件外围电路的要求,结合高速串行传输的部分特性,突破了传统并行传输的比特速率限制,为数字信号处理能力的提高提供了支持。

[1]赵增辉,刘中友,彭圻平.高速差分信号的互连设计[J].无线电通信技术,2010,36(1):50-56.

[2]胡锦,彭成,谭明.基于RocketIO的高速串行协议设计与实现[J].微计算机信息,2008,24(18):196-197.

[3]武荣伟,苏涛,翁春蕾.基于FPGA的高速数据传输方案设计与实现[J].重庆邮电大学学报,2010,22(2):205-208.

[4]史小波,程梦璋,许会芳.集成电路设计VHDL教程[M].北京:清华大学出版社,2005:145-147.

[5]杨翠红,文丰,姚宗.基于LVDS的高速数据传输系统的设计[J].通信技术,2010,43(9):59-64.

[6]陈长林,邱兆坤.Rocket I0及其在高速数据传输中的应用[J].单片机与嵌入式应用,2010(11):25-28.

[7]薛隆全,文丰,张时华.基于LVDS总线的高速长距数据传输的设计[J].电子设计工程,2009,17(2):39-42.

[8]马将,任勇锋,李圣昆.LVDS远程传输中继电路的设计应用[J].通信技术,2010,43(1):26-28.