航天用SRAM型FPGA抗单粒子翻转设计

马 寅

(中国空间技术研究院 载人航天总体部,北京 100094)

0 引言

在日益复杂的航天器电子系统中,用户可配置的 FPGA由于其功能配置的多样性与可重复性以及进行海量数据处理时的灵活性与高效性,逐渐承担起更多的任务。

然而,采用SRAM工艺的FPGA受空间高能粒子影响较大,其内部配置存储器的逻辑状态常常由于粒子撞击而翻转,即发生单粒子翻转(SEU)。如果翻转发生在逻辑功能区,可能导致航天器的功能中断;如果翻转发生在RAM单元,可能导致数据错误或者丢失[1]。

近年来,针对SEU的容错研究有了很大发展。随着SRAM型FPGA不断的技术革新,容错技术也呈现多样化。总的来说,SRAM型FPGA的容错技术分为两大类:第一类是作用于前端的SEU屏蔽,包括各种抗辐射加固结构设计、新的高性能抗辐射CMOS工艺等[2]。这类技术可以带来抗辐射能力的显著提高,但一般都要在附带性能上作出牺牲,如可实现的高速时钟频率往往要下降一半以上,实现成本也由于对工艺的更改而大大增加。第二类是作用于后端的SEU恢复,如错误检测和纠正编码(EDAC),以及 Xilinx公司提出的刷新(scrubbing)、回读检测等[3]。这类技术在实现成本和性能牺牲上要优于第一类,但由于翻转形式多样,同样不能保证百分之百的容错。

只有同时结合两类容错技术,既做到前期尽量避免翻转发生,也做到后期尽量恢复已经发生的翻转以避免其累积,才可以获得最佳的抗辐射性能。前期屏蔽的设计方法已经比较成熟,本文将着重讨论针对Xilinx公司高性能的Virtex系列FPGA的抗SEU设计对配置逻辑部分采用回读比较后刷新;对 Block RAM部分采用通用自纠错宏[4-5]的容错设计方案。

1 SRAM型FPGA原理简介

1.1 配置原理

SRAM型 FPGA用户编程功能的实现依赖于数百万配置锁存器中存储的数据。数据帧是配置数据在FPGA配置存储器中可以读写的最小单位。多组配置帧组成一个配置帧列,配置帧列根据功能的不同,细分为CLB帧列、IOB帧列、IOI帧列、GCLK帧列、BRAM帧列和BRAM内连帧列。这些帧列可以被划分为3类:CLB帧块(包括GCLK、CLB、IOB、IOI帧列),BRAM 帧块,BRAM 内连帧块[6]。一个完整的配置文件就是由所有配置位置的帧信息和一些必要的首位命令字所组成的。

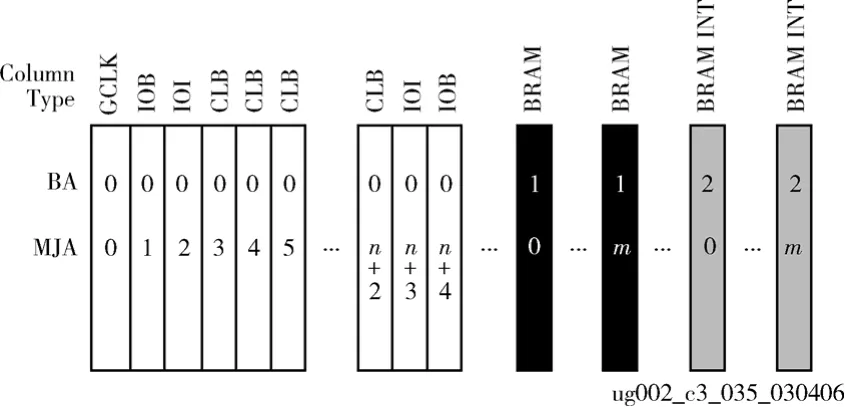

帧是可寻址的。帧地址分为块地址(BA)、主地址(MJA)和从地址(MNA)3部分,如图 1所示。块地址对应3个帧块,主地址指明了块地址下某帧列的位置,从地址指明了帧列中某特定帧的位置。由这3个地址就可以准确地定位到一个配置数据帧了。

为了引导和辅助配置,FPGA内部设计了一些专用于配置的32 bit的配置寄存器,例如帧地址寄存器(FAR)、帧数据输入寄存器(FDRI)、控制寄存器(COL)等都对配置、刷新、回读等操作起关键作用。

图1 Virtex-II FPGA内部配置架构Fig.1 Virtex-II FPGA configuration architecture

1.2 刷新

配置数据中一个位(bit)的翻转不一定直接导致FPGA发生功能故障,这是由于翻转的位置可能恰好不在FPGA编程布线区。然而,如果不及时采取恢复措施,翻转位数量会不断累积,达到一定程度终究会导致功能错误。刷新的直接功能就是阻止翻转位的累积。

刷新就是在FPGA已经上电配置成功之后,不事先擦除已有的逻辑,就直接重新写入配置数据且不中断用户的功能。理论上来说刷新也属于部分重配置,目前只有Xilinx公司的Virtex系列FPGA支持刷新[6-7]。

为了实现刷新,有几点需要注意:

1)在设计中不能使用SRL16和分布式RAM。因为刷新会将其初始化,导致其实时状态的丢失。

2)只有JTAG和SelectMAP可以被用于刷新。需要配置端口在配置后保持配置功能,不被复用为普通IO口。另外,启动时钟(start-up clock)必须被设置为CCLK。

1.3 回读比较

回读是在 FPGA配置完成后将其内部配置锁存器中的数据读出的过程。回读的操作也不会影响FPGA的正常工作[6,8]。

回读时,用户可以读出所有的配置信息,甚至连用户存储单元如LUT RAM、SRL16、BRAM中的实时数据也可以读出。但是如果在线回读存储单元中的实时数据,可能导致FPGA死锁。一般回读时将跳过这些部分,对存储单元的容错另外处理。

与刷新相同,回读只能通过 SelectMAP或JTAG配置接口进行,同样也需要在配置后进行功能保持。

回读出数百万配置锁存器中的 FPGA配置信息后,将其与原始配置文件进行逐位对比。如果有不同,则说明可能有单粒子翻转,且能同时准确定位到是哪一帧数据的哪一位发生了翻转。

1.4 块RAM容错设计

块RAM(Block RAM,简称BRAM)是FPGA内部嵌入的专用RAM区,可以被配置成多种维度和尺寸的RAM,形式也多样化,单端口RAM、双端口RAM、FLASH等都可以通过设定不同的参数来实现[6]。

BRAM 存储实时数据会随着工作不断变化,如果对其进行刷新或回读操作,可能会因为影响实时数据进而影响到FPGA的正常工作,导致死锁或其他故障。因此对BRAM的容错设计不同于配置逻辑部分,简单的三模冗余设计效果不明显,一般需要有对实时数据的检测、存储和恢复处理功能。Xilinx公司提供了一种自纠错宏[4],将其应用到BRAM中可以自纠正发生在BRAM中的翻转。

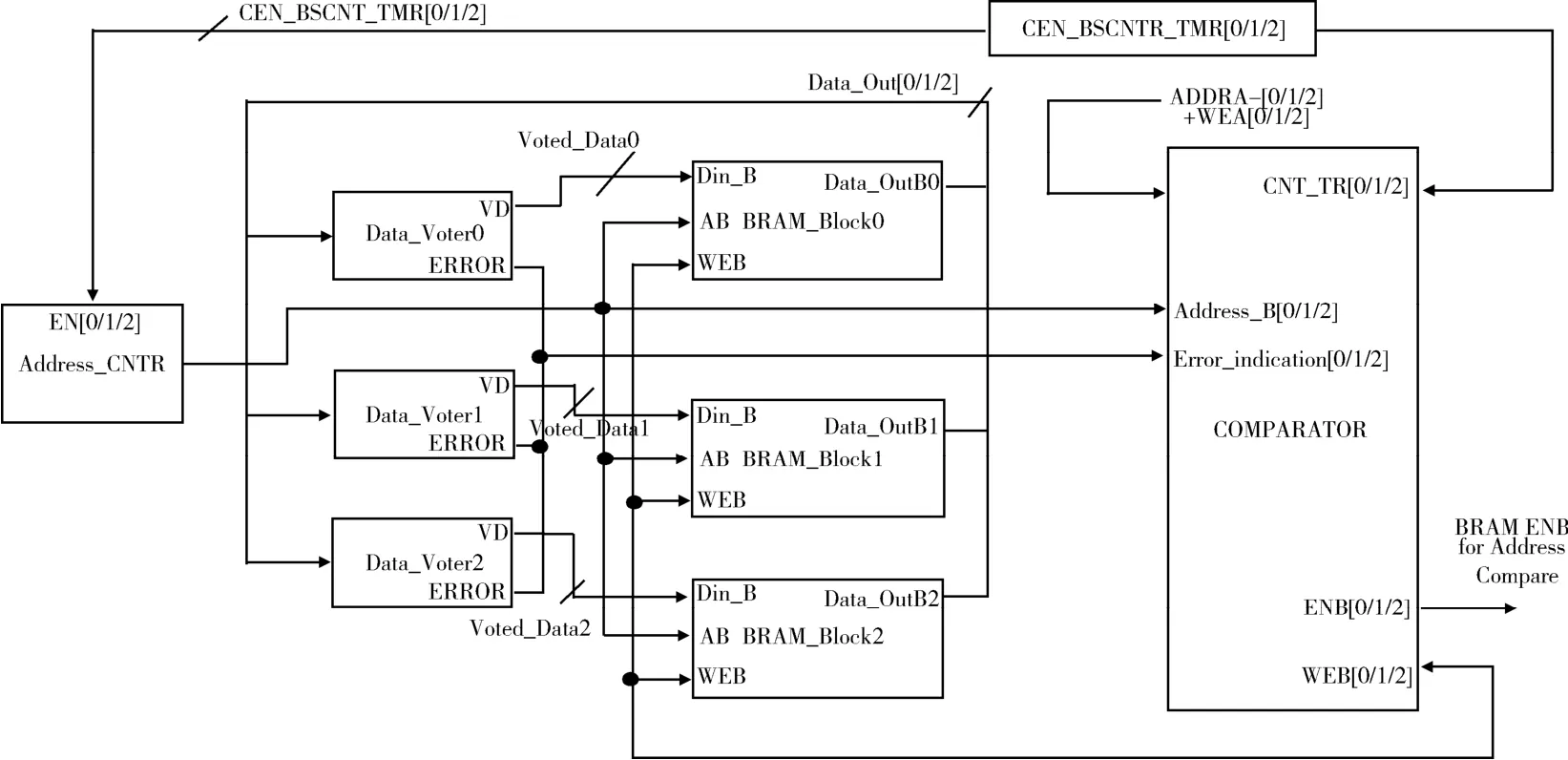

这种BRAM自纠错宏的容错算法如图2所示:

1)BRAM做三模冗余设计,各BRAM设计有地址计数器端口AB。

2)各 BRAM 均有一个数据输出端口 Data_OutB,同时输出同一个地址的3个BRAM单元数据,用于表决。

3)从Data_OutB输出的3个BRAM的数据经表决后作为Din_B的输入数据。

4)如果检测到错误,WEB(Write Enable B)激活并纠正BRAM中的翻转。各BRAM的地址计数器将暂时不工作。

5)纠错过后,令地址计数器恢复工作,继续计数。开始下一个BRAM地址单元的检错纠错。

图2 Block RAM自纠错宏容错图解Fig.2 Diagram of fault-tolerant function of self-correction macro for block RAM

2 FPGA抗SEU设计

本文提出的FPGA抗SEU设计综合了回读比较(检错)、刷新(纠错)和BRAM自纠错宏(特殊处理)3种抗SEU措施[7,9-10]。

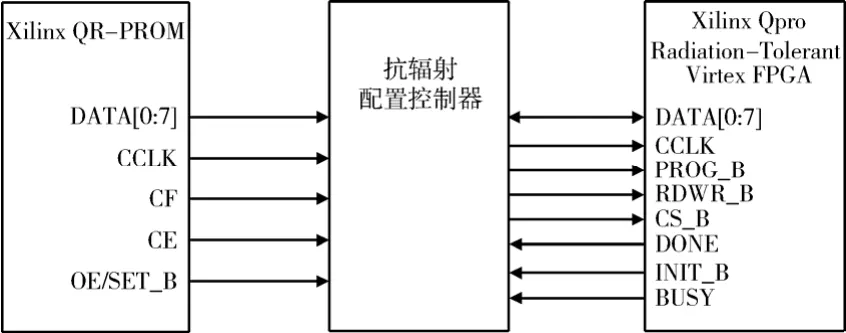

如图3所示,执行回读比较和刷新操作的核心控制由一块具有高抗辐射性能的芯片完成,如ASIC或反熔丝的 FPGA;核心控制芯片一侧是具有高抗辐射性能的存储芯片,用于存储 Virtex FPGA的配置文件(.bitsream或其他格式);另一侧是Virtex FPGA,完成用户功能。

图3 FPGA抗SEU设计框图Fig.3 Diagram of FPGA SEU-tolerant design

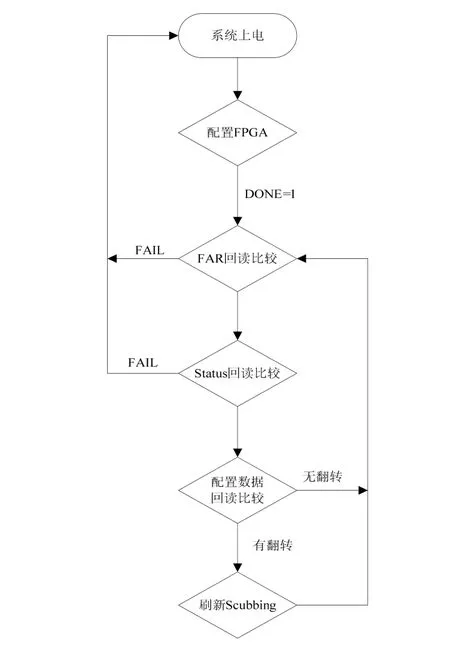

容错处理流程如图4所示:

1)系统上电。

2)控制芯片从外部存储芯片导入配置文件到FPGA。

3)完成配置,DONE信号跳高,FPGA开始正常工作。

4)回读比较FPGA帧地址寄存器中的数据。如果相同,则进行下一步;不相同,则需要重新上电配置。

5)回读比较FPGA状态寄存器中数据判读,如果正常,进行下一步;不正常,则需要重新上电配置。

6)回读比较FPGA数百万配置锁存器中的数据,和外部存储芯片中的原始配置信息逐位对比。如果相同,重复回读比较流程;不相同,则需要刷新纠正。

图4 容错设计流程图Fig.4 Flow chart of fault-tolerant design

控制芯片触发刷新纠正的流程后,步骤如下:

1)对FPGA的多个配置寄存器重新设置,做好刷新准备。

2)以特定的顺序将外部存储芯片中的配置数据写入FPGA中,完成数百万配置锁存器中数据的更新。

3)再重复执行一次刷新,保证对已发生翻转的纠正。

对BRAM采取特殊处理方法,使用Xilinx提供的通用自纠错宏替换用户的RAM设计。如一个单端口 RAM,将通过修改综合后的网表文件(.ngc),被替换成 3个拥有冗余表决和比较、纠错功能的RAM,之后使用新的网表文件布局布线,完成对BRAM的容错设计。步骤如下:

1)设置宏参数,如BRAM的宽度、深度,是否读使能等。

2)综合生成一个地址计数器的网表。使用XTMR工具(Xilinx的TMR实现软件)对地址计数器做三模冗余。

3)生成一个BRAM自纠错模块的网表。

4)综合用户设计,生成原始网表文件。

5)用BRAM自纠错模块的网表替换用户设计中的BRAM网表。

6)使用新网表文件进行布局布线。

3 抗辐射设计效果评测

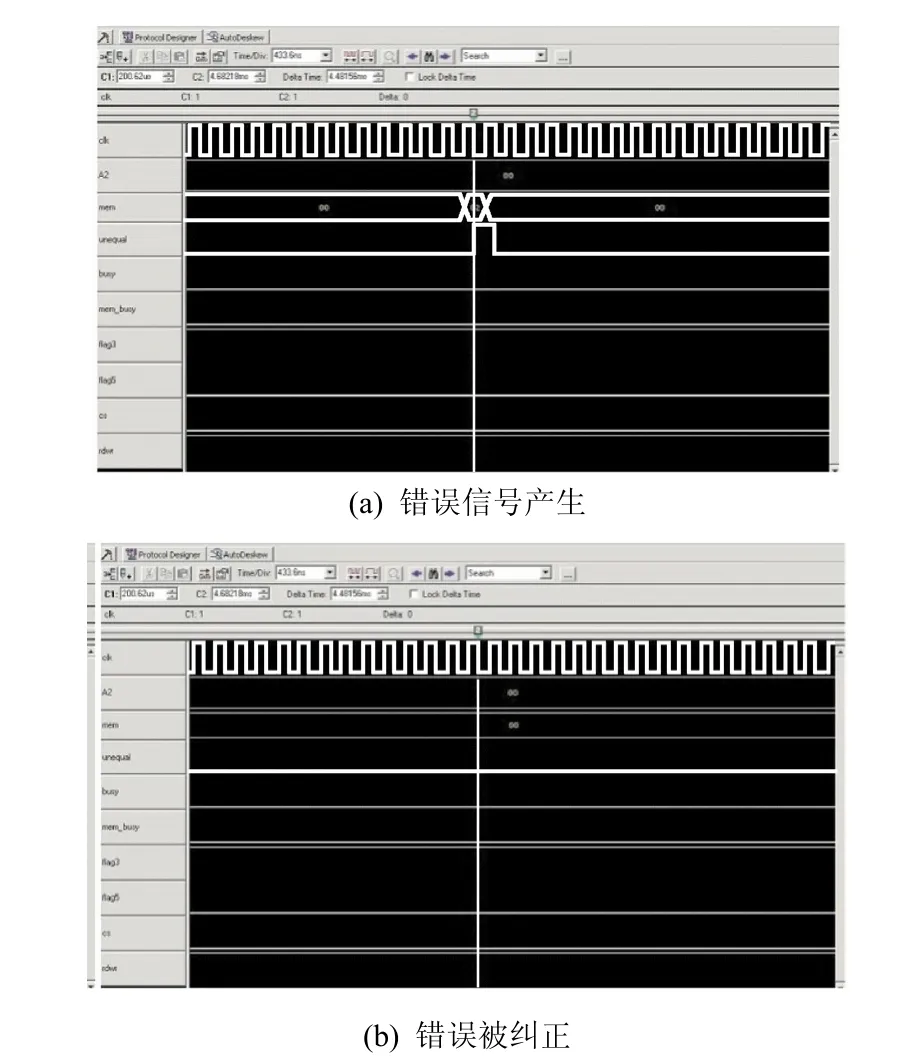

图 5所示为对回读比较出错后进行刷新纠正的效果。产生高电平跳变信号后(图 5(a)),停止回读比较,执行一次刷新操作;之后再执行回读比较,该错误被纠正(图5(b))。

为实现本设计,相比普通实现方案,增加了一块控制芯片,占用了一定的PCB面积;功耗也有相应的增加,执行回读/刷新时将增加约0.25 W;由于使用自纠错宏对 BRAM 进行处理,占用了 3倍多的芯片内RAM资源。然而,一定的性能牺牲换来了较高的空间应用可靠性。

文献[11]对SRAM型FPGA进行了单粒子翻转地面模拟试验,轨道分别取低地球轨道(645 km/97.9°)和地球静止轨道,卫星屏蔽厚度取3 mm铝,空间辐射环境取 90%最坏情况(M=3)。结果为:FPGA配置区在低地球轨道,每天会出现2.55次翻转;在地球静止轨道,配置区每天会出现 7.96次翻转。每翻转1次,均可导致器件功能不正常。

图5 SRAM型FPGA纠错前后对比Fig.5 Comparison before and after read-back & scrubbing of SRAM FPGA

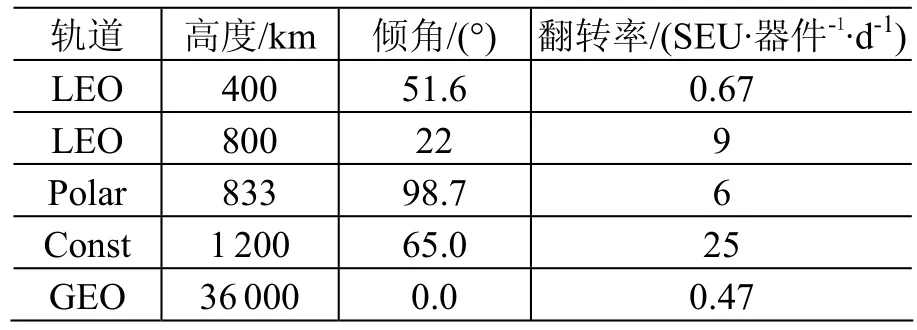

文献[10]中提到Xilinx与JPL联合测试计算出的不同轨道情况下Virtex-II 600万门FPGA的翻转率,如表1所示。

表1 XC2V6000在不同轨道的翻转率Table1 SEU rates of XC2V6000 on different orbits

按照最恶劣情况考虑,SEU发生率也在10次/(器件·d)以下。本文提出的容错设计方法是将对配置存储数据进行周期性的回读比较和刷新,而经验之法是将回读速率和刷新速率设置在高于翻转率一个数量级或更高一些[12]。最后实现时,回读/刷新的速率可以达到300 ms/次,这个速率远远大于翻转率。

简单的故障注入(修改个别配置位)能够验证功能的可靠性,然而如果应用于航天器,则需要完备的统计结论。

对SEU缓解措施的评测瓶颈在于故障注入的方法。目前主流的故障注入方法有3种:

1)采用Jbits SDK软件。该软件工具是由Xilinx提供的一个Java类的集合,它为Xilinx Virtex系列FPGA提供配置位流的应用接口(API),使得配置位流可以伪随机或定位方式修改,从而达到整片故障注入的目的。

2)代码仿真。采用VHDL等设计语言来仿真存储器等相关部件(Latch、FF、Register、RAM)和组合逻辑节点中的SEU,具体可参考文献[13-14]。这种方法的优点在于故障注入参数灵活、周期短、对所有敏感部分均可自由访问,但实现较复杂。

3)外部辐射模拟。外部辐射主要分为激光辐射和高能粒子辐射两大类。无论哪种方案,首先需要去除芯片外壳封装。激光能够穿透较深的深度,且对器件不会有硬件损伤,但是不能穿透金属工艺层,因此需要选用倒装芯片;高能粒子束可以穿透金属,目前北京大学的重离子实验室以及中国科学院兰州高能物理研究所等均可以对正面打开封装的FPGA进行高能粒子辐射,但辐射深度有限,难以达到Virtex-II系列FPGA的敏感深度。

本文的SEU缓解设计方案目前正在中国科学院国家空间科学与应用研究中心的激光效应实验室进行激光辐射注入评测,完备的统计结论有待进一步的计算和研究。

4 结束语

SRAM型 FPGA对单粒子翻转敏感,其空间应用必须进行加固和容错设计。除通常采用的三模冗余及外部增加屏蔽层之外,本文提出用回读比较进行检错、用刷新进行纠错、用BRAM自纠错宏作为特殊处理方案的解决措施,在牺牲一定的器件性能的情况下,能达到较好的抗SEU效果,为航天电子产品抗单粒子翻转设计提供了一种解决方案。

(References)

[1]邢克飞, 杨俊, 王跃科, 等.Xilinx SRAM型FPGA抗辐射设计技术研究[J].宇航学报, 2007, 28(1): 123-129

Xing Kefei, Yang Jun, Wang Yueke, et al.Study on the anti-radiation technique for Xilinx SRAM-based FPGA[J].Journal of Astronautics, 2007, 28(1): 123-129

[2]冯彦君, 华更新, 杨桦周, 等.国外星载容错计算机技术及最新进展[C]∥全国第十二届空间及运动体控制技术学术会议论文集.北京: 中国自动化学会空间及运动体控制专业委员会, 2006: 452-457

[3]徐斌, 王贞松, 陈冰冰, 等.适用于空间环境下的FPGA容错与重构体系[J].计算机工程, 2007, 33(3): 231-233

Xu Bin, Wang Zhensong, Chen Bingbing, et al.Architecture for fault-tolerance and reconfiguration of FPGA in aerospace[J].Computer Engineering, 2007,33(3): 231-233

[4]Xilinx Inc.Single-event upset mitigation for Xilinx FPGA block memories[EB/OL].(2008-03-14).http://www.xilinx.com/support/documentation/application_notes/xapp962.pdf

[5]张钰, 郑阳明, 黄正亮, 等.皮卫星星载计算机存储模块的容错结构设计[J].宇航学报, 2008, 29(6): 2057-2061

Zhang Yu, Zheng Yangming, Huang Zhengliang, et al.Fault-tolerant design of memory module for pica-satellite on-board computer[J].Journal of Astronautics, 2008,29(6): 2057-2061

[6]Xilinx Inc.Virtex-II platform FPGA user guide[EB/OL].(2007-11-05).http://www.xilinx.com/support/documentation/user_guides/ug002.pdf

[7]Xilinx Inc.Correcting single-event upsets in Virtex-II platform FPGA configuration memory[EB/OL],(2007-02-19).http://www.xilinx.com/support/documentation/application_notes/xapp779.pdf

[8]Carmichael C.SEU mitigation techniques for Virtex FPGAs in space applications[C]//Proc of 2ndMAPLD(poster paper), 1999: 24-34

[9]Bolchini C, Miele A, Santambrogio M D.TMR and partial dynamic recongurationto mitigate SEU faults in FPGAs[C]//Proc of 22ndIEEE International Symposium on Defect and Fault-tolerance in VLSI Systems.Washington D.C., USA, 2007: 87-95

[10]Xilinx Inc.Xilinx defense and aerospace presentation[EB/OL].[2011-10-06].http://www.xilinx.com/publications/prod_mktg/MilAero.pdf

[11]于庆奎, 张大宇, 张海明, 等.SRAM FPGA电离辐射效应试验研究[J].航天器环境工程, 2009, 26(3): 229-231

Yu Qingkui, Zhang Dayu, Zhang Haiming, et al.Tests on total dose effects and single event effects on SRAM FPGA[J].Spacecraft Environment Engineering, 2009,26(3): 229-231

[12]Kastensmidt F L, Carro L, Reis R.Fault-tolerance techniques for SRAM-based FPGAs[M].Springer, 2006

[13]DeLong T A, Johnson B W, Profeta J A.A fault injection technique for VHDL behavioral-level models[J].IEEE Design & Test of Computers, 1996,13(4): 24-33

[14]Lima F, Rezgui S, Carro L.On the use of VHDL simulation and emulation to derive error rates[C]//Proceedings of European Conference on Radiation and Its Effects on Components and Systems, 2001: 253-260