基于CPCI总线的短波调制解调板卡电路设计*

张佳炜

(中国舰船研究院 北京 100192)

1 引言

Compact PCI是一种基于标准PCI总线的小巧而坚固的高性能总线技术。1994年PICMG(PCI Computer Manufacturers Group,PCI工业计算机制造商联盟)提出了Compact PCI技术,它定义了更加坚固耐用的PCI版本[1]。

系统控制器是某短波通信系统的核心,用于系统时序控制,通信频率选择与转换控制,用户数据的调制发送和解调接收等,实现系统通信控制功能。而调制解调卡是系统控制器的重要组成部分,完成通信时发送数据的编码调制和接收数据时的同步、均衡、解调、译码等功能。

2 短波调制解调板卡电路总体设计

2.1 电路主要功能需求

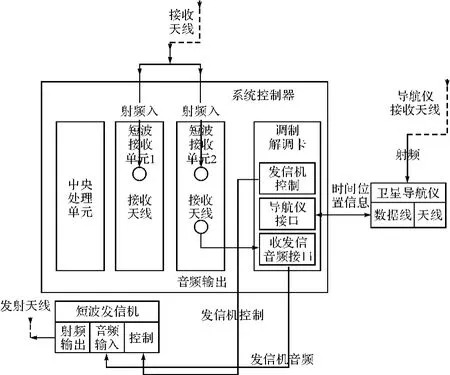

图1为某短波通信系统的组成框图,由系统控制器、接收天线、发射天线、短波发信机、卫星导航仪、导航仪接收天线等组成。该通信系统主要工作过程为:发送过程,系统控制器控制发信机切换到指定的发送频率,将编码后的用户数据调制成音频信号通过发信机发射出去,实现数字信号的无线发送;接收过程,系统控制器接收来自接收天线的短波信号,将信号转换为音频,再将音频信号进行解调、译码,最终实现无线信号的数字接收。

系统控制器基于CPCI 6U结构,由中央处理单元、短波接收单元1、短波接收单元2、短波调制解调卡等CPCI接口卡以及CPCI 6U机箱组成。各接口卡通过CPCI总线完成数据交互,其中CPU卡运行基于Linux的用户程序,完成用户数据的产生、分组、排序等功能;短波接收单元1进行短波频谱的监测,选择通信频率;短波接收单元2主要功能是将接收的短波信号转换为音频信号。系统控制器中的短波调制解调卡有以下几个功能:1)完成与系统控制器CPU卡的用户数据的交互;2)完成用户数据的编码调制(发送时)和解调译码(接收时);3)完成与短波接收卡的接口,对音频信号进行数字化处理;4)完成与短波发信机的接口,控制发信机的状态,将待发送的音频信号传送给发信机;5)完成与卫星导航仪的接口,对导航仪状态进行控制,接收卫星导航仪的定时信号;6)预留短波信道模拟器接口,方便进行实验室调试。

图1 某短波通信系统组成框图

2.2 电路设计思路及主要元器件选择

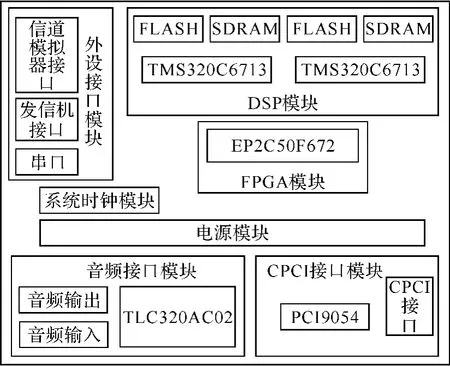

根据调制解调卡主要功能需求,采用模块化的方法将功能需求进行分解并实现。本板卡主要划分为以下7个模块:1)CPCI接口模块,完成CPCI接口总线和本地总线的协议转换,主要元器件为PCI接口芯片PCI9054;2)音频接口模块,与短波收发信机的音频信号接口,完成音频信号的数模/模数转换,主要元器件为音频数模/模数转换芯片TLC320AC02;3)外设接口模块,与短波信道模拟器、卫星导航仪、短波发信机等外设进行接口,主要元器件为CAN总线接口芯片SJA1000、RS232电平转换芯片 MAX3232等;4)DSP(数字信号处理)模块,完成用户数据的编码调制和解调译码功能,主要元器件为DSP芯片TMS320C6713;5)FPGA模块,主要功能是作为调制解调卡上各个器件间以及外设各个设备间的数据交换的桥梁,进行通信协议转换、设备控制、中断处理等功能,主要元器件为FPGA(可编程逻辑器件)芯片EP2C70F672;6)系统时钟模块,主要功能是为板卡各元器件提供所需时钟频率,主要元器件为可编程时钟芯片CY22393;7)电源模块,主要功能是为板卡各元器件提供所需电源电压,主要元器件为电压转换芯片。

2.3 电路组成框图

调制解调板卡各功能模块在电路板上的布局如图2所示。

图2 调制解调卡各功能模块布局图

3 主要功能模块设计

3.1 CPCI接口模块设计

CPCI接口模块的主要功能是通过CPCI总线完成计算机和调制解调卡的数据交互。另外,CPCI接口还为调制解调卡各个模块提供电源。CPCI模块设计思路是采用PCI桥芯片PCI9054完成CPCI总线到CPCI本地总线的转换,采用配置芯片HT93LC56完成PCI9054的配置。

PCI9054是美国PLX公司生产的PCI总线通用接口芯片。使用该专用芯片桥接PCI总线和本地总线(local bus),开发者可以省去考虑太多复杂的PCI总线规范,而集中精力开发硬件和驱动程序[2]。PCI9054有3种工作模式,分别为M模式、C模式和J模式,通过管脚Mode0和Mode1选择[3]。本调制解调卡采用C模式,本地总线32位地址/32位数据非复用。HT93C56为配置PCI9054的EEPROM,容量为2K,通过4根信号线与PCI9054的相应信号相连,主要作用是在开机时完成对PCI9054内部各个寄存器的配置。

3.2 音频接口模块设计

音频接口模块的主要功能是完成短波收发信机的音频信号和音频数模/模数转换芯片TLC320AC02的接口,转换后的数字信号经过电平转换后进入DSP芯片进行处理。

TLC320AC02是一种Texas Instruments公司出品的数模/模数转换芯片。在TLC320AC02的模拟信号端为单端音频信号,且有直流偏置[4]。而短波收发信机的接口的主要参数为:频率:300~3400Hz;电平:-10dBm~10dBm;600Ω(平衡)。所以需要采用信号整形电路将短波收发信机的平衡音频信号转换为TLC320AC02的单端音频信号。

在TLC320AC02的数字信号端,输入输出为数字化的音频信号,电平均为5V,而FPGA的接口电平为3.3V,所以需要用电平转换芯片SN74CBTD3384来实现电平转换。

3.3 外设接口模块设计

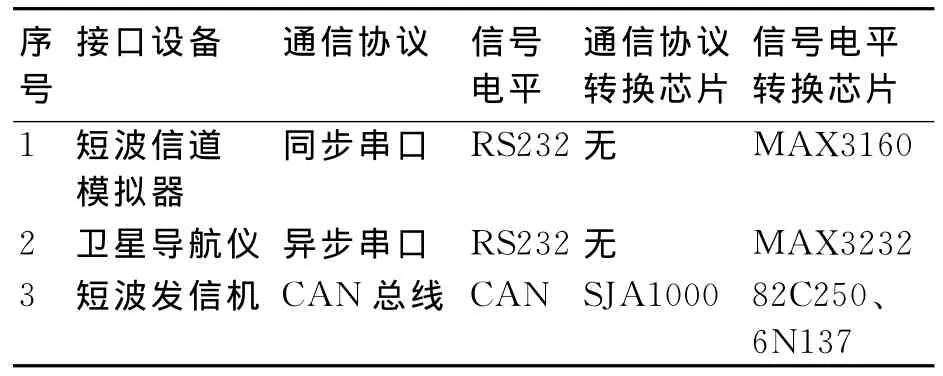

该模块的主要功能是完成调制解调卡FPGA芯片与外设设备的接口,包括短波信道模拟器、卫星导航仪、短波发信机,由于各个外设的通信协议和信号电平与FPGA不同,采用通信协议转换芯片和电平转换芯片进行转换,如表1。

表1 调制解调卡各个外设设备列表

3.4 DSP模块设计

DSP模块主要完成数据调制解调功能:1)将通过CPCI总线传来的用户数据信息通过编码、调制后,发送到音频接口模块;2)将音频接口模块传来的数据进行解调、译码,并通过CPCI总线发送到上位机。

TMS320C6713是Texas Instruments公司出品的DSP芯片,基于0.13μm工艺,是一个高性能的32位浮点DSP产品,核心频率可达225MHz,具有32Bit外部存储器接口、两个McBSP缓冲串口、16Bit的 主 机 接 口 HPI[5];AM29F800B 是 1 个8Mb 容 量 的 FLASH (闪 存 ) 芯 片[6];MT48LC8M32是1个256Mb的SDRAM(同步动态随机存取存储器存储器)芯片[7]。

该模块有2片DSP芯片TMS320C6713,1片完成数据的编码调制,1片完成数据的解调译码,每片DSP芯片分别配置1片FLASH芯片存放DSP的启动信息,配置1片SDRAM芯片存放DSP数据处理过程种的中间数据。

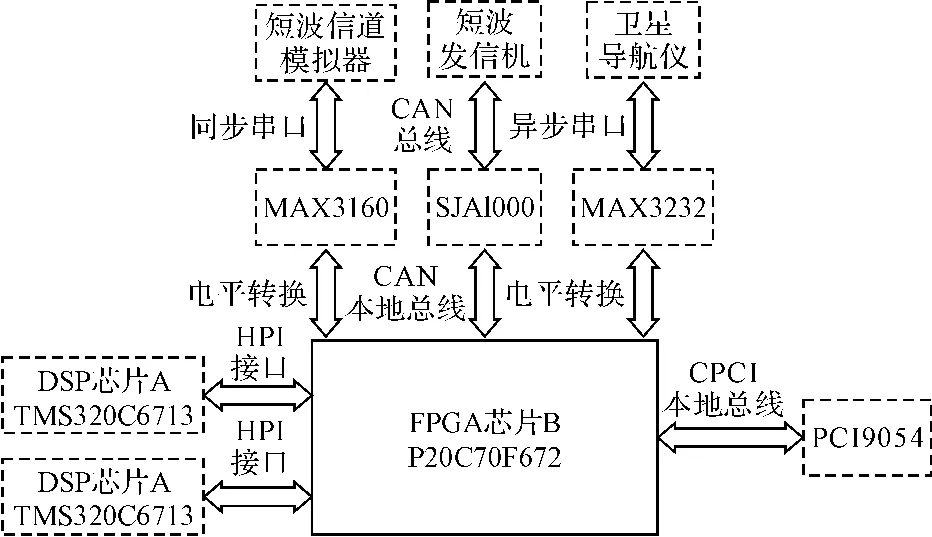

3.5 FPGA模块设计

FPGA模块的主要功能是作为调制解调卡上各个器件间以及外设各个设备间的数据交换的桥梁,包括数据格式的转换、地址译码、外围设备的控制、设备间的中断处理等[8]。

EP2C50F672是Altera公司出品的FPGA芯片,属于Cyclone-II系列,支持多种接口标准,内部频率可达260MHz,可用I/O口为475,可以内部配置594,432bit的双口RAM,还内嵌86个硬件乘法器,可以有效提高数字信号处理的速度[10]。

图3 FPGA模块电路框图

关于各个设备与计算机之间的数据交换流程,FPGA芯片作为两者之间数据交换的中转站,通过分配各个外设映射到PCI9054本地总线的不同地址,计算机访问各个外设的资源,数据的收发通过中断方式进行,FPGA芯片暂存中间数据。FPGA芯片每收完来自计算机本地CPCI总线的数据,根据数据包头的地址区分各个外设,然后向该外设发送该数据;FPGA芯片每收完来自各个外设的数据,通过写PCI9054的中断寄存器(每个外设对应寄存器的不同数值)来通知计算机取走该数据。FPGA模块电路框图如图3所示。

3.6 时钟模块设计

时钟模块功能是给调制解调卡上主要元器件提供所需的时钟,板卡所需时钟频率有:1)50MHz,使用该时钟的元器件为PCI9054;2)10.368MHz,使用该时钟的元器件为TLC320AC02;3)36MHz,使用该时钟的元器件为EP2C70F672;4)25MHz,使用该时钟的元器件为TMS320C6713和MT48LC8M32。

板卡时钟需求主要有2个特点:1)PCI9054所需本地总线时钟50MHz需要频率较为稳定的时钟;2)需要频率种类较多。根据上述特点,采用一个50MHz的有源晶振作为PCI9054的本地总线时钟;采用一个可编程时钟芯片CY22393产生表2中各器件所需时钟频率,由于板卡上有2片TMS320C6713和2片MT48LC8M32需要25MMHz时钟频率,所以采用一片时钟缓冲芯片CY2305作为可编程时钟芯片和各器件中的缓冲[11]。

4 电路电源设计

由于电路上主要元器件均需要电源进行工作,所以电源设计是一个电路板设计成功的关键。本板卡电源部分设计的思路是:分析板卡主要元器件对电压和电流的需求,提出相应解决方案,保证其正常工作。

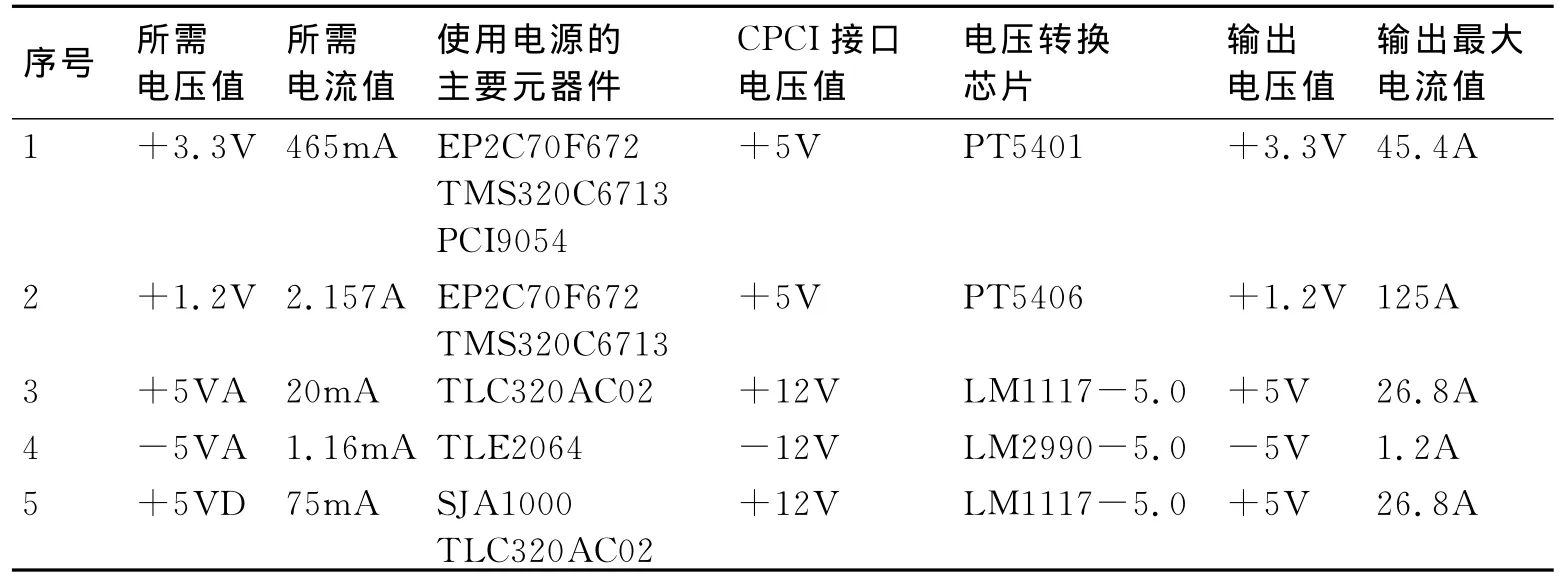

板卡所需电源有:+3.3V、1.2V、+5VA、-5VA、5VD共5种,其中后3种分别为5V(模拟电路用)、-5V(模拟电路用)和5V(数字电路用),通过相关电流计算软件计算和查询元器件使用手册,得出各种电源所需电流;采用CPCI接口的+5V、+12V和-12V电源作为输入,利用不同的电压转换芯片输出所需的电压,同时最大输出电流应大于所需电流。具体实现方法见表2。

表2 板卡所需电源解决方案

由表4可知,经过电压转换芯片对CPCI接口电源电压进行转换,输出电压值符合板卡所需电压值,输出最大电流值大于所需电流值,满足板卡需求。

5 电路电磁兼容性设计

5.1 板卡电源去耦设计

本调制解调板卡主要通过CPCI总线的+12V、+5V和-12V电源进行供电,根据CPCI总线标准规定,每CPCI总线上每10个电源管脚必须有一个0.1μF的瓷片电容,每种电源必须有一个10u的钽电容。故在本板卡电路中,CPCI总线的+5V电源,分配了8个0.1μF电容和2个钽电容;+12V电源,分配了3个0.1μF电容和2个钽电容;以及-12V电源,分配了3个0.1μF电容和2个钽电容。通过对板卡电源去耦设计,提高了电源信号供电稳定性。

5.2 模拟电路和数字电路电磁兼容性设计

本板卡分为模拟电路和数字电路两大功能模块,为防止两个模块的信号互相影响,采取以下措施:

1)对模拟电路和数字电路在PCB电路板布局时进行功能分区,且在模拟电路部分用模拟地信号对整个区域进行敷铜;

2)数字地和模拟地分别接地,并采用“单点接地”的办法,仅在一点处将模拟地和数字地连接起来,防止数字回路对模拟信号造成干扰。

5.3 板卡结构设计

由于本板卡信号线较多,且各个信号对干扰较为敏感,在板卡结构设计时,采用了八层板设计板叠层顺序为:顶层(信号层)-电源层(+3.3V)-信号层-信号层-电源层(模拟地与数字地)-信号层-电源层(除+3.3V外其它电源)-底层(信号层)。

6 结语

本文介绍的短波调制解调板卡已经应用到某短波自适应通信系统中。试验表明,该板卡稳定性好,功能完备,满足预先设计要求。同时,该板卡采用符合CPCI总线标准CompactPCI Specificatian V2.1的接口,通用性强,适用于各类采用该标准的短波通信设备中;基于DSP和FPGA的软件灵活度高,可以根据外部设备的不同调整板卡参数,扩展性好。

[1]PICMG 2.0R2.1(Compact PCI Specification)[R].PICMG,1997:9~10

[2]瞿世尊,陈健.PCI9054在PCI总线高速数据采集中的应用[J].电子技术,2004(2):59~60

[3]赵思阳,陈文艺,卢朝阳.用PCI9054实现实时视频DSP平台[J].无线电工程,2004,34(8):55~56

[4]TLC320Ac02C.TLC320Ac02IData Manual[R].TEXAS INSTRUMENTS,1997:1~2

[5]TMSC6713Data Sheet(Rev.I)[R].TEXAS INSTRUMENTS,2004:1~9

[6]Am29F400BData Sheet[R].Advanced Micro Device,2000:1~2

[7]MT48LC8M32B2Data Sheet[R].Micron Technology,2003:1~3

[8]马亮,向农.基于DSP与PCI总线的电表校验装置的设计[J].仪器仪表用户,2004(4):23

[9]张炜,沈德刚.基于FPGA的PCI总线接口设计与实现[J].计算机与数字工程,2009,37(5)

[10]CycloneⅡ Device Family Data Sheet[R].Altera corporation,2006:1~5

[11]CY22393CY22394CY22395Three-PLL Serial-Programmable FLASH-Programmable Clock Generator[R].Cypress Semiconductor Corporation,2004:1~5