基于DSP和FPGA架构的嵌入式图像处理系统设计

钟 颖 , 张春侠 , 林玉野

(1.北京航天自动控制研究所 北京 100854;2.宇航智能控制技术国家级重点实验室 北京 100854)

随着数字化技术的不断发展和完善,嵌入式数字图像处理技术已广泛应用于工业、军事、生物、医疗、电信等领域,由于图像处理要求运行复杂灵活的图像处理算法和大数据量的数据传输处理,且实际应用中嵌入式系统实时性要求不断提高,要求硬件平台的处理速度快、灵活性强,基于DSP和FPGA架构的数字硬件系统可以把二者的优点结合在一起,已经成为嵌入式图像采集、处理硬件平台的首选方案。

1 嵌入式图像处理系统功能

嵌入式图像处理系统主要负责从前端图像输出部件接收图像数据,经过FPGA逻辑处理后通过FIFO传输至DSP,在DSP中进行算法处理,将处理结果通过串行通信接口发送至主控制单元。为了满足实时性要求,全部图像采集、传输、处理必须在50 ms以内完成。

嵌入式图像处理系统的功能主要包括:

1)通过LVDS接口实时接收图像输出部件传送过来的图像信息;

2)通过RS422串行通信接口实时接收图像输出部件传送过来的其他信息,完成对图像输出部件的配置、指令控制;

3)完成对图像输出部件曝光、时序控制;

4)通过RS422串行通信接口将图像处理结果传送到主控制单元,并接收执行主控制单元控制指令。

5)接收并转发主控制单元与图像输出部件之间的指令、状态信息。

2 系统硬件设计

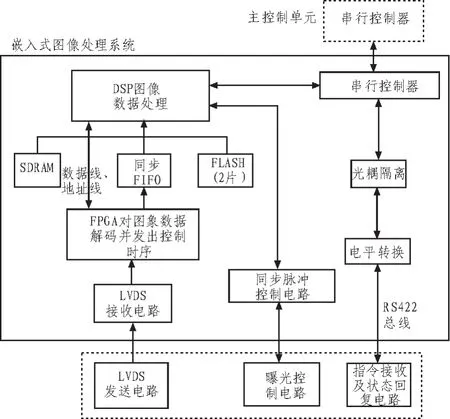

嵌入式图像处理系统构成如图1所示,包括LVDS接收电路、FPGA控制电路、同步FIFO接口电路、DSP数字图像处理及其配套存储器电路、同步脉冲控制电路、串行控制电路等。其中FPGA控制电路主要完成图像信号接收、初步预处理并将其写入同步FIFO中缓存,DSP主要控制图像采集输出部件正常工作、接收FIFO传送的图像数据、实现较为复杂的图像处理算法等。

系统硬件设计采用模块化设计思想,保证系统工作可靠,满足实时性要求。

2.1 DSP数字图像处理电路

DSP选用TI公司的TMS320C6416芯片,其为定点数值处理器,内部采用两个高速缓存器,即16 kbyte的一级数据cache,16 kbyte的一级程序cache和可映射到统一存储空间的1 024 kbyte的二级存储器;主频最高可以达到600 MHz,具有EDMA、QDMA数据传输方式,可以大大缩短数据搬移时间;对外接口包括两个外部存储器接口(EMIFA和EMIFB)、主机接口(HPI)、多通道缓冲串口(Mcbsp)等,接口能力强,具有与大部分存储器的无缝接口,使用灵活、易于扩展。

图1 系统设计框图Fig.1 System design schematic

TMS320C6416DSP内核采用超长指令字体系结构,有8个功能单元、64个32 bit通用寄存器。内核工作电压1.4 V,外围工作电压3.3 V,工作于最高主频600 MHz时功耗仅为1.6 W,功耗较低。

如图1所示主机内存分配如下:1片扩展SDRAM芯片,存储容量 64 Mbyte;2片 FLASH芯片,监控 FLASH为1 Mbyte,主要用于存储程序;数据记录FLASH为4 Mbyte,主要用于存储基准图数据。

2.2 LVDS接口电路

LVDS接口用于实时接收图像采集输出部件传输过来的图像信息,接收芯片与图像采集输出部件的发送芯片保持匹配,采用NS公司的DS90CR216芯片。图像采集输出部件将图像数据通过4路LVDS差分信号传输到嵌入式图像处理系统,通过LVDS接收芯片解码,分别输出10位图像数据、行同步脉冲、场同步脉冲和数据时钟,数据图像如图2所示。

图2 LVDS传输信息时序图Fig.2 LVDS transmit information schedule diagram

LVDS传输信息时序说明如下:

1)每个场同步脉冲(下升沿)到来,标志一帧图像到来;

2)场脉冲周期内,在场脉冲低电平期间,每个行脉冲(上升沿)到来,标志一行图像数据到来,每帧图像有512行图像,从而有512个行脉冲;

3)每个行脉冲周期内,在行脉冲低电平期间,每个像素时钟上升沿到来,标志一个像素数据到来,每个像素数据有10 bit,并行传输;

4)接收端需要在每个像素时钟上升沿到来后将10位图像数据锁存。

2.3FPGA电路

根据系统时序控制和计数等功能需要逻辑门的大小,FPGA芯片选用ACTEL公司的APA600芯片,此芯片内部自带ROM,上电就可以自主运行,不需从外部ROM引导,可靠性高,已经成为航天、医疗等可靠性要求高场合的首选产品。

FPGA实现的功能主要包括:

1)接收LVDS传输数据并将其写入FIFO 对LVDS接收芯片接收的信号按照图2所示的时序关系进行处理,判断场、行同步信号是否有效,在场同步信号有效、同时行同步信号有效的情况下按照CCD时钟将512×512个有效数据写入FIFO。

2)总线控制 对EMIFB CE2空间进行地址译码,分配给两个串口作为片选。

3)复位信号处理 对上电复位和外部主控制单元发送的复位信号进行逻辑处理,控制电路板上的各个芯片复位信号有效。

2.4 RS422接口电路

一路RS422接口电路用于信息处理系统向图像采集输出部件传送控制指令和配置信息;同时图像采集输出部件向信息处理系统回传状态信息;另一路RS422接口电路用于信息处理系统向主控制单元传送图像处理结果,以及主控制单元向信息处理系统发送控制指令。

串行通信控制器选用TI公司的串行控制芯片TL16C752B芯片,内部集成两个独立的串口控制单元,通信协议(数据位、波特率等)可以通过软件灵活配置,通信速率最快可以达到2 Mbps,外部接口和时序控制都比较简单。两个串口控制单元的中断请求管脚分别对应DSP的两个外部中断输入管脚,软件管理简单,提高了可靠性,技术成熟。

2.5 同步脉冲控制电路

同步脉冲控制电路主要用于信息处理系统向图像采集输出部件发送外触发曝光信号。

图像采集输出部件有两种工作方式,一种是外同步方式,即图像处理板通过IO口向图像采集输出部件发送外触发曝光信号启动图像采集输出部件曝光;另一种方式是内同步方式,即图像采集输出部件在曝光中间时刻将曝光同步信号发送到图像处理板,通知图像板曝光开始,图像处理板需实时响应该信号从而获知曝光时刻。

本设计采用外同步方式,主要利用DSP的GPIO口产生同步脉冲信号,外触发信号的电路形式见图3所示。

2.6 FIFO接口电路

图3 外同步脉冲输入控制曝光时间电路原理图Fig.3 External synchronization pulse control exposal time principle diagram

FIFO接口电路是介于FPGA和DSP之间的数据缓冲单元,也是确保可以准确读取图像数据的关键环节,电路原理图参见图4所示。FIFO接口设计的关键是确定好几个关键信号的处理,写时钟、写使能、读时钟和读使能,写时钟、写使能由FPGA控制,写时钟为前端CCD时钟信号,当场、行同步信号同时有效的情况下,写使能信号有效,将数据写入FIFO。设计中采用IDT公司的IDT72V2105芯片,该芯片容量为262 144×18 bit,可以满足设计要求。

图4 FIFO接口电路原理图Fig.4 FIFO interface circuit diagram

3FPGA程序处理

FPGA程序处理的主要任务之一是按照图2中LVDS传输信息时序图的要求,准确接收LVDS传输的图像数据,并将其按照节拍写入FIFO中缓存。程序设计的要点是准确判断场同步信号是否到来,场同步信号到来后判断行同步信号是否到来,在场同步信号、行同步信号都有效的情况下如何控制将数据写入同步FIFO。

设计难点及解决办法主要包括:

1)正确判断行、场信号到来并有效读取数据

为了准确判断场同步信号ccd_vd、行同步信号ccd_hd是否有效(下降沿到来)并且在ccd_hd有效后的第一个时钟上升沿读取到数据,设计中采用ccd_clk时钟频率3倍以上的高频时钟 clkin对 ccd_vd、ccd_hd进行采样,fif0_wen为FIFO写使能控制信号,fifodata为写入FIFO后的数据,仿真后的波形图参见图5所示,满足时序要求。

图5 有效读取起始数据仿真波形图Fig.5 Effectively read initiative data emulation wave diagram

2)有效读取512行

为了准确获得512×512个有效数据,在ccd_vd有效的前提条件下,需要对ccd_hd进行计数,如果超过512行就认为数据无效,此时关闭fif0_wen,cnt2为行计数值,仿真后的波形图参见图6所示,满足时序要求。

图6 有效读取512行仿真波形图Fig.6 Effectively read 512 rows emulation wave diagram

3)有效读取每行的512个数据

为了准确获得512×512个有效数据,在ccd_hd有效的前提条件下,需要对ccd_clk进行计数,如果超过512个时钟信号就认为数据无效,此时关闭fif0_wen,cnt1为有效数据计数值,仿真后的波形图参见图7所示,满足时序要求。

图7 有效读取每行512个数据仿真波形图Fig.7 Effectively read 512 data in every row emulation wave diagram

4 软件设计

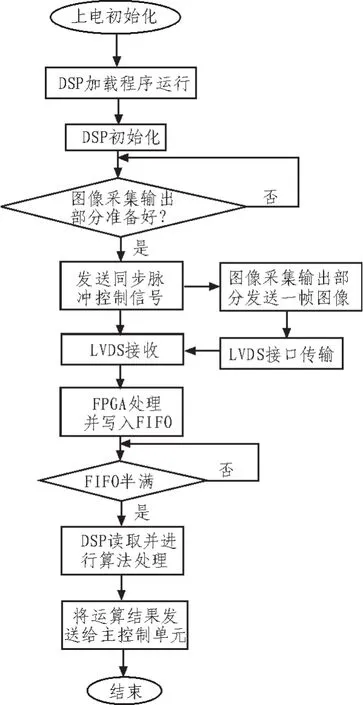

系统运行的过程如图8所示:系统加电以后,上电复位电路会产生200 ms的低电平复位脉冲,在复位的这段时间内,位于外部CE1空间的FLASH中的代码首先通过EDMA被搬入内存中。传输完成后,CPU退出复位状态,开始执行内存中的指令。

首先对嵌入式图像处理系统进行初始化,工作正常后通过串行控制器与前端图像采集输出部件进行通信,确认图像采集输出部件工作正常后发出相关成像指令,指令执行正常后由图像处理系统发出同步脉冲控制信号,图像采集输出部件接收到同步脉冲后输出一帧图像,经过LVDS转换输出后,在FPGA中进行初步判断处理,由FPGA按照时间节拍将图像数据写入同步FIFO中缓存,当写入FIFO的数据达到FIFO存储容量的一半时,FIFO会通过外部中断4向CPU提出中断申请,CPU响应中断并按照EDMA方式从FIFO中读取数据,随后在内存中进行相关算法的处理。算法处理结束以后,CPU把运算结果发送给主控制单元,至此系统运行结束。

在该嵌入式图像处理系统上运行图像复原算法后处理结果如图9所示,使用的图像像素为 512×512,图像灰度值为10 bit,图 9(a)为原始图像,图 9(b)为算法处理后的输出结果。

在满足系统功能性要求的同时,对图像采集、传输、处理的时间进行了统计,其中前端图像采集输出部件接收到外部触发脉冲后10 ms输出一帧图像,经过FPGA和FIFO缓存及被DSP读取大致需要16 ms,图像处理算法需要20 ms,整个图像采集、传输、处理过程需要46 ms,满足系统实时性要求。

图8 软件运行流程图Fig.8 Flow chart of software

图9 系统处理实验结果Fig.9 System process experimentation result

5 结束语

基于DSP和FPGA架构的嵌入式图像处理系统针对可见光图像数据量大,数据复杂的特点,充分利用了DSP计算庞大数据的高效性和FPGA精于并行处理的优点,系统具有集成度高、存储量大、处理速度快和方便传输等特点。另外系统也有很好的通用性,不仅能够用于目标识别,还可实现压缩、分类等其他信息处理,具有广泛的应用前景。

[1]李方慧,王飞,何佩坤.TMS320C6000系列DSPs原理与应用[M].2版.北京:电子工业出版社,2003.

[2]张晔,邵涛,严萌.基于DSP和FPGA的高光谱图像处理系统设计[J].光电技术应用,2010,25(1):56-59.ZHANG Ye,SHAO Tao,YAN Meng.Design of hyperspectral image processing system based on DSP&FPGA[J].Electrooptic Technology Application,2010,25(1):56-59.

[3]高春甫,杨前进,冯礼萍,等.基于FPGA+DSP的CCD实时图像采集处理系统[J].山西大学学报:自然科学版,2007,30(1):36-39.GAO Chun-pu,YANG Qian-jin,FENG Li-ping,et al.A real time digital image processing system for CCD based on FPGA and DSP[J].Journal of Shanxi University:Nat.Sci.Ed.,2007,30(1):36-39.

[4]干戈.基于DSP+FPGA的双通道实时图像处理系统设计[J].舰船电子工程,2008,28(7):75-77.GAN Ge.Design and implementation of 2-channel digital image processing system based on DSP+FPGA Architecture[J].Ship Electronic,2008,28(7):75-77.

[5]郭志强,刘毅.基于DSP并行处理的图像融合系统设计[J].武汉理工大学学报:信息管理工程版,2006,28(11):107-109.GUO Zhi-qiang,LIU Yi.Design of an image fusion syetem based on DSP parallel processing[J].Journal of Wut:Information&Management Engineering,2006,28(11):107-109.

[6]潘基明,张少兵.基于DSP视频图像采集处理系统设计[J].电子测试,2008(8):74-78.PAN Ji-ming,ZHANG Shao-bing.DSP-based video image acquisition and processing system design[J].Electronic Test,2008(8):74-78.