一种基于ARM的远程监控系统的设计与实现

唐文俊 李维波 贺洪 饶金

(海军工程大学舰船综合电力技术国防科技重点实验室,武汉 430033)

1 引言

随着以太网朝着高速方向发展并借助交换技术、全双工工作方式的融入以及嵌入式技术的步发展,极大地推动了以太网技术在工业控制领域中的广泛应用。由于嵌入式系统具有体积小、功耗低、可靠性高以及面向行业应用的突出特点,大量应用于国防军事、消费电子、网络通信、工业控制等多个领域。ARM和 FPGA是嵌入式领域应用非常广泛的微处理器,ARM在顺序执行和事务处理方面功能强大,FPGA的 I/O口丰富、处理数据的速度高能力强,将它们有机结合起来构建嵌入式采集系统,就兼具各自的优点[1]。

本文阐述一种基于ARM和FPGA的远程监控系统,分别从硬件选型和软件编程两方面进行论述,并借助实验验证该系统的有效性和合理性。

2 硬件电路的设计

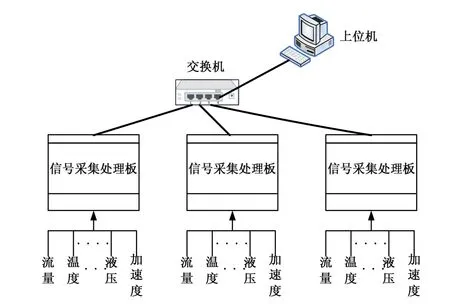

图1表示基于ARM和FPGA的监控系统的总体框图,它主要由信号采集处理板、交换机和上位机等几个重要部分组成。

图1 监控网络结构图

由于信号采集处理板是整个监控系统的核心,起到了承上启下的关键作用,一方面它将完成底层信号的获取和预处理,另一方面它将对这些信号进行后续处理并上传给上位机,本文将重点介绍这部分内容。

2.1 信号采集处理板

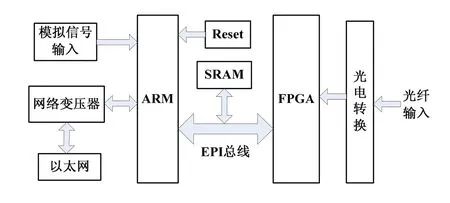

信号采集处理板的硬件架构如2所示,它由ARM 和 FPGA两个微控制器构建而成,其中ARM作为整个处理板的主控单元,完成读取存储器数据、A/D采样、并与FPGA和上位机之间的通信等功能;FPGA则主要对来自光电转换获得的数字量进行数字滤波、采集和存储等重要操作。

图2 信号采集处理板的硬件架构图

信号采集处理板的 ARM 选型为 TI公司的LM3S9B92。它是基于 ARM® Cortex-M3™技术的一款32位高性能的微控制器,在80 MHz的时钟频率时可以达到100 DMIPS(每秒百万条指令)的处理能力,相对于当前的 8位和16位微处理器(MCU)的水平,具有突出的优势,同时具有Cortex-M3和Thumb-2指令集。其中Thumb-2技术可以使16位和32位的指令并存,带来了代码密度和性能的最佳平衡,Thumb-2比纯32位代码占用少26%,同时使得性能提升25%,有效降低系统成本。

另外,LM3S9B92片内资源非常丰富,它集成了高速外部并行总线接口(EPI接口),支持8位/16 位/32 位专用并行总线,便于连接片外设备或存储器,并支持直接存储器访问控制器(DMA)、时钟控制、片外 FIFO 缓冲等功能,可实现高效的数据传输;它集成了10/100M以太网的MAC和PHY模块,只需要外接一个网络变压器芯片,就能实现以太网功能(目前一般的微处理器还不具备该功能),如图2所示。与此同时支持 IEEE1588精确时间协议,为每个单独的数据包提供高精度时间戳,该以太网控制器还支持DMA高效数据传输,能够有效提高通信速率。

第三,LM3S9B92 微控制器内置了一个DMA,该DMA控制器所提供的工作方式能够降低Cortex-M3处理器参与数据传输任务,从而更加高效地使用内核以及总线带宽,它还能够自动执行存储器与外设之间的数据传输,片上每个支持DMA 功能的外设都有专用的DMA 通道,通过合理的编程配置,当外设需要时能够自动在外设和存储器之间传输数据;LM3S9B92 微控制器还集成了两个10位的A/D模块,支持16个I/O接口,并且内置温度传感器,A/D模块包含4个可编程的序列发生器,无需控制器干预即可自动完成多个模拟量的采样,每个采样序列发生器都可灵活配置其模拟量、触发事件、中断产生和序列发生器的优先级[2]。

FPGA微控制器采用 Altera公司的 Cyclone系列的EP1C3T144I7N,它有接近3000个逻辑单元、13个M4k RAM模块,共有104个用户可用I/O接口,支持66MHz、32位PCI接口,它有两个PLL模块能够提供时钟倍频和移相功能,它同时也支持外部的存储器接口,可以外部扩展SDRAM、SRAM、FLASH等存储器,因此它是一款性价比较高的处理芯片[3]。

2.2 ARM、FPGA和SRAM之间的接口

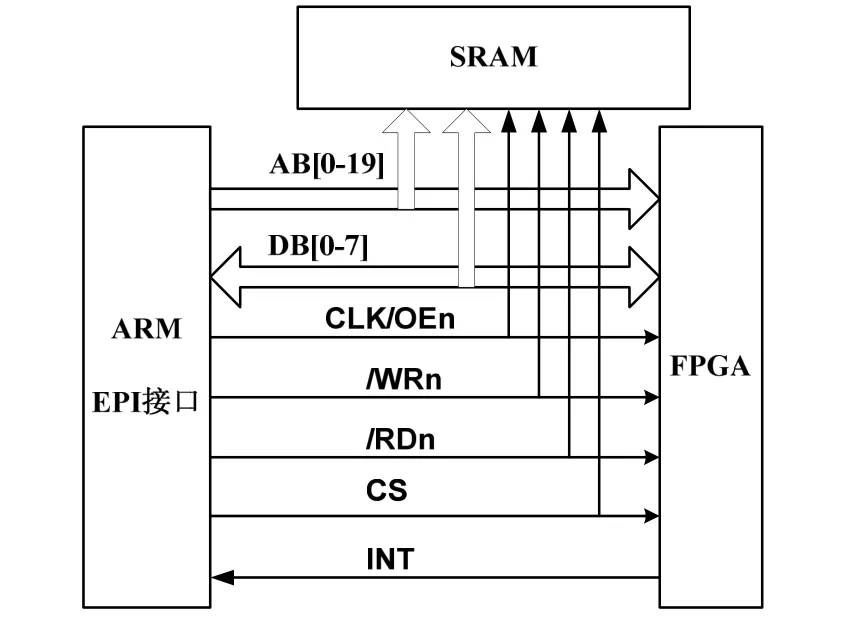

ARM作为主控制器,控制 FPGA完成信号的采集和存储等功能,它们之间的通信效率会直接影响控制器的性能,本文特别采用总线形式,并在总线上挂一个SRAM缓存数据,便于提高数据传输效率,它们之间的接口关系如图3所示。

分析图 3得知,该总线包括三种总线,即ARM与FPGA的总线,ARM与SRAM的总线以及FPGA与SRAM的总线。图3中AB[0-19]表示20位地址总线;DB[0-7]表示 8位数据总线;CLK/OEn表示时钟或使能信号,当操作FPGA时,CLK/OEn配置为时钟信号,当操作 SRAM时,CLK/OEn配置为使能信号,作使能信号时是低电平有效;WRn为写信号且低电平有效;RDn为读信号且低电平有效;CS为片选信号且高电平有效;INT为FPGA向ARM发出的中断请求信号,以应对特殊情况时请求ARM进行干预处理。

图3 ARM、FPGA和SRAM的接口关系

2.3 FPGA的编程配置

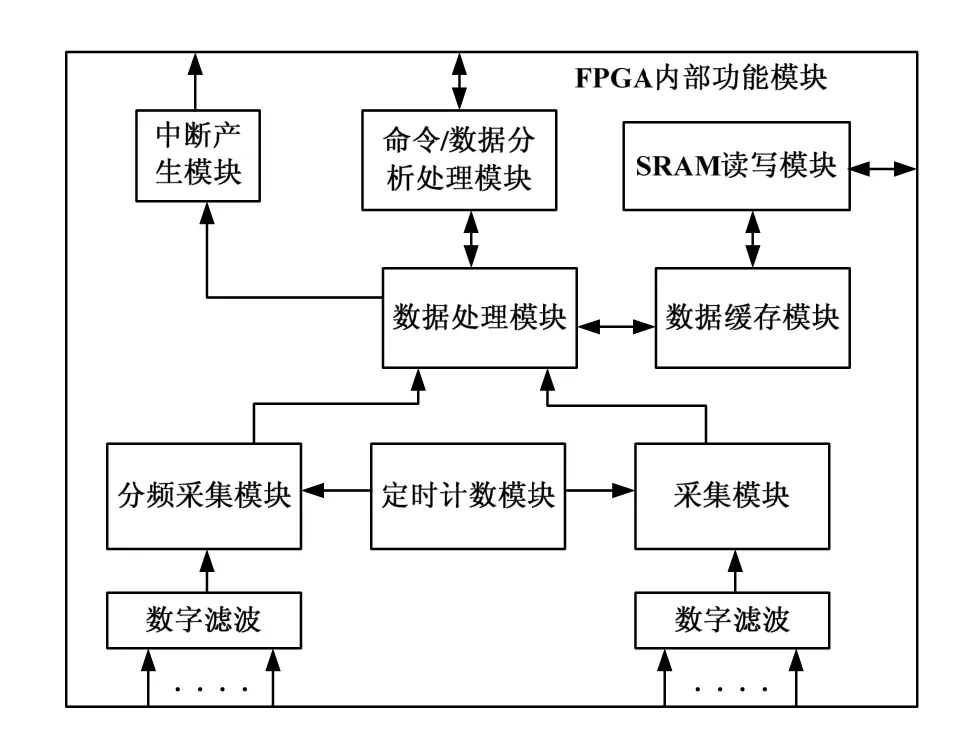

由于该监控系统需要处理模拟量和数字量,而数字信号的频率又各不相同,为了与这种特点的数字量相适应,需要采用灵活的可编程方法来配置FPGA的接口和相应的处理模块,其配置功能如图4所示,它包括以下几个重要模块:

1) 数字滤波模块:对输入量进行滤波处理,本文采用了 FIR滤波方式;2)高频数字信号采集模块,完成高频数字信号的分频和采集功能;3)低频信号采集模块,用于采集频率不高的数字信号;4)定时计数模块,用于按照要求的频率采集数据;5)数据处理模块,用于完成所有输入数据的处理和控制数据块的读/写前的操作;6)数据缓存模块,用于对数据块的存储操作;7)SRAM的读/写模块,完成数据的读入和写入 SRAM 功能;8)中断产生模块用于完成 FPGA的中断申请;9)命令/数据分析处理模块,完成 ARM 的控制响应和与ARM的通信操作。

3 系统软件设计与实现

软件设计主要包括ARM实现TCP/IP协议并与上位机通信,控制FPGA实现采集存储等工作。FPGA程序设计采用Verilog语言编写,在Quartus II 8.1环境下实现,并在ModelSim-Altera 6.3环境下进行了功能仿真和时序仿真。ARM程序设计在IAR6.1环境下实现,主要包括以下三部分:一是TCP/IP协议栈的实现;二是ARM完成模拟信号的采集;三是与FPGA和SRAM的通信。本文主要介绍ARM程序的实现方法。

图4 FPGA的功能模块的配置

3.1 TCP/IP协议栈的实现

TCP/IP协议栈实际上是一个协议族,主要由负责对不同网络进行互联的 IP协议和检测网络传输中差错的传输控制TCP协议组成,但是它的代码体积庞大、CPU耗时多给处理器带来了一定的困难,随着嵌入式以太网技术的快速发展,国外推出了不少轻量级的TCP/IP协议,如LwIP、uIP等,针对工程的实际需要,本文选择了LwIP协议。

LwIP是瑞士计算机科学院(Swedish Institute of Computer Science)的 Adam 、Dunkels等开发的一套用于嵌入式系统的开放源代码 TCP/IP协议栈。LwIP的含义是Light Weight(轻型)IP协议。LwIP可以移植到操作系统上,也可以在无操作系统的情况下独立运行。LwIP TCP/IP实现的重点是在保持 TCP协议主要功能的基础上减少对RAM的占用,一般它只需要几十kB的RAM和40kB左右的ROM就可以运行,这使LwIP协议栈非常适合嵌入式系统中使用。LwIP的主要特性有:

(1)支持多网络接口下的IP转发。

(2)支持网际间控制报文协议ICMP(Internet Control Messages Protocol)协议。

(3)包括实验性扩展的UDP协议(用户数据报协议)。

(4)包括阻塞控制、RTT估算和快速恢复和快速转发的TCP协议(传输控制协议)。

(5)提供专门的内部回调接口(Raw API),用于提高应用程序性能。

(6)多线程情况下,具有可选择的 Berkeley接口API,支持动态主机配置协议(DHCP)和动态分配IP地址[4-6]。

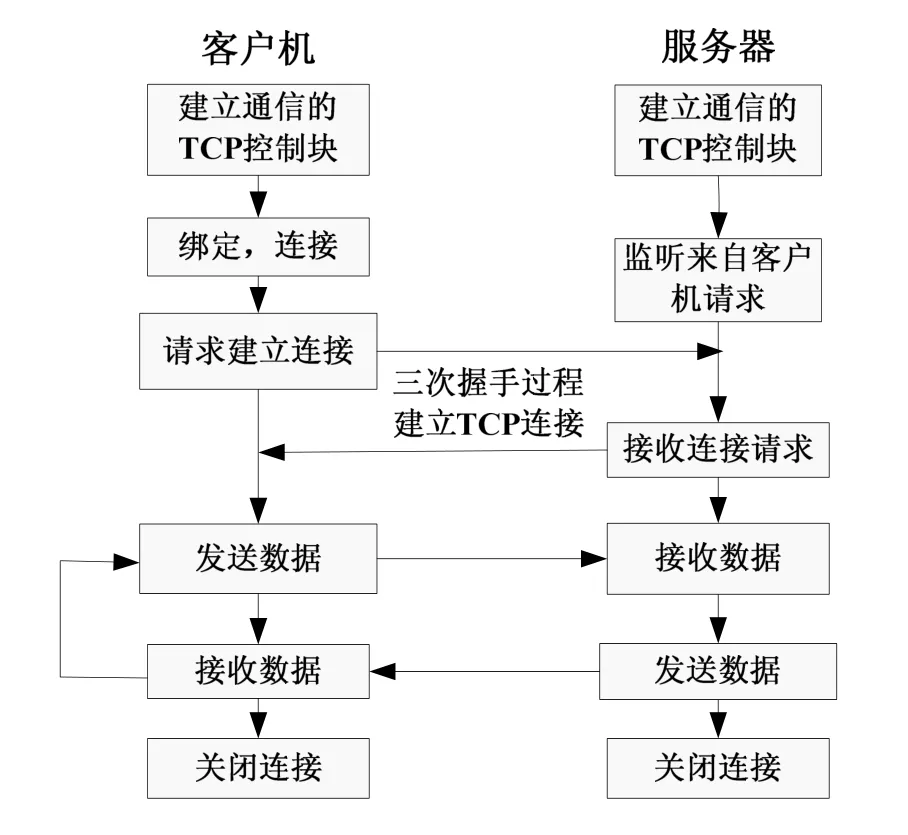

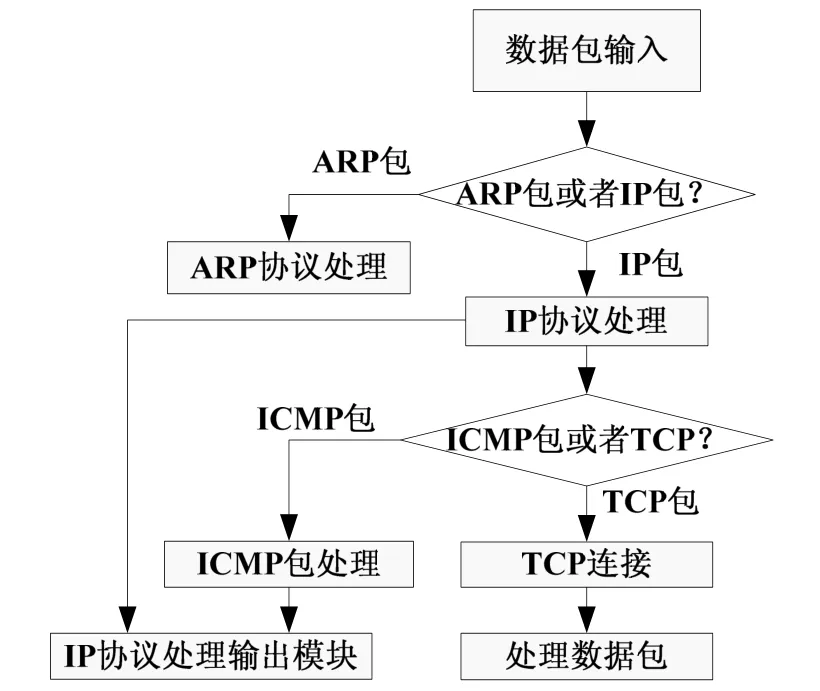

由于系统传输的数据比较大,对速度也有一定的要求,对数据的准确性和稳定性要求很高,所以采用无操作系统的LwIP的TCP协议建立高效可靠的链接来保证数据传输的质量,上位机与信号采集处理板采用客户机/服务器的模式进行通信。软件设计的主要工作是LwIP的移植和TCP协议处理后的数据处理,其流程如图5所示,它为面向连接的客户机/服务器通信流程图,图6表示处理数据包的流程图[7-9]。

图5 面向连接的客户机/服务器通信流程

图6 数据包的处理流程图

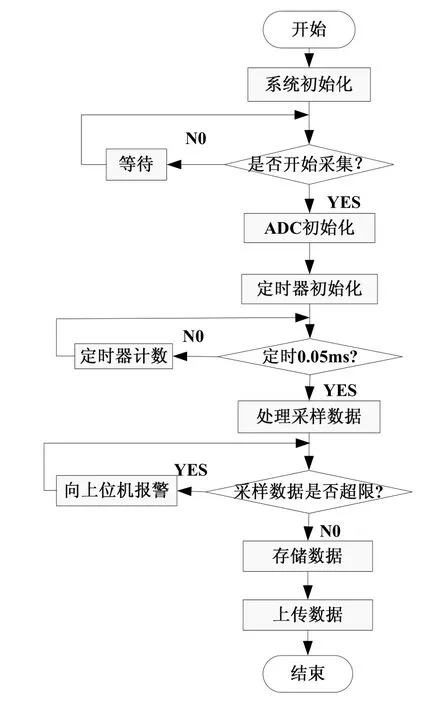

3.2 ARM完成模拟信号的采集

针对温度、电压等模拟信号,采用 ARM自带的16通道ADC进行采集,本文选用的ARM能够达到10位的转换精度和1M次每秒的采集速率,完全能够满足采集要求,而且支持硬件过采样技术,能够对采集结果进行多达64个采样取平均值,能很好的提高采样的精度。图7表示模拟量采集的流程图。

图7 模拟量采集流程图

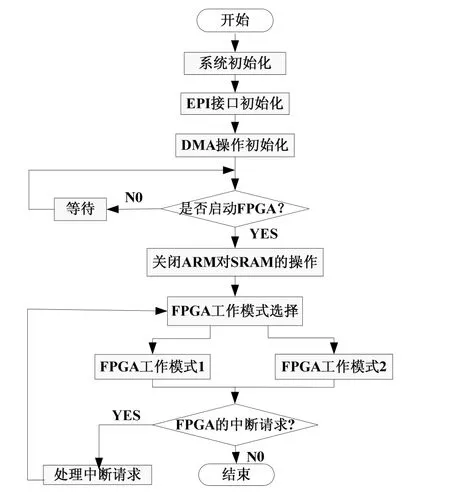

图8 ARM与FPGA的通信流程图

2.3 与FPGA和SRAM的通信

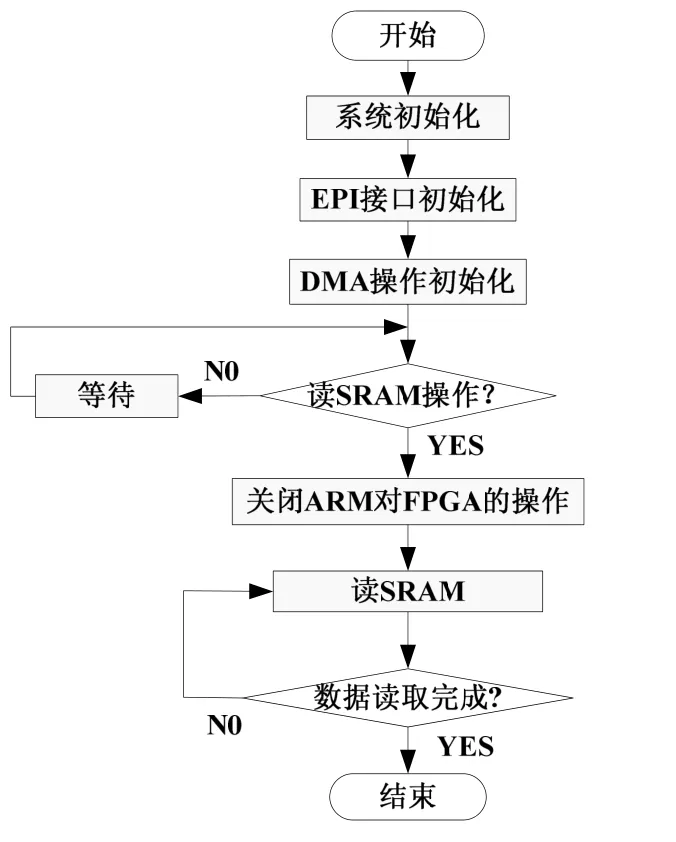

FPGA在硬件处理方面具有独特的优势,并且硬件实现是并行处理模式,配置50 MHz的时钟能满足很高的性能要求和时序要求,本文采用ARM控制 FPGA采集的处理方式,并且采用总线形式,同时数据存储使用外部的SRAM作为存储,减少了FPGA的负荷用时拓展了存储空间,很好的提高了监控的数量和质量。图8表示ARM与FPGA的通信流程,图9表示FPGA对SRAM进行读操作的基本步骤。

图9 ARM对SRAM进行读操作

4 测试结果

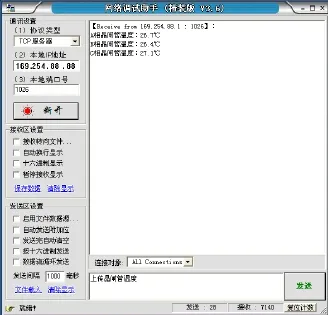

按照上述硬件和软件的设计,通过软件调试成功后,并对软硬件进行实验验证,图10表示本采集系统的实物图,中间部分为信号采集处理板,它采集晶闸管的导电极温度,并通过以太网的方式发送给上位机,上位机采用网络调试助手,通过设置协议类型、IP地址和端口号进行网络连接,图11表示实验测试结果[10]。

图10 采集系统实物图

5 结论

对基于ARM+FPGA的远程监测系统,从硬件和软件两部分进行了研究,由于该系统采用了无操作系统的精简 TCP/IP协议,能够实现远程监控,且该系统具有成本低、占用资源少、功能完善、操作方便、易于扩展等特点,可用于现场远距离测试多种数据量,并易于通过网络进行快速级联,具有较强的推广价值。

图11 上位机测试结果图

[1]陈积明, 王智, 孙优贤. 工业以太网的研究现状及展望 [J]. 化工自动化及仪表, 2001, 2(28): 7-10.

[2]Stellaris LM3S9B92 microcontroller datasheet. texas instruments incorporated.

[3]Cyclone device handbook, Volume 1. Altera Corporation.

[4]邱维宝, 傅星, 邬泳. 基于以太网的信号发生与采集控制系统的研究[J]. 电子技术应用, 2006, 11:77-79.

[5]Adam Dunkels. Design and Implementation of the LwIP TCP/IP Stack [M]. Swiss: Swedish Institute of Computer Science, 2001

[6]张海波, 胡大可. 低成本高速率传感器网络的设计实现 [J]. 传感技术学报, 2010, 23(5): 732-738.

[7]范建华.TCP/IP详解卷 1: 协议 [M]. 北京: 机械工业出版社, 2000.

[8]Douglas E. Comer. 用 TCP/IP进行国际互联 [M].第一卷:原理协议与结构(第 5版), 北京: 电子工业出版社, 2007.

[9]Douglas E. Comer, David L. Stevents.用 TCP/IP 进行国际互联[M]. 第二卷:设计实现与内核:第三版.北京:电子工业出版社, 2001.

[10]李维波,饶金,贺洪. 晶闸管脉冲功率开关保护参数优化计算及其影响特性[J]. 高电压技术, 2009,35(12): 3099-30105.

- 船电技术的其它文章

- 船舶通信导航设备配套综合设计分析