基于Xilinx MicroBlaze多核嵌入式系统的设计

何宾,王瑜

(北京化工大学 信息科学与技术学院,北京 100029)

随着嵌入式处理需求的快速增长,单处理器系统复杂度太高且计算能力不足的缺点不能满足需求,嵌入式系统架构开始转向多处理器的协同工作,这样针对同一系统的多任务需求,协同工作的处理器可以充分完成各自管辖的不同功能应用。近年来,FPGA以其高逻辑集成度和内嵌的高性能硬件模块的优势,使得功能强大的芯片多处理(CMP)解决方案成为现实,如今关键问题是如何高效地将各种IP核互联在一起,构成复杂的系统,实现多核处理器的设计。

本文提出了将3个可编程的32位微处理器软核MicroBlaze内嵌到FPGA芯片上,实现了一个运行在FPGA上的基于多处理器软核的可编程片上系统,并对采用PLB总线与FSL总线连接处理器,实现核间通信进行了比较。一个FPGA芯片内部可以使用主从两个或多个MicroBlaze处理器,而FPGA最大的特点就是能够缩短产品开发的周期,它的可编程配置特性可以将系统开发的风险降到最低。而Xilinx公司的MicroBlaze软核处理器的优点在于,不像ARM是由固定的硬芯片来实现,用户可以根据实际系统的需求添加必要的外设来实现基于MicroBlaze的嵌入式可编程片上系统,从而提高了设计的灵活性。

1 系统总体结构设计

系统整体架构如图1所示。本系统是基于MicroBlaze的三核系统,采用嵌入3个32位处理器软核MicroBlaze的SOPC是由Xilinx公司提供的Spartan-3E芯片[1]。

图1 三核处理器互连架构Fig.1 Interconnect architecture of three processor

在本系统中,2个MicroBlaze软核协同处理工作,核间采用PLBv46总线互连,并利用系统自带的XPS_Mailbox核实现核间的通信,第2个核与第3个核之间采用FSL总线实现点对点的通信。在核不多的情况下,采用共享内存结构可以有效地减少核间的通信量,避免数据一致性的问题。本系统中,数据传送到第1个核,第1个核与第2个核之间进行通信,第2个核再将数据发送给第3个核,并通过PC机超级终端接收UART的输出,得到输出信息,经过分析和比较,可以对系统进行调试和最后结果的验证。

1.1 Spartan-3E开发板

Spartan-3E是Xilinx公司在Spartan-3成功的基础上改进的产品,提供了比Spartan-3更多的I/O端口和更低的单位成本,是Xilinx公司性价比最高的FPGA芯片。其应用广泛:支持32位RISC处理器;支持DDR接口的应用;内嵌Xilinx的MicroBlaze软核,可用于嵌入式系统的开发;支持基于Ethernet网络的应用。本系统采用的FPGA芯片是XC3S500E-4FG320。

2 多MicroBlaze软处理器核的系统设计

2.1 EDK开发平台介绍及其开发流程

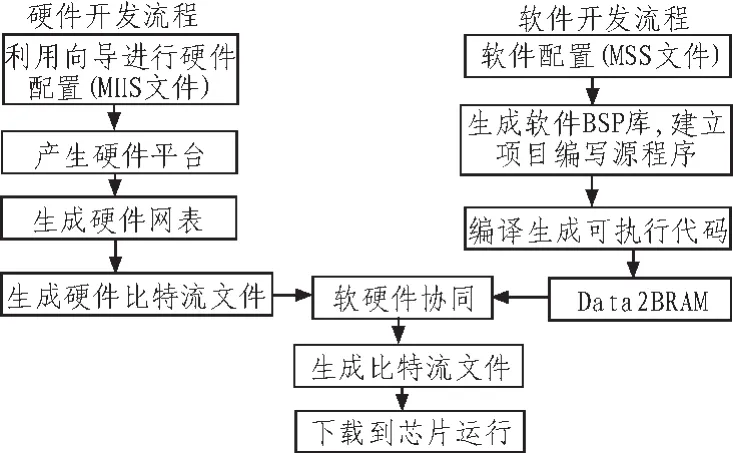

一般而言,由于嵌入式系统涉及了软件和硬件的开发以及两者的综合设计,因此其开发是较为复杂的。Xilinx为了简化基于FPGA的嵌入式开发流程,提供了功能强大、操作简单的工具ISE和EDK。

EDK(Embedded Development Kit)是XILINX公司针对FPGA内部32位嵌入式处理器开发而推出的工具套件。EDK的工具包中集成了硬件平台产生器(platgen)、软件平台产生器(libgen)、仿真模型生成器(simgen)、软件编译器(GNU)和软件调试(GDB)等工具,同时配有丰富的可重用IP核,利用其集成开发环境XPS(Xilinx Platform Studio)可以方便、快速地完成嵌入式系统开发的整个流程。该开发流程主要分为硬件开发流程和软件开发流程,整个流程如图2所示。其中,嵌入式处理器硬件系统的构建由微处理器硬件规范(MHS)文件定义,用于描述硬件系统结构,定义处理器类型、总线接口、外设接口、中断处理和地址空间;软件系统结构由微处理器软件规范(MSS)文件定义,用于装载软件库、驱动程序和文件系统。Data2BRAM 的作用是把软件代码文件 (*.Elf)、FPGA位流文件(*.bit)和块存储器(BRAM)初始化数据文件(*.bmm)转换成新的 FPGA 位流文件(*.bit)和存储器数据文件(*.mem)[2]。

图2 EDK开发流程Fig.2 Development process of EDK

2.2 系统硬件平台的搭建与设计

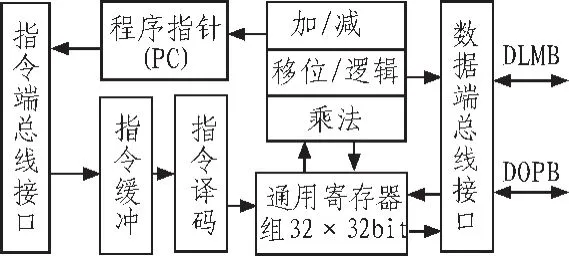

2.2.1 MicroBlaze软核

MicroBlaze处理器是Xilinx公司针对嵌入式处理器开发应用推出的一种32位嵌入式处理器内核,采用RISC架构和哈佛结构的32位指令和数据总线,可以全速执行存储在片上存储器和外部存储器中的程序,并访问其中的数据。简单但灵活性强,与其他外设IP核及用户IP核一起,可以完成片上可编程系统芯片(SOPC)的设计。MicroBlaze处理器的内部结构如图3所示[3]。

图3 MicroBlaze内部结构框图Fig.3 Internal block diagram of MicroBlaze

2.2.2 硬件平台搭建步骤及其设置

利用Xilinx公司提供的嵌入式开发工具EDK中的基本系统创建器(Base System Builder,BSB)向导来快速创建一个工程。通过进入XPS图形用户界面,在系统的组件面板中,通过Bus interface子窗口建立硬件单元与总线的连接,在硬件单元上单击鼠标右键,可配置其参数、阅读相应的数据手册以及查看底层代码。通过Ports子窗口配置端口参数,包括顶层模块和各个子模块的端口,并可对其重命名。单击相应信号行Net列的下拉框,可选择连接的网表名。通过Address子窗口设置硬件单元的绝对地址和大小,用户还可设置指令缓存(ICache)和数据缓存(DCache)的位置。

2.2.3 PLBv46总线

通过Xilinx公司128bit宽度的PLB总线可将多个PLB主设备和PLB从设备连接到整个PLB系统中。PLB总线结构包括总线控制单元、看门狗计时器、读/写数据通路以及独立的地址空间,此外,还带有一个可选的DCR从接口来访问总线错误状态寄存器。PLB总线的主要特点包括以下几点:

1)支持任意数目的PLB主设备。

2)可支持128 bit、64 bit及32 bit位宽的从设备和主设备。3)仲裁时间小于3个周期。

4)PLB地址流水线技术,支持共享总线模式或端到端的配置模式。

5)自带PLB看门狗计时器。

6)效率远高于OPB总线,特别是在大吞吐量应用场合。

此外,PLB总线支持单拍读写8位、16位、32位数据传输和低延时的PLB点到点拓扑结构。PLB总线桥的功能就是将2个独立的PLB总线连接起来,实现外设资源的共享[4]。

2.2.4 FSL总线

FSL_V20快速单链接(FSL)总线是一个基于FIFO的单向点对点通信总线,可用来连接FPGA上的任意两个带有FSL总线接口的设计元素并提供两者间的快速通信信道。Xilinx MicroBlaze处理器最多可支持8个FSL主设备接口和8个FSL从设备接口。这些接口被用于处理器的寄存器堆和FPGA片内的硬件之间的数据传输,单个数据传输操作消耗的CPU时间不超过2个时钟周期[4]。

FSL总线具备以下主要特征:

1)实现了单向的、点对点的、基于FIFO的通信;

2)提供了不共享的、无需仲裁的通信机制,可以用于在带有FSL接口的主设备和从设备之间快速传送数据;

3)提供了额外的控制位用于注释被传输数据,这个控制位对于从设备有多种用途,例如,将被传输数据作为一个控制字解码,或者用这个位来标识一个数据帧的起始或结束;

4)支持的FIFO深度最小为1,最大为8 k;

5)支持同步和异步2种FIFO模式,这允许FSL的主从端能以不同的速率工作;

6)支持2种FIFO实现方式:双端口Block RAM或LUT RAM,SRL16移位寄存器。

本系统处理器间通信采取的方案为:处理器1与处理器2之间通过XPS_mailbox核实现,处理器2与处理器3之间的双向通信通过一对FSL总线实现,一个核负责发送,另一个核负责接收,不存在阻塞而导致无法运行的问题。处理器核间的FSL总线相当于一个简单的基于FSL的数据通道FIFO_LINK。它用VHDL语言描述的实现过程如下:

architecture example of fifo_link is begin

FSL_M_Data<=FSL_S_Data;

FSL_M_Write<=FSL_S_Exists and(not FSL_M_Full);FSL_S_Read<=FSL_S_Exists and(not FSL_M_Full);

End architecture example;

2.3 系统软件的开发与设计

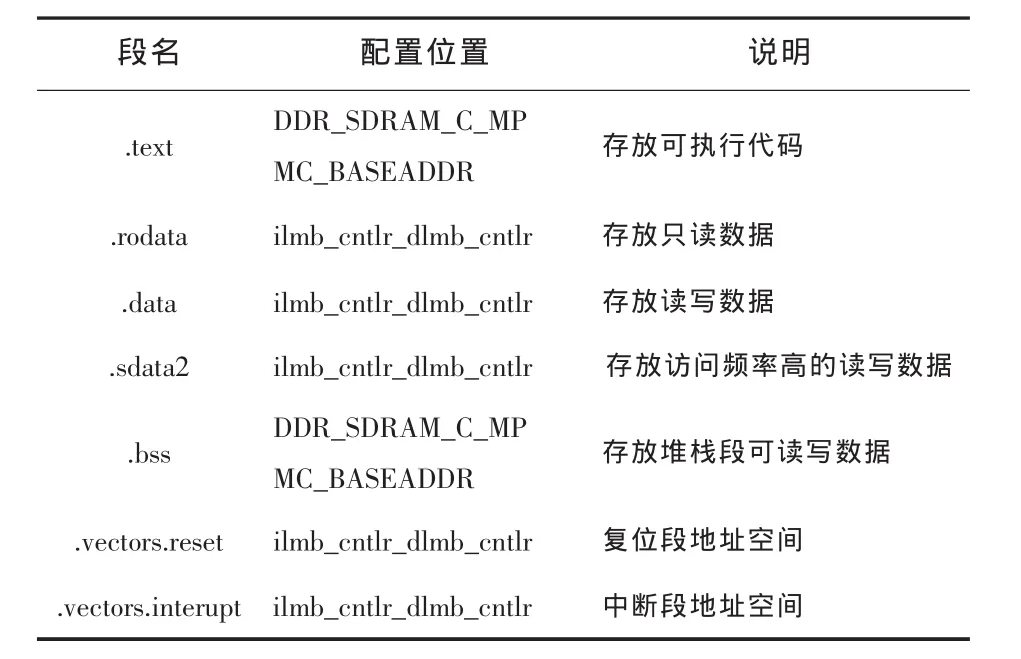

2.3.1 内存地址的映射

在多核处理器的设计中,任何一个共享内存必须进行地址映射。本系统在FPGA内部的BRAM中放置了共享代码,其中,软件应用程序接口与系统的设备通过平台工作室(XPS)设备驱动,首先在将要运行的应用程序名处右击,选中“Mark to Initialize BRAMs”,然后再右击应用程序名,点击“Generate Linker Script”,对链接脚本文件进行合理的设置。本系统链接脚本文件各个段配置如表1所示,实验表明,该配置能够满足系统实际运行要求及代码的高效执行[5]。

表1 程序各段配置空间Tab.1 Configuration space of programming sections

2.3.2 核间通信

1)共享内存的通信 多个处理核之间的通信可以使用进程间通信机制、共享内存或中断。共享内存是最基本的实现不同核上的线程间通信的机制(队列和消息)。在内存中有一个共享的全局变量或数据结构,则在处理器中的软件可以轻易地更新该变量的值,且对于其他处理器是可见的。所有这一切需要的是变量的地址或指向共享区域的指针。

在两个处理器处理共享资源的时候,为了对处理器的工作进行同步,避免出现共同资源占用的冲突,造成功能实现混乱,采用了XPS_Mutex核。对于共享资源,如一些常见的外设和对内存的共享访问,经常需要进行同步。XPS Mutex模式提供了一些可配置的内存映射互斥寄存器,它包括一个权值部分和一个处理器编号的组成部分。为了获得Mutex,处理器写入了一个软件分配的处理器ID,该ID与互斥寄存器和权值0相对应。Mutex判断两个同时访问Mutex的处理器,并在互斥寄存器中存储获胜处理器写下来的权值。如果Mutex已经被锁住,Mutex中的权值不会改变。每个处理器用读回Mutex的权值与自己的处理器ID进行比较,以验证该处理器有没有获得Mutex。

当Mutex成功挂载到系统中,程序开始会出现“#include

“cfg= XMutex_LookupConfig (XPAR_XPS_MUTEX_0_DEVICE_ID);

XMutex_LookupConfig(XPAR_XPS_MUTEX_0_DEVICE_I D);”

利 用 “XMutex_Lock_CPU (XMutex*InstancePtr,u8 MutexNumber,u8 CPUID)” 函数对处理器加锁。 利用“XMutex_Unlock_CPU(XMutex*InstancePtr,u8 MutexNumber,u8 CPUID)”对处理器进行解锁[6]。

2)消息的传递原理 利用XPS_Mailbox核来传递两个处理器通信时需要的信息和握手信号。XPS Mailbox硬件最初是在硬件设计部分描述的,它的软件驱动程序在处理器之间可以帮助提供消息传递功能。该软件的API是面向read()和write()调用的,因此软件可以将邮箱看作是发送和接收的一个串行访问的文件。该软件库提供阻塞和非阻塞的API版本。Mailbox是从一个或多个发送者传输信息到一个接收者的方案。它形成一种渠道,通过这个渠道信息从发送者端排列进入一个FIFO流,然后到达接收端,它可以被看作成两核之间一个简单的TCP/IP形式的信息通道。

Xilinx利用XPS Maibox核实现核间的通信,该核具有以下几个特点:

①每一个Mailbox核都有一对Mailbox FIFO,一个用来发送数据,另一个用来从特定的处理器接收数据。

②FIFO的深度由用户定义。

③FIFO利用的是分配的RAM或是BRAM资源。

④每一个Mailbox都有一对连接处理器用来通信的接口。虽然,多处理器都可以连接到接口上,但是推荐的方法是每一个Mailbox连接2个处理器[6]。

Xilinx的XPS Mailbox核适于中小规模的数据传输(数据一般小于100 Bytes)。发送端处理器需要从本地或外部内存复制整条信息,再将其写入FIFO;接收端处理器将信息复制到内存之中。在拷贝的过程中处理器浪费了一定的时间。

当信息到达Mailbox时,Mailbox接收端发送一个中断;当Mailbox不能再接收信息的时候,这个中断是无效的,中断控制器上可以使中断无效,且可以选择开或者关闭,所以,发送端与接收端的通信可以是同步的,也可以是异步的。

当Mailbox配置成功时会出现“#include和#include”。前者是Mailbox的函数库,后者是中断的函数库。在程序调用Mailbox时需要用语句“XMbox mbox;”对其进行引用。对于Mailbox的初始化,使用语句如下:

“cfg=XMbox_LookupConfig (MBOX_INTR_ID);

XMbox_CfgInitialize (&mbox,cfg,cfg->BaseAddress);”

对于异步消息传递功能允许一个处理器上的软件去前行,而不必浪费在一个旋转环数据到达的邮箱,从而隔离了从具有其他时间临界任务执行的快速接收机到缓慢发送者。异步消息传递功能也可以用作处理器间中断的一种形式。

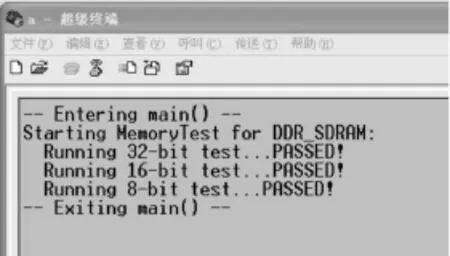

3 多核系统的调试

在系统工程中更新比特流,将比特流下载到目标FPGA芯片中,经综合、编译后,运行应用程序,进行调试。通过串口连接到目标板上应用系统中的XMD调试接口,在超级终端窗口查看观察结果。超级终端的配置为:每秒位数(B)=9600,数据位(D)=8,奇偶校验(P)=无,停止位(S)=1,数据流控制(F)=无。

核间共享内存的调试结果如图4所示。

图4 DDR_SDRAM存储器测试结果Fig.4 Testing result of DDR_SDRAM memorizer

核间消息传递的调试结果如图5、图6所示。

图5 处理器发送数据显示结果Fig.5 Display result of Processor sending datas

图6 处理器接收数据显示结果Fig.6 Display result of processor receiving datas

由调试结果知,系统可以正常工作,满足设计需求。

4 结束语

通过实验调试结果得知,基于Xilinx MicroBlaze多核系统的嵌入式系统开发[7],提高了系统的性能,由于MicroBlaze软核的可移植性,增加了系统设计的灵活性。文中将多个MicroBlaze软核嵌入到FPGA芯片中,得知多核比单核的性能有了显著地提高,且验证了PLB总线和FSL总线混连处理器的可行性,提高了核间的通信速度,降低了系统的开发成本,且表明该系统的设计具有一定的实用性。

[1]李剑阳,付宇卓,刘婷.基于MicroBlaze多核系统的设计及在FPGA 上的实现[J].微电子学与计算机,2009,26(7):160-163.LI Jian-yang,FU Yu-zhuo,LIU Ting.Design multi-core system using MicroBlaze and realize on the FPGA[J].Microelectronics& Computer,2009,26(7):160-163.

[2]陈锐,徐建华,蒋亚东.MicroBlaze嵌入式处理器的硬件加速模块设计[J].微处理机,2009(5):3-6.CHEN Rui,XU Jian-hua,JIANG Ya-dong.Design of hardware accelerator in MicroBlaze embedded processor [J].Microprocessors,2009(5):3-6.

[3]王玉峰,胥保华.基于FSL总线的UART外设IP核设计[J].单片机与嵌入式系统应用,2008(2):45-47.WANG Yu-feng,XU Bao-hua.Design of UART peripheral IP core based on FSL[J].Microcontrollers&Embedded Systems,2008(2):45-47.

[4]田耘,徐文波.Xilinx FPGA开发实用教程[M].北京:清华大学出版社,2008.

[5]王尔申,张淑芳,张芝贤.基于Xilinx MicroBlaze的嵌入式GPS 接收机研究[J].通信技术,2010,43(10):28-30.WANG Er-shen,ZHANG Shu-fang,ZHANG Zhi-xian.Study on embedded GPS receiver based on Xilinx MicroBlaze[J].Communication Technology,2010,43(10):28-30.

[6]张益嘉.一种基于FPGA的MPSoC架构的设计方法与实现[D].大连:大连理工大学,2009.

[7]蔡勉,田健生.向多核平台移植操作系统的研究[J].现代电子技术,2010(05):182-184.CAI Mian,TIAN Jian-sheng.Research on transplanting of operating system to multi-core environment[J].Modern Electronics Technique,2010(05):182-184.