采用CPLD的通用高速模糊控制器

薛大庆

哈尔滨达宇通信技术有限公司,黑龙江 哈尔滨 150080

模糊系统技术具有语词计算和处理不精确性、不确定性信息的能力,是解决许多实际复杂控制问题的有效方法。模糊控制器利用模糊集合理论将专家知识或操作人员经验形成的语言规则直接转化为自动控制策略。通常使用模糊规则查询表,用语言知识模型来设计和修正控制算法。

CPLD复杂可编程逻辑器件,是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。具有编程灵活、集成度高、设计开发周期短、适用范围广、开发工具先进、设计制造成本低、对设计者的硬件经验要求低、标准产品无需测试、保密性强。可实现较大规模的电路设计,被广泛应用于产品设计生产中。

Altera的MAXII 系列CPLD具有低功耗、低成本、高速度等特点,在现有CPLD产品中具有一定的优势。

1 模糊控制器结构

整个控制器硬件分为3部分:

1)模糊化:利用规定的隶属函数将真实的确定量转换成模糊量;

2)模糊推理及结论合成:利用以IF-THEN形式给出的控制规则将输入模糊量转化为输出模糊量,并将多条控制规则所形成的输出加以合成;

3)结果非模糊化:将控制器输出的模糊结果非模糊化,形成控制所需的确定值。

2 模糊控制器设计

1)模糊化

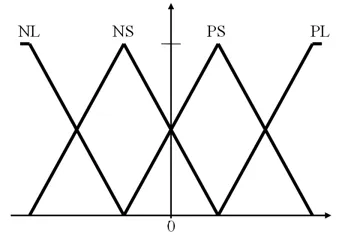

对于模糊化这里采用最简便易行的查表法,利用MAXII内嵌的8kFLASH存储器可以很容易构成一个模糊化表,变量量化采用8bit,模糊化结果为6bit,每个确定值模糊化后为{NL,NS,PS,PL},模糊结果采用两个8bit,分别是2bit隶属度(11=NL,10=NS,00=PS,01=PL),6bit隶属度值。逻辑结构如图2。因为每次精确值输入均转化成两项模糊值,所以每次精确值输入对应两次输出值。

图1

图2

2)模糊推理及结论合成

下表是本设计所采用的推理规则:

0 E NL NZ PZ PL NL PL PZ PZ NZ NZ PZ NZ NZ NL PZ NZ NZ NL NL PL NZ NL NL NL CE 际复的语修正

每条规则对应一个推理器。其VHDL程序如下:(此处省略该程序)

将输出分别送入推理器,由于每次精确值输入对应两次模糊值输出,所以在一次运算中推理器每个工作两次,共产生32个结果。

综合器将结果综合,产生一个模糊结论向量。综合算法采用模糊加法。

为了节约CPLD中的逻辑资源,综合器采用串行工作方式,先将结果存储器清零,然后每个结果依次与结果存储器相加,最后产生结论向量。

3)非模糊化:非模糊化采用重心法,公式为:非模糊化结果直接以PWM形式输出。

3 结论

通过对设计的计算机模拟和在某型等离子切割机机头调高器中的实际应用表明,采用CPLD设计通用高速模糊控制器具有以下特点:

1)电路简单:与采用的DSP或FPGA相比可大大简化电路,降低功耗,提高抗干扰能力;

2)控制运算速度快:采用MAXII时经测定运算速度可达到每秒1000万条规则,和DSP相当,远远高于单片机控制器;

3)实用性强:CPLD使用设计简单,可现场编程,控制算法,修改容易;

4)成本低:CPLD价格远低于DSP和FPGA,与单片机相当,还可将其他逻辑电路集成在芯片内,进一步简化电路,降低成本。

[1]李士勇.模糊控制.神经控制和职能控制论.哈尔滨工业大学出版社,2004,1.

[2]陈梅,杨琳琳,李鑫.直流调速系统的模糊/PID控制器设计,2008,2.

[3]MAX II Device Handbook.Altera Corporation,2009,8.