AD9520高速时钟发生器在5 Gs/s数据采集系统中的应用

蔡春霞,吴琼之

(北京理工大学信息与电子学院,北京100081)

高速系统时序设计中对时钟信号的要求非常严格,因为所有的时序计算均以恒定的时钟信号为基准。在高速高分辨率的ADC电路中,如果忽略量化噪声、热噪声、非线性误差等的影响,仅考虑在时钟抖动作用下的信噪比:

其中,J表示时钟抖动,fin表示输入信号频率。由式(1)可知,信噪比与时钟抖动密切相关[2]。采样时钟的微小抖动都将大大降低ADC转换电路的信噪比,使其有效位减小,而采样时钟的偏移也将影响两路ADC之间的正交一致性。高速数据采集系统中,ADC在很大程度上决定了系统的整体性能,而它们的性能又受到时钟质量的影响,传统时钟电路已难以满足系统要求的高速、低抖动的特性[3],针对这种情况,文中提出一种新的解决方案,采用AD9520为5 Gs/s数据采集系统中的高速ADC提供高质量、低抖动、低相位噪声的时钟信号,最后给出测试结果和分析。了2个参考输入端、1个参考时钟倍频器、1个参考时钟R分频器,1个整数N分频器、1个VCO可编程驱动器、可调延迟线和均分为4组的12个LVPECL输出,当输出频率低于250 MHz时,1个LVPECL可当作2个CMOS输出。AD9520系列的每款芯片均可配合频率高达2.4 GHz的外部VCO使用,内部VCO频率范围为2.27~2.65 GHz,工作频率可高达VCO最大频率,且每组LVPECL输出幅度可调2倍。

AD9520可选择内部VCO或者CLK作为要分配的时钟信号源,当内部VCO被选为源,则必须使用VCO分频器。当CLK被选为源,如果CLK频率低于最大的通道分频输入频率1 600 MHz,则不需要使用VCO分频器;否则,必须使用VCO分频器来降低频率,使之达到通道分频器可接受的值。

通过对寄存器地址0x1E1<1:0>进行设置来选择哪一种作为时钟源,参考频率为REF1和REF2的任意一个,可以差分时钟输入,或者外接晶振。本设计采用内部VCO作为时钟源,内部VCO与参考频率之间的关系如式(2)所示:

1 低抖动、低相位噪声锁相环时钟芯片AD9520

AD9520是ADI公司发布的系列时钟产品,该系列集成

可编程的参数N、P、A、B、R使得VCO与参考频率的组合变得灵活,设计简便。一般情况下,R取值为1,P的取值需要根据输出频率来决定,B必须不小于3或选择旁路(B=1),且B的取值要大于A。为了降低芯片的功耗和保护器件,AD9520提供2级安全关断模式,一个是按组关断,若组内的3个LVPECL输出均没有使用,可以选择;一个是组内未使用的LVPECL输出分别关断。

芯片的所有配置主要是通过串行控制端口来设置。AD9520的串行控制端口允许对配置AD9520的所有寄存器进行读写,支持单字节或多字节传输,以及MSB首传或LSB首传等传输格式,默认为MSB首传,可以配置为单一的双向I/O引脚(SDIO)或2个单向I/O引脚(SDIO/SDO)。AD9520默认处于双向模式、长指令模式。串行控制端口由4条控制线组成,如表1所示。

表1 串行控制端口说明Tab.1 Description of serial control port

SCLK用于串行控制端口读写同步,在时钟的上升沿寄存读数据位,下降沿寄存写数据位。SDIO可仅用作输入(单向模式),也可用作输入/输出模式(双向模式),AD9520默认为双向模式,本设计中AD9520工作在单向模式,通过设置寄存器0x000<7>可以完成相应设置。通过拉低,来初始化对AD9520的读写操作。

AD9520的串行控制端口16位指令字如表2所示。

表2 串行控制端口16位指令字MSB首传Tab.2 Serial control port,16-bit instruction word,MSB first

AD9520写入一个16位指令字,为串行控制端口提供与数据传输相关的信息,其中MSB位指明读写状态(高为读,低为写),随后2个位<W1:W0>指明传输的字节长度,最后13位指明从何处开始读写操作的地址<A12:A0>。<A12:A0>这13位选择寄存器映射的地址来写入或读取数据,只有<A9:A0>位需要覆盖AD9520使用的0x232寄存器范围,<A12:10>位必须总是0 bit,对于多字节传输,该地址是起始的字节地址。

在MSB首传模式,<W1:W0>指明数据字节数量,如表3所示。

表3 传送字节Tab.3 Byte transfer count

AD9520串行控制端口的写时序如图1所示。

图1 串行控制端口写时序16位指令字Fig.1 Serial control port write-MSB first,16-bit instruction,timing measurements

2 AD9520在5Gs/s数据采集系统中的应用

图2所示为5 Gsps高速数据采样系统的原理框图。所用ADC型号为EV8AQ160,8 bit采样精度,内部集成4路ADC,最高采样率达5 Gsps,可以工作在多种模式下[4]。通过对ADC工作模式进行配置,ADC既可以工作在采样率为5 Gsps的单通道模式,也可以工作在采样率为2.5 Gsps的双通道模式。模拟输入信号经过BALUN型高频变压器完成单端信号到差分信号的转换,通过ADC进行采样,然后把数据送入FPGA中作进一步处理。本设计采用Xilinx公司发布的Virtex-6系列FPGA,具体型号为XC6VLX240T-1156C[5]。

2.1 时钟模块组成结构

本设计中,AD9520的任务是给ADC提供一个2.5 GHz时钟,而实现这一要求还须为VCO提供一个外部参考时钟源,这里采用一个优质的10 MHz时钟作为参考时钟源。ADC在给FPGA传输数据的同时,也会输出4路312.5 MHz的同步采样时钟,如图2所示。

通过相应寄存器的设置把内部VCO配置为2.5 GHz、PDF频率设置为10 MHz。要获得满意的PLL性能,需要对PLL进行正确配置,外部的环路滤波的设计对PLL的正常工作至关重要。使用ADIsimCLK软件通过输入需要的参数可得到能使AD9520达到高质量时钟输出的环路滤波结构,环路带宽默认为100 kHz。由于环路带宽不仅与参考时钟源的性能有关系,而且还与AD9520所在硬件环境的参数有关系,所以环路带宽须根据实际情况具体调节。PLL的外部环路滤波器的结构如图3(a)所示,设置完成后,理论仿真得到的输出时钟相位噪声如图3(b)所示。本设计的环路滤波器参数设置为:C1=6 200 pF,R1=750 Ω,C2=470 pF,R2=1.5 kΩ,C3=220 pF。

图3 PLL环路滤波器结构及仿真输出时钟的相位噪声Fig.3 Structure of PLL loop filter and phase noise of simulating output clock

2.2 寄存器配置

AD9520的配置必须通过载入控制寄存器来设置,只有在控制寄存器写入适当的配置参数,以及按照正确的顺序写入后,才能使得AD9520正常工作并且输出要求的2.5 GHz时钟。

内部PLL使用外部环路滤波器来设置环频宽,当改变PLL的R、P、B、A等分频器的值以及变换参考时钟频率源时,必须初始化VCO校准,即需要对VCO进行校准以保证AD9520按照用户的要求产生相应的时钟,获得最佳性能。

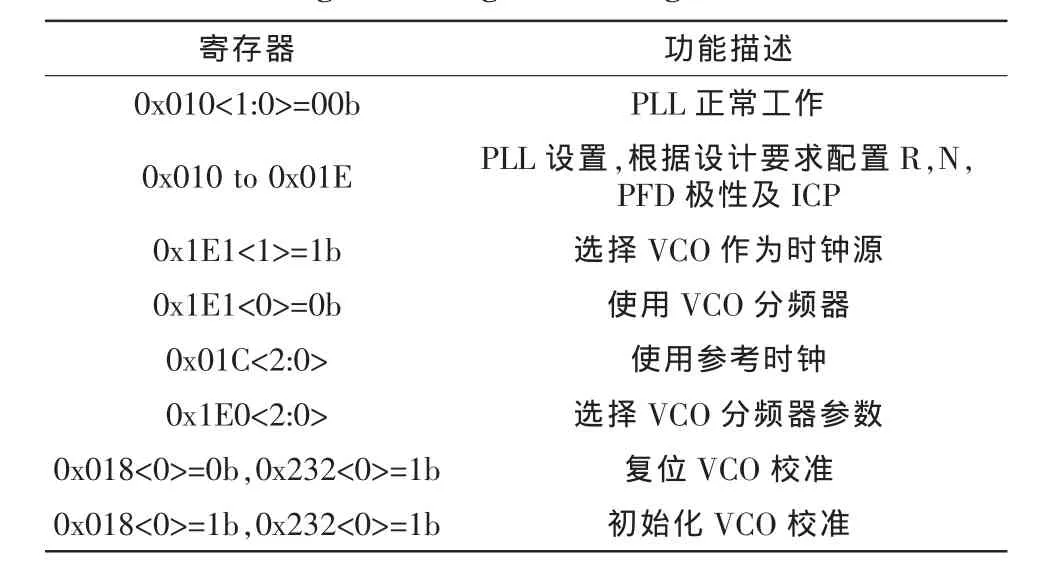

对于内部VCO和时钟分频的应用,需要使用如表4所示寄存器的设置。

由式(2)可知,N=P×B+A。

本设计中所用参考频率fREF=10MHz,VCO频率fVCO=2.5GHz,根据芯片的工作要求,VCO频率应该小于P预分频器允许的最大频率,因此在本设计中,P预分频器的取值应为16 dM或者32 dM,参考频率既不进行分频,也不使用倍频器,即R设置为1。取A为10,则由(2)式,B应取15。以上分频器的设置可以通过其对应的寄存器设置完成。如表5所示。

使用内部VCO,存在两条可用的信号路径,一条是VCO时钟被送到VCO分频器,接着经过4个独立的通道分频器后输出,另一条是不经过VCO分频器和通道分频器,VCO时钟直接递到输出管脚。由于本设计要求的输出时钟为2.5 GHz,而且通道分频器的最大输入频率为1 600 MHz,因此将VCO时钟直接递到输出管脚,此时2.5 GHz时钟以50%占空比输出。本设计中2.5 GH在的输出管脚为OUT9,根据芯片使用要求将寄存器0x19B<1>设置为1b。为减小功耗和保护器件,其他未使用到的通道分频器和对应的输出管脚选择安全关断模式。

表4 使用内部VCO时寄存器设置Tab.4 Register settings when using internal VCO

表5 R和N(A,B,P)分频器的设置Tab.5 Settings of R divider and N(A,B,P)divider

如前所述,为使AD9520正常工作,除了要在控制寄存器中写入适当的参数,还要保证控制寄存器写入顺序的正确性。具体配置顺序如图4所示。

图4 寄存器配置流程图Fig.4 Register configuration flowchart

2.3 测试结果

极高速ADC(采样率大于1 Gsps)需要低抖动的采样时钟,目的是为了维持一定的信噪比(SNR)。8位和10位转换器最优情况时的背景噪声是由量化噪声决定的[6],对于一个N位ADC对一个满幅正弦波进行采样时,SNR与有效位数之间的换算公式为:

为了测试时钟对ADC的性能影响,需要获得输出数据的SNR。这里采用Xilinx公司ISE软件中的ChipScope Pro工具将逻辑分析器、总线分析器和虚拟I/O小型软件核直接插入到设计当中,直接查看ADC输出的数字信号,这些信号在操作系统速度下或接近操作系统速度下被采集,并从编程接口中引出,再将采集到的信号通过ChipScope Pro逻辑分析器进行分析。

首先让ADC工作在采样率为5 Gs/s的单通道模式下,用特定的测试模式来检验ADC与FPGA之间的数据接口的准确性。将测试程序下载到FPGA并运行后,用ChipScope Pro抓取ADC的输出数据如图5(a)所示。然后在单通道模式下不使用测试模式,输入2 MHz的正弦信号,用ChipScope Pro抓取ADC的输出数据如图5(b)所示。

图5 用ChipScope Pro抓取ADC的输出数据Fig.5 Output data of ADC using ChipScope Pro to get

从图5(a)中的数据可以看出,各个通道均以约定的格式输出,说明ADC与FPGA之间数据接口已经准确连通。图5(b),输入正弦信号时用BUS PLOT工具将抓取到的数据实时画图,得到的波形平滑,计算其信噪比为42.9 dB,由式(3)计算得到ADC的有效位数为6.6 bit。实测表明,AD9520输出的2.5 GHz时钟具有较高的性能,整体指标达到设计要求。

3 结束语

通过对AD9520输出的时钟应用在ADC时测试得到正确的数据及波形,以及计算得到ADC有效位数为6.6 bit,表明AD9520的输出时钟具有较高的质量,性能良好,并在5 Gsps高速数据采集系统中满足应用要求。

[1] Devices A.12 LVPECL/24 CMOS Output Clock Generator with Integrated 2.5 GHz VCO AD9520-1 Data Sheet[EB/OL].http://www.analog.com/static/imported-files/data_sheets/AD9520-1.pdf

[2] 胡智宏,廖旎焕.高速ADC时钟抖动及其影响的研究[J].微型机与应用,2011,30(2):85-88.HU Zhi-hong,LIAO Ni-huan.Research of high-speed ADC clock jitter and its effects[J].Microcomputer&its Applications,2011,30(2):85-88.

[3] 胡广洲,赵忠凯,司锡才.AD9516-3时钟设计及在中频数字系统中的应用[J].应用科技,2009,36(7):28-32.HU Guang-zhou,ZHAO Zhong-kai,SI Xi-cai.The design of clock AD9516-3 and the application in IF digital systems[J].Applied Science and Technology,2009,36(7):28-32.

[4] English E2V Corporation.EV8AQ160 QUAD ADC Data Sheet[EB/OL].http://www.e2v.com/assets/media/files/documents/broadband-data-converters/doc0846I.pdf.

[5] Xilinx Corporation.Virtex-6 series FPGA Data Sheets[EB/OL].http://www.xilinx.com.

[6] Catt J.高速A/D转换器的时钟设计[R].美国国家半导体公司应用注释1558,2007.