埋置型叠层微系统封装技术

杨建生

(天水华天科技股份有天限公司发展规划部,甘肃天水741000)

微电子机械系统(MEMS)从航空体系到家用电器提供了非常广阔的潜在性应用范围,与功能等效的宏观级系统相比,在微米级构建电子机械系统的能力形成了在尺寸、质量和功耗方面极度地缩小。保持MEMS微型化的潜在性的关键之一就是高级封装技术。如果微系统封装不好或不能有效地与微电子集成化,那么MEMS的很多优点就会丧失。采用功能上和物理上集成MEMS与微电子学的方法有效地封装微系统是一种具有挑战性的任务。由于MEMS和传统的微电子工艺处理存在差异,在相同的工艺中装配MEMS和微电子是复杂的。例如,大多数MEMS器件需要移除淀积层以便释放或形成机械结构,通常用于移除淀积材料的这些工艺对互补金属氧化物半导体(CMOS)或别的微电子工艺来说是具有破坏性的。很多MEMS工艺也采用高温退火以便降低结构层中的残余材料应力。典型状况下退火温度大约为1 000℃,这在CMOS器件中导致不受欢迎的残余物扩散并可熔化低温导体诸如通常用于微电子处理中的铝。

缓和这些MEMS微电子集成及封装问题的一种选择方案就是使用封装叠层理念。叠层或埋置芯片工艺已成功地应用于微电子封装。在基板中埋置芯片考虑当高性能的内芯片互连提供等同于单片集成的电连接时,保护微电子芯片免受MEMS环境影响。埋置型芯片封装尤其适合于微系统封装诸如元器件必须裸露于外部环境中的微光学器件或天线等。

已证明的几种MEMS封装方法,考虑到埋置型MEMS封装,这些方法在实际封装安装或创造适合于MEMS环境的模块装配期间,采用微电机技术。本文中描述的埋置型叠层封装方法不同于扩展现存的多芯片及微电子封装工艺。当允许与微电子高性能集成时,创造适合于MEMS的模块。MEMS埋置型叠层工艺是为微电子封装研发的挠曲基板上芯片封装的衍生物。使用COF初始的可行性已证明,那些结果突出了更进一步研究使MEMS器件损坏最小化的工艺的需要。

1 COF/MEMS封装工艺

在基本COF工艺中,当芯片被埋置于如图1所示的塑料基板中时,通过布图的叠层完成电互连。COF互连叠层在芯片粘附之前预装配,叠层的底层通常为聚酰亚胺薄膜,叠层的顶层也可为聚酰亚胺薄膜。铜用于使预装配叠层金属化,采用聚酰亚胺或热塑胶粘剂在COF叠层上面朝下粘附芯片,把芯片压焊到叠层上之后,使用塑料模塑成形工艺诸如传递、压缩或注射模塑在元器件周围形成基板,在基板模塑期间模块温度不超过210℃。

下一步工艺就是芯片与叠层进行电连接,穿过叠层到元器件焊盘通过激光钻通通路完成电连接。接着为了形成电互连,把Ti/Cu金属化进行溅射并布图,依据目标应用采用不同类型的顶层金属化。对MEMS封装而言,通过增加额外的激光融除步骤允许物理通路到MEMS器件(见图1)来增加COF工艺。也要进行附加的等离子蚀刻使在裸露窗口中积累的聚酰亚胺残余物最小化。接着在COF叠层移去之后把裸露的MEMS器件释放。

图1 制造后的COF/MEMS封装及MEMS通路的激光融除

2 改进COF/MEMS激光融除工艺

在初始封装分析阶段发现的最严重问题就是由于激光融除过度的加热造成MEMS器件翘曲或失效。最易受过热影响的器件是到基板通路的热损耗弱的长、薄结构的器件诸如热驱动器。另外,MEMS芯片的材料特性也可促成热损坏问题。在350 nm状况用连续的氩离子激光完成COF激光融除。由于与融除有关的热问题较少,短脉冲、高瞬时功率激光是较好的,然而,在标准的COF工艺中采用的氩离子激光的使用授权对成本和设备进行限制。在350 nm状况下氩离子激光特别会损坏多晶硅试验器件,因为它们实际上吸收那个波长的所有入射的激光能量。再者,MEMS芯片上未覆盖的顶部多晶硅层特别对热损坏易受影响,因为在融除期间它是直接裸露于激光束。

2.1 叠层融除概述

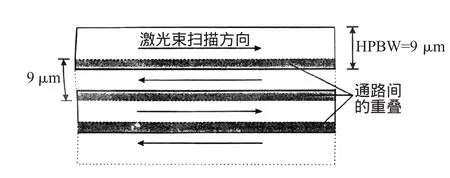

如前所述,采用350 nm状况下连续不断的氩激光运作完成COF工艺中的激光融除。激光的半功率射束宽度(HPWB)标称为9μm。如图2示出了在融除期间使用的激光扫描图案。对每个通路而言,在6~12mm中穿过模块表面进行激光扫描,当认为激光束影响模块表面时,使用快门控制。

图2 COF/MEMS模块上融除扫描图案

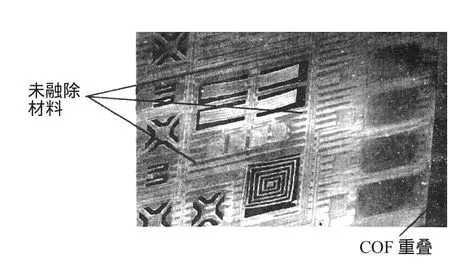

在交叉通路的末端,使激光正交步进并颠倒过程使另一通路穿过模块。正交步进的数量决定通路之间的重叠数。使用重叠来改进融除的均匀性。由于功率仅为中心激光束的一半,因此在激光束边缘融除较少的聚酰亚胺薄膜单个通路之后,聚酰亚胺薄膜融除的深度是不一致的。选择不是太大或不是太小的重叠是关键,是在先前通路上得不到足够功率的融除区域的又一机会。大的重叠可产生大量的融除而不足的重叠将产生不能融除的材料保留于模块上,图3示出了一排留在大块微机电MEMS芯片上的叠层材料。通路间的重叠太小不能认为融除是良好的一致性。扫描率在决定融除工艺特征方面是又一关键性因素,慢扫描率考虑更多的目标时间,将融除更多材料,采用较快的扫描率清除残留的聚酰亚胺薄膜或使过热的目标区域的危险性最小化。

图3 在COF模块由于通路间不充足重叠在裸露的MEMS芯片上留下的一排排未融除的材料

2.2 叠层融除特性

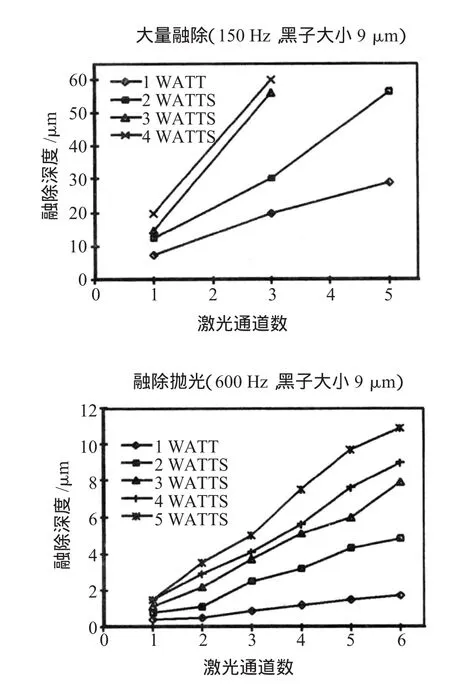

为了测量并分析激光融除工艺,对几个COF封装样品进行测试,由于在实验室激光是设定的,只有限定数目的扫描率是可用的,因此选择150 Hz(1 350 m/s)作为融除大量材料的扫描率,选择600 Hz(5 400 μm/s)用于抛光融除,清除大量融除后残余材料,只有两个变量参数为通路间的叠层和功率等级。通路间的叠层是调研的第一量,采用改变的叠层融除试验样品来决定那个叠层将提供最大的一致性。对试验样品的分析表明相邻通路中心之间的间距为3μm,提供最均匀的融除覆盖,在随后的试验中使用此间距来确定融除深度对激光功率变换的敏感性。

下一步就是测量与功率级有函数关系的融除深度,对此试验采用有60μm厚的叠层COF封装样品。当大量融除的激光功率从1~4W变换,融除抛光的功率从1~5W变换时,在试验样品的叠层中融除窗口。伴随特定功率级每个通路,用表面光度仪测量叠层融除的深度。图4示出了这些试验的结果。

2.3 改进叠层融除工序的研究

描述了激光融除工艺特征之后,对改进的融除进行调研。首先对显示MEMS器件损坏的COF/MEMS模块采用1.6W功率进行融除,然而直到激光进入埋置芯片几个微米之内时,功率才下降,因此对采用较低激光功率新的融除程序和移去叠层的替代法进行研究和开发。

较低功率融除的第一次尝试没有成功。把激光功率设定到1W,尝试是否可通过降低功率来提高MEMS器件的可靠性。然而,在1W(150 Hz)状况下融除是缓慢的,并且在几个通路之后出现了过度的残余物,产生了不受欢迎的副作用。再者,残余物开始变硬,对融除造成了困难,不能用O2或CF4/O2等离子蚀刻移除。

图4 COF/MEMS重叠融除深度与功率级比较

下一个程序就是结合高功率融除移去大部分的叠层,接着当融除继续到更接近芯片时降低功率采用2 W(150 Hz)的功率融除COF/MEMS模块,直到剩下的材料不到10μm。采用3W(600Hz)的融除抛光来移除剩余材料。

此程序比移去大部分叠层先前的尝试效果更好,并且残余物不变硬,但融除抛光不能彻底移去大量融除后剩下的接近10μm的残余物。虽然采用(CF4/O2)的4 h的等离子灰来除去残余叠层物,但是当除去残余物时,等离子灰循环太长引起了在整个模块上方叠层的分层现象,也开始蚀刻MEMS芯片上裸露的多晶硅。

把实际降低融除诱发损坏方案与前面两次尝试相结合,第一次尝试失败,原因在于1W的功率不能足够融除电介质残余物变硬前的材料。第二程序失败,是由于融除抛光和等离子灰移除之后剩下大量的材料。第三程序的成功是由于采用了三步融除并伴随短的等离子灰移除,高压水擦洗有助于使每个步骤后剩下的残余物最小化,从而使硬化的可能性最小化,此程序的步骤如表1所示。

表1 COF/MEMS叠层改进的融除方案

第一次融除步骤的目的为是移除足够的叠层而考虑使用设定的低功率,在2 W(150 Hz)状况下用3个通路完成这一步骤,该步骤移除了第一层聚酰亚胺薄膜和内层胶粘剂(约30μm)。第二融除步骤在1W状况下包括5~7通路,此步骤融除底部聚酰亚胺薄膜(约25μm),并留下仅仅较低的胶粘剂层通过融除抛光移除。融除抛光(6个通路,3W,600 Hz)清除大部分残余物电介质和胶粘剂。

融除之后,使用等离子灰和高压水擦洗,在低功率融除状况下从第二次尝试得到的教训之一就是短的(小于90m in)等离子灰(CF4/O2)在除去融除抛光后留下的残余物方面是非常有效的。采用低压(约133.3 Pa)使封装芯片上氮化物或氧化物蚀刻最小化,最后步骤就是高压水擦洗,为的是除去MEMS芯片表面上的硅石残余物,在每个融除步骤后也要使用高压擦洗。

3 二氧化硅层的热保护

在COF封装之前,把MEMS芯片用保护性二氧化硅涂层覆盖,通过激光融除使其上方区域裸露,初始采用300 nm到1μm厚的保护性氧化物使裸露表面诸如反射微镜盘上的残余物最小化。保护性氧化物涂层意外的益处之一就是降低了MEMS器件对激光融除的易损性,即使在1.6 W状况下进行融除,氧化物涂层区域中的MEMS器件显示出较少的激光加热损坏的证据。降低损坏最可能的原因是通过氧化物层提供了热隔离。

COF/MEMS工艺中融除首要的是光热现象。采用高于1 ms脉宽的聚酰亚胺的紫外激光融除已被表明是首要的光热反应现象。在COF/MEMS工艺中采用激光的脉宽可确定为激光束的HPBW覆盖表面上点的时间量。通过此定义,大量融除和融除抛光步骤的脉宽依次为6.67 ms和1.67 ms,这显示出光热融除是可预料的。

在350 nm聚酰亚胺薄膜的光热融除温度阈值的最小值为850℃,理论化的聚酰亚胺薄膜最佳的光热融除发生的温度为1 100~1 500℃。结果,接近聚酰亚胺薄膜融除的任何材料,诸如埋置型MEMS芯片,使经受至少850℃的热源,可能高达1 500℃,这一数值的温度最易导致多晶硅结构中的失效发生。

二氧化硅的热传导率为1.0~1.4 WK-1m-1,大大低于硅的热传导率160 WK-1m-1或多晶硅的热传导率30 WK-1m-1。溅射或旋涂玻璃(SOG)氧化物保护层的存在对保护采用顶部多晶硅层的MEMS结构是特别重要的,因为这些器件裸露在表面,否则对融除的热效果没有绝缘作用。

4 采用改进的叠层融除协议的结果

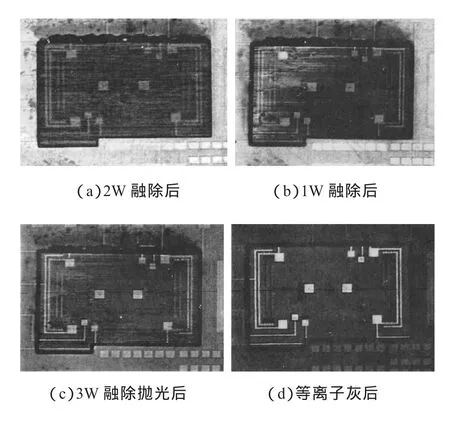

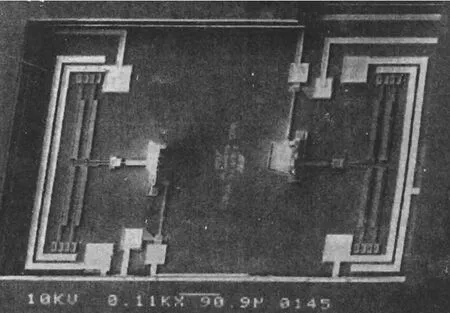

改进的融除方案的使用非常成功,图5示出了在COF/MEMS模块中含有一对扫描微镜窗口的融除工艺。图 5 描绘了(a)2W,(b)1W,(c)3W融除抛光和(d)(CF4/O2)等离子灰之后融除的状况。注意到伴随等离子灰在表面现象的情况,使用与等离子清洗有联系的改进的融除方案极大地降低了试验芯片上激光诱发损坏现象的发生。再者,二氧化硅保护层的使用极大地降低了残余物并且有助于MEMS器件额外热绝缘的形成。图6示出了经试验发现的封装和组装的扫描微镜,与未封装的控制芯片上相同器件具有相同的运作特性。融除宽度为1 200μm,这些器件与图5中所示的器件一样,封装后手工与微探针一起装配并释放。

图5 改善融除计划后图案

图6 封装及组装扫描微镜

5 应用

COF/MEMS工艺拥有部分富有吸引力的MEMS和电子封装的特征。由于采用了直接金属化,芯片互连具有极低的寄生电容和电感。使用的三维封装技术,实际上是把焊盘定位于芯片上任何地方的能力,以及从很多装配技术主宰芯片的能力。当COF/MEMS工艺不能主导每一种类的MEMS器件,存在宽范围的器件诸如微光学器件、RFMEMS、以及微流体器件是适用于此工艺的。成本是此封装工艺的限制之一,为了降低COF工艺的成本需做出极大的努力,对应用于诸如军品及航天电子领域而言,要求其具有独特的性能,主要采用此封装替代品。在本文中证明的MEMS封装技术增加的步骤,不能显著地增加到每个模块的总成本上,由于所做的每个努力是使用本地化现存的COF工艺的设备和工艺。再者,在文中包含的埋置型叠层理念可通过适于特定能力的折中成本的其他方法实现。

如前所述,COF/MEMS封装最先实际应用之一就是用于主导微光学器件。活塞微镜的COF/MEMS封装技术是特别有吸引力的,原因是这些器件在释放之后不需要装配。因此,主要的要求就是提供微镜的光存取,并在电学方面集成微镜和控制电路。图7示出了COF/MEMS微镜组装设计,通过采用在镜芯片下方放置微控制器的三维理念可获得更小型化的封装。如图7所示,小的镜阵列(5×5)被成功地封装并在包含简单微电子驱动电路的COF/MEMS模块中运作。含有较大阵列的封装合并全功能微镜控制器芯片。COF/MEMS封装的其他应用包括埋置型RF天线和开关阵列,与活塞微镜一样,很多RFMEMS器件在释放后不需要组装并与COF/MEMS封装技术工艺非常兼容。在COF/MEMS封装中埋置RF MEMS开关和天线将促进微波系统结构的小型化。

图7 有5×5阵列的活塞微镜的COF/MEMS封装

6 结束语

本文论述了适于封装微电子机械系统(MEMS)的挠曲基板上芯片(COF)封装工艺,对降低由于激光融除对MEMS器件损坏的潜在性的理论也进行了讨论并付诸实施。说明采用具有等离子清洗和高压水擦洗变换的激光融除功率等级,可提供有效的除去COF叠层的方法而不损坏埋置型MEMS器件。另外,发现使用热绝缘层可提供免受激光相关热损坏的额外保护。采用COF/MEMS工艺可成功地封装与微镜和微电子驱动电路合并于一起的简单的微系统。

[1]L.guerin,M.A.Schaer,R.Sachot and M.Dutoit.New multichip-on-silicon pachaging scheme forM icrosystems[J].Sens.Actuators,A,2000,52:156-160.

[2]J.Butler,V.Bright,and J.Reid.Scanning and rotating micromirrors using thermalactuators[C].inProc.Spie.Opt.Scanning Syst,3131,July 3001,134-144.

[3]张海霞,赵小林等译.微机电系统设计与加工[M].北京:机械工业出版社,2009.

[4]田文超.微机电系统(MEMS)原理、设计和分析[M].西安:西安电子科技大学出版社,2009.

[5]肯.吉列奥,中国电子学会电子封装专委会(译).MEMS/MOEMS封装技术:概念、设计、材料与工艺[M].北京:化学工业出版社,2008.