基于AD9910雷达信号发生器设计

王刚,徐晚成

(西安电子科技大学电子工程学院,陕西西安710071)

雷达信号的种类繁多,早期雷达信号多为简单脉冲,随着雷达技术的不断发展,脉冲压缩信号逐渐取代简单脉冲,成为雷达的主流信号。线性调频就是脉冲压缩技术中常用的一种,在高分辨率、相控阵、合成孔径等雷达中得到了广泛采用。DDS由于具有幅度和相位一致性好、频率转换时间短、频率分辨率高、输出频率相对带宽较宽、输出波形相位连续等优点,成为生成稳定线性调频信号的主要方法[1]。AD9910是ADI公司2007年推出的一款专用DDS芯片,工作频率高达1 GHz,适合模拟单频脉冲,线性调频及连续正弦波等雷达信号。

1 AD9910功能特点

1.1 AD9910简介

AD9910内置14位数/模转换器,支持1 GS·s-1的采样速率和快速相位及幅度切换,具有PLL REFCLK乘法器,能够在400 MHz的频率下,生成频率捷变正弦波形。AD9910可通过串行I/O端口设置内部控制寄存器内容,其内部包含静态RAM,支持多种频率、相位和幅度调制[2]。

AD9910支持4种工作方式:单频模式、RAM调制模式、DRG调制模式和并口调制模式。芯片可在一种或几种模式下工作,由控制寄存器位决定。根据具体控制位的不同,频率、幅度和相位参数可由不同的工作模式提供,组合生成所需信号。

DDS信号控制参数在不同模式下的提供方式不同:单频模式下,由与串行I/O口相关的可编程寄存器直接提供;RAM模式下,DDS信号控制参数保存在内部RAM中,通过指令调用;DRG调制模式下,由DRG发生器提供;并行数据端口模式下,由并行端口直接提供。各种调制模式下一般只用一种DDS信号控制参数提供方式。未调制的信号控制参数保存在相应的编程寄存器中,根据所选工作模式自动传送给DDS。

1.2 DDS内核

DDS内核是AD9910的核心部分,它根据输入的波形参数合成相应的数字波形。DDS内核由标准参考频率源、32位相位累加器、ROM波形存储器和14位数模转换器DAC构成[3]。相位累加器在参考时钟的控制下,不断对频率控制字进行线性相位累加,输出32位二进制码作为波形ROM的取样地址,对波形ROM进行寻址,完成相位到幅值的转换[4]。然后将输出的幅值码送到D/A转换器,产生所需波形信号。

AD9910的输出频率fOUT由输入的频率调谐字FTW控制。fOUT、FTW和fSYSCLK之间的关系可表示为

DDS信号的初始相位Δθ由16位的相位偏移字POW控制,它们之间的关系可表示为

DDS信号的幅度A是经过归一化处理的,由14位的幅度比例因子ASF控制,它可表示为

可以看出,改变FTW、POW和ASF的值,就可以控制输出波形的频率、相位和幅度,生成各种信号波形。

1.3 DRG工作模式

AD9910中集成了全数字式斜坡发生器,用于控制生成信号的相位、频率和幅度。DRG模式需用9个控制寄存器位、3个外部引脚、2个64位寄存器和1个32位寄存器[5-6]。在DRG控制寄存器位中,若DRG使能位禁用,其它控制输入均无效。DRG的总线输出为32位无符号数据,可以作为任一波形控制参数,通过数字斜坡目的字选择波形参数类型。

通过控制DRCTL引脚来控制DRG的调谐方向:当置为逻辑1时,DRG做正调谐;当置为逻辑0时,DRG做负调谐。

DRG有两种工作模式,分别为正常斜坡发生模式和非驻留斜坡发生模式,由控制寄存器的两个非驻留位决定。在正常斜坡发生过程中,当DRG输出达到编程设定的上限或下限时,如果工作参数不变化,DRG会始终保持在上下限值。而在非驻留操作中,如果非驻留高位置1,当DRG达到上限值时,DRG会自动直接跳到下限值;如果非驻留低位置1,当DRG达到下限值时,DRG会自动直接跳到上限值。

2 系统总体设计

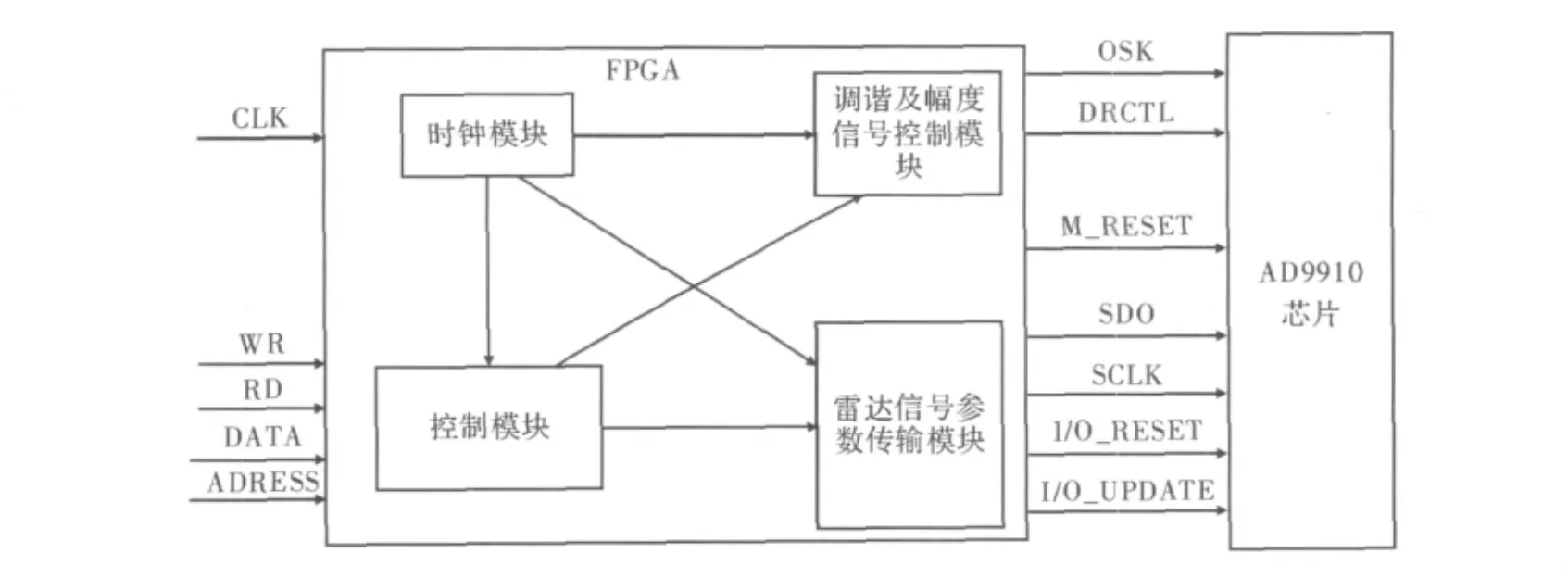

系统主要由DSP,FPGA和AD9910组成。DSP负责提供AD9910工作频率,调频带宽,调谐状态的参数,FPGA将DSP传输过来的并行数据转换成串行数据并以SPI形式传输给AD9910。系统总体框图如图1所示。

图1 总体框图

2.1 软件设计

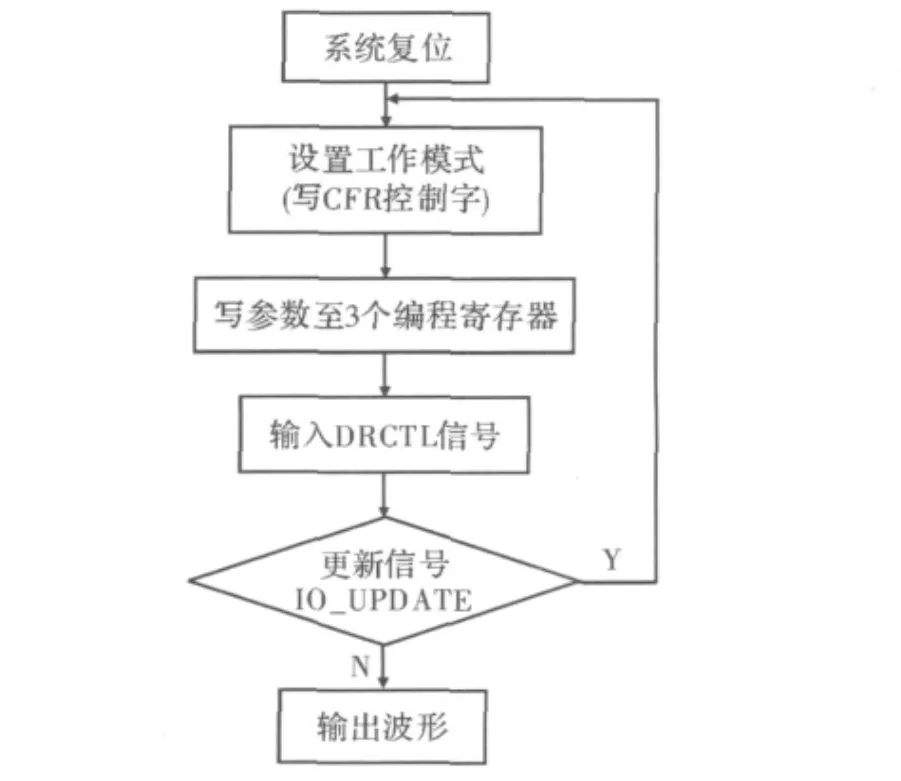

FPGA控制AD9910产生线性调频信号可分为以下几个步骤:

(1)向CFR1寄存器的位[31]写入0,禁用RAM模式;向CFR2寄存器的位[19]写入1,使能DRG模式;向CFR2寄存器的位[21∶20]写入00,设置DDS控制参数为频率。

(2)将参数值写入DRG的三个编程寄存器。向2个64位寄存器分别写入上下限值和步长参数,向32位寄存器写入速率参数。

(3)通过DRCTL引脚控制斜率的方向,DRCTL=1为正调谐,DRCTL=0为负调谐。

(4)DROVER引脚提供外部信号表示DRG状态,当DRG输出处于上限或下限时,DROVER引脚输出高电平,其他时候DROVER引脚输出低电平。软件流程图如图2所示。

图2 软件流程图

2.2 接口电路控制设计

AD9910的系统时钟由晶振提供或外部时钟直接提供,设计采用晶体振荡器提供。晶振产生20 MHz的高稳定时钟信号通过REF_CLK引脚输入到AD9910,经过AD9910内部的锁相环倍频后产生需要的采样时钟。

线性调频信号由AD9910的DRG模式产生,需设置AD9910的起始频率、步进间隔、频率变化斜率以及调谐方向。FPGA负责产生AD9910需的所有信号参数,其内部具体分为时钟模块、控制模块、调谐及幅度控制模块和雷达信号参数传输模块。

时钟模块负责产生其他模块的时钟信号,通过对外部晶振输入的信号进行倍频、分频产生需要的所有时钟,其中对信号倍频是由FPGA内部的PLL完成。

控制模块对由DSP传输过来的指令进行译码,控制其他模块的信号输出以及AD9910的芯片复位信号M_RESET。

调谐及幅度控制模块产生AD9910所需的OSK及DRCTL信号。OSK控制脉冲信号的脉宽和脉冲重复周期,DRCTL控制调谐方向。

雷达信号传输模块对由DSP传输过来的并行数据进行并串转换,将并行的雷达参数信息转换为串行数据,通过非标准的SPI串口送给AD9910。该模块还同时负责产生AD9910的其他控制信号,包括I/O_RESE信号、I/O_UPDATE信号及DRHODLD信号。AD9910接口电路如图3所示。

图3 AD9910接口电路

3 实验结果

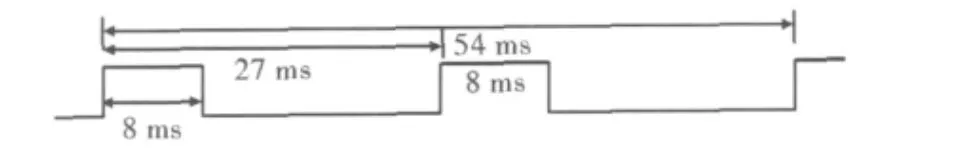

实验期望产生中心频率为75 MHz,带宽为30 MHz的雷达脉冲信号,脉内采用正线性调频。期望波形如图4所示。

图4 雷达脉冲期望波形

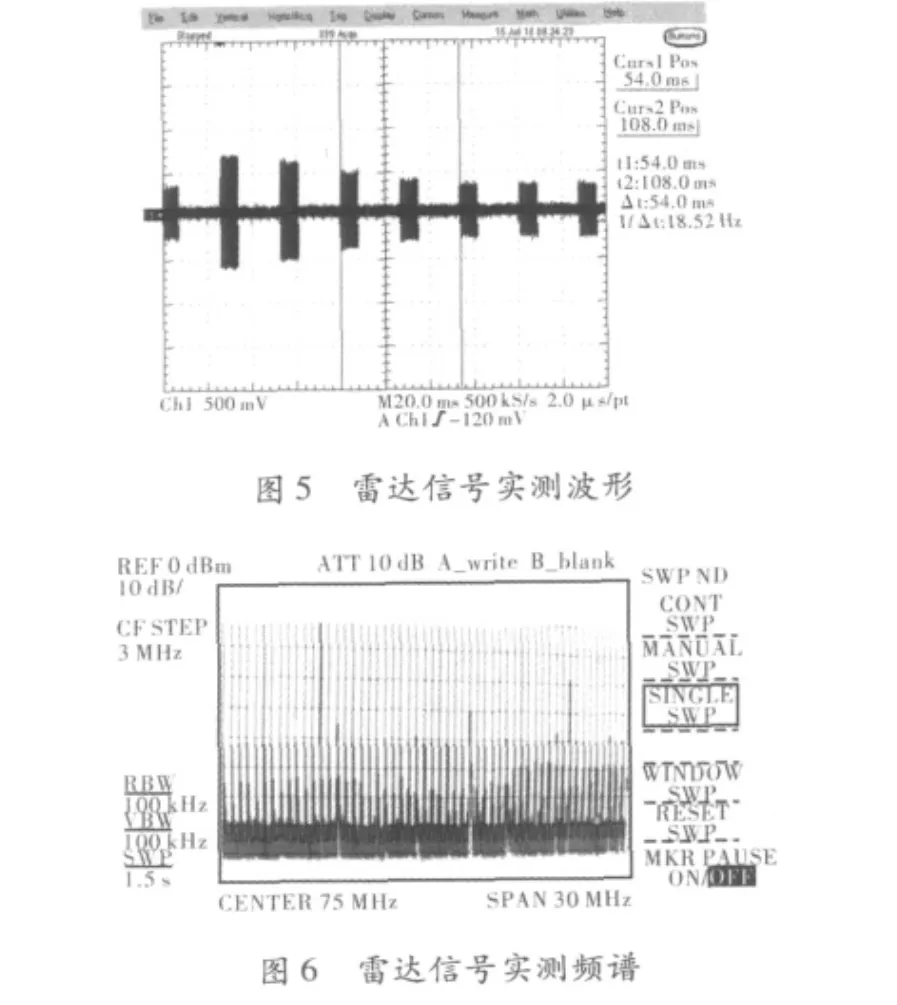

实验产生波形及频谱如图5,图6所示。

由图5和图6可以看出,产生的雷达信号脉冲间隔为27 ms,脉宽为8 ms,脉内采用正线性调频信号,其中心频率为75 MHz,带宽30 MHz,满足所需雷达信号的指标要求。

4 结束语

根据线性调频信号参数的特点,结合AD9910的功能特性,完成了雷达信号源发生器的设计方案。从实验结果看,该方案产生的雷达信号稳定度高、调制参数灵活、频谱干净,逼真地模拟了雷达信号。随着采样频率的不断提高,输出信号频谱的谐波杂散越来越小,DDS技术在雷达信号模拟方面将会取得广泛应用。

[1] 徐春香,刘军.基于FPGA的线性调频信号产生器设计[J].电子测试,2009(10):49-52.

[2] Analog Device Inc.AD9910 Datasheet[M].USA:Analog Device Inc,2007.

[3] 汪洋.基于DDS的脉压雷达信号的产生技术[D].西安:西安电子科技大学,2009.

[4] 詹俊鹏.基于DDS技术的雷达信号模拟器设计与实现[D].西安:西安电子科技大学,2009.

[5] 张茂春,刘恺.基于DDS技术的调频连续信号发生器设计[J].制导与引信,2010,31(2):16-17.

[6] 周云波.ICL8038扫频信号发生器[J].现代电子技术,2003(17):40-41,52.