基于DSP双路音频信号实时处理系统设计

袁茹轩,尉乐,何天璐,高中山

(西安电子科技大学本科生创新实践基地,陕西西安710126)

现代音频信号处理领域,通常需要采集大量的数据进行实时分析,并且逐步从处理单路信号发展为处理多路信号。对语音信号而言,采用元音强度与元音间隔作为听者识别信号的基础参数。另外音频信号处理的器件也从传统的模/数、数/模转换器发展成为多款高性能专用芯片。传统的数据采集系统以工控机或普通单片机为核心,整个系统体积大、功耗高,未考虑语音数据实时处理和发送。设计的实时语音处理系统具有数据量大、缓冲更新迅速、稳定性高、采集发送延时小等特点。该系统利用DSP进行数据处理,DMA与McBSP实现双路音频信号的实时并行采集发送,便于实验室进行数据分析、算法仿真和过优化处理流程等,也可用于个人便携式音频通信设备的驱动开发。

1 硬件概述

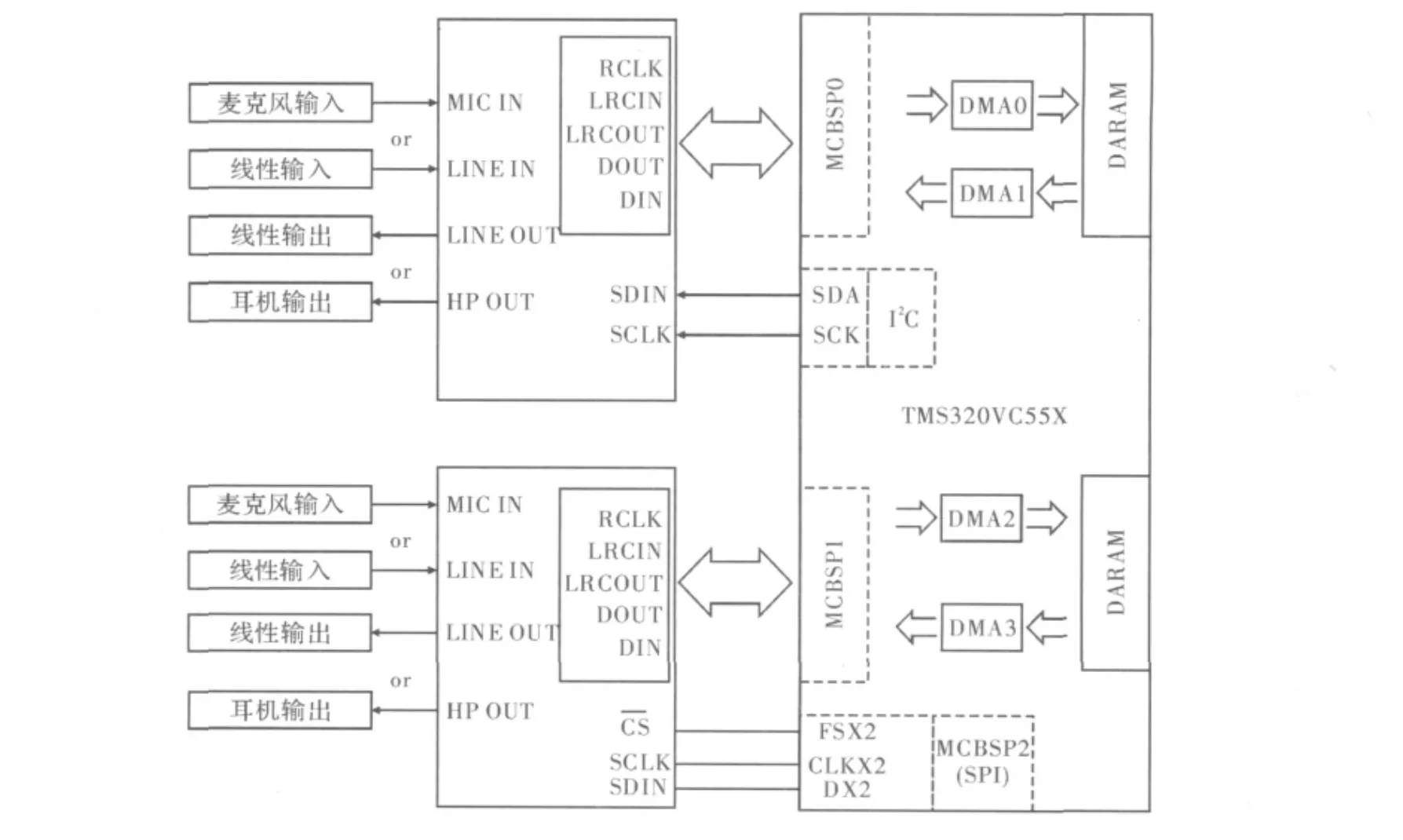

该系统采用美国TexasInstruments公司TMS320VC55X处理器,其继承了C54X系列的发展趋势,低功耗、低成本,在有限的功率条件下能够保持优良的性能。工作在0.9 V,其核的功率仅为0.05 W/MIPS,性能可达800 MIPS,对数字通信、语音处理等便携式应用提出的挑战提供了有效的解决方案[1]。以TMS320VC5509A为例,该芯片共有3个多通道缓冲串口,分别为McBSP0、McBSP1、McBSP2,每个串口接收和发送数据使用独立的时钟,支持连续传送,可直接与多媒体数字信号编码器的工业接口以及ADC/DAC接口实现无缝连接,通过CPU或DMA对16 bit寄存器访问实现通信,由DX引脚发送数据,RX引脚接收数据。通信时钟和帧同步有CLKX,CLKR,FSX以及FSR引脚来控制。TMS320VC5509A芯片提供6个通道DMA控制器,可独立于CPU完成4个标准接口的数据传输。每个通道可从一个数据源地址读取数据后写入另一个口或目标地址。特别指出5509芯片具有64 kB双访问RAM,其结构由8个4 kB×16位的块组成,允许两个端口同时访问,提高了系统速度[2]。

TLV320AIC23B是TI公司推出的一款高性能立体声音频编解码器,内置耳机输出放大器,支持MIC

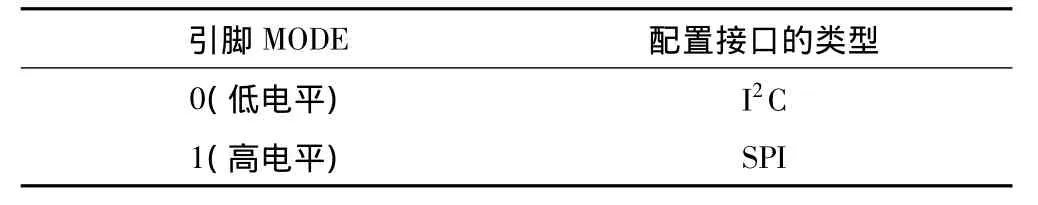

表1 SPI与I2C接口控制

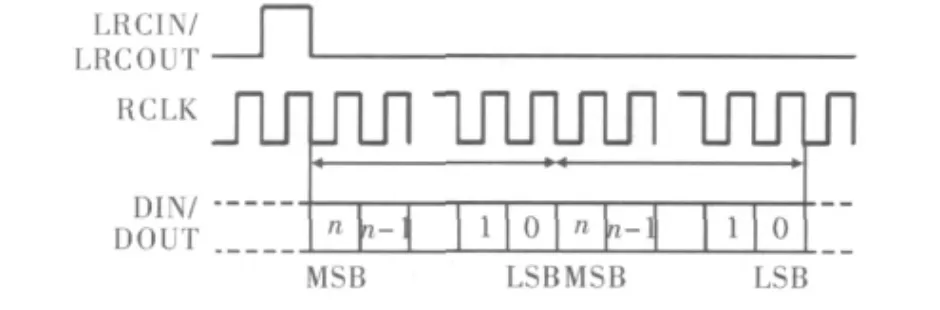

AIC23b数据传输格式支持右判断模式、左判断模式、I2C模式和DSP模式4种方式,其中DSP模式专门针对TI DSP设计。这两款芯片的I/O电压兼容,从而使得二者可以无缝连接,因此,基于DSP和音频Codec芯片AIC23B构建的硬件系统是一种理想的语音信号处理系统。在语音信号处理系统中,AIC23主频为12 MHz,A/D和D/A转换器的抽样频率为8 kHz[6],模拟音频信号由LINEIN/MICIN输入到该芯片,这些参数需要通过McBSP1对AIC23进行配置实现。模拟音频信号通过A/D转换、编码后,由数字音频接口传送给DSP的串口McBSP0,并接收DSP处理后的数据,收到的数字音频信号经解码、D/A转换后,从HEADPHO/LINEOUT输出[4]。本系统采用DSP模式,如图1所示。

图1 DSP模式时序

I2C总线协议是由Philips公司开发的两线式串行总线,用于连接微控制器及其外围设备,该协议已广泛地应用于数字通信系统硬件电路设计中。

AIC23B与微处理器的接口有两个,一个是控制口,用于设置AIC23B的工作参数,另一个是数据口,用于传输AIC23B的A/D、D/A数据。用I2C总线与AIC23B的控制口接口,对AIC23B的各个控制寄存器进行设置。McBSP的发送与接收时钟均由AIC23B提供。

在DMA应用中,可以赋予每个通道的bit流高低的优先级。每个DMA通道的同步事件为MCBSP串口收发事件,同时每个通道某个事件完成后可向CPU发送一个中断。用户可以编写代码修改寄存器配置,当DMA在进行数据传输时,只要用户使能该通道,就可将配置寄存器复制到工作寄存器中[5]。另外DMA支持自动初始化模式,可以在块传输过程中反复复制,连接示意图如图2所示。

图2 系统硬件接口原理图

2 软件系统设计

方案中两路麦克风输入数据,两路耳机输出数据。在此给出一路信号的接收处理发送过程,另一路信号设计思路相同。

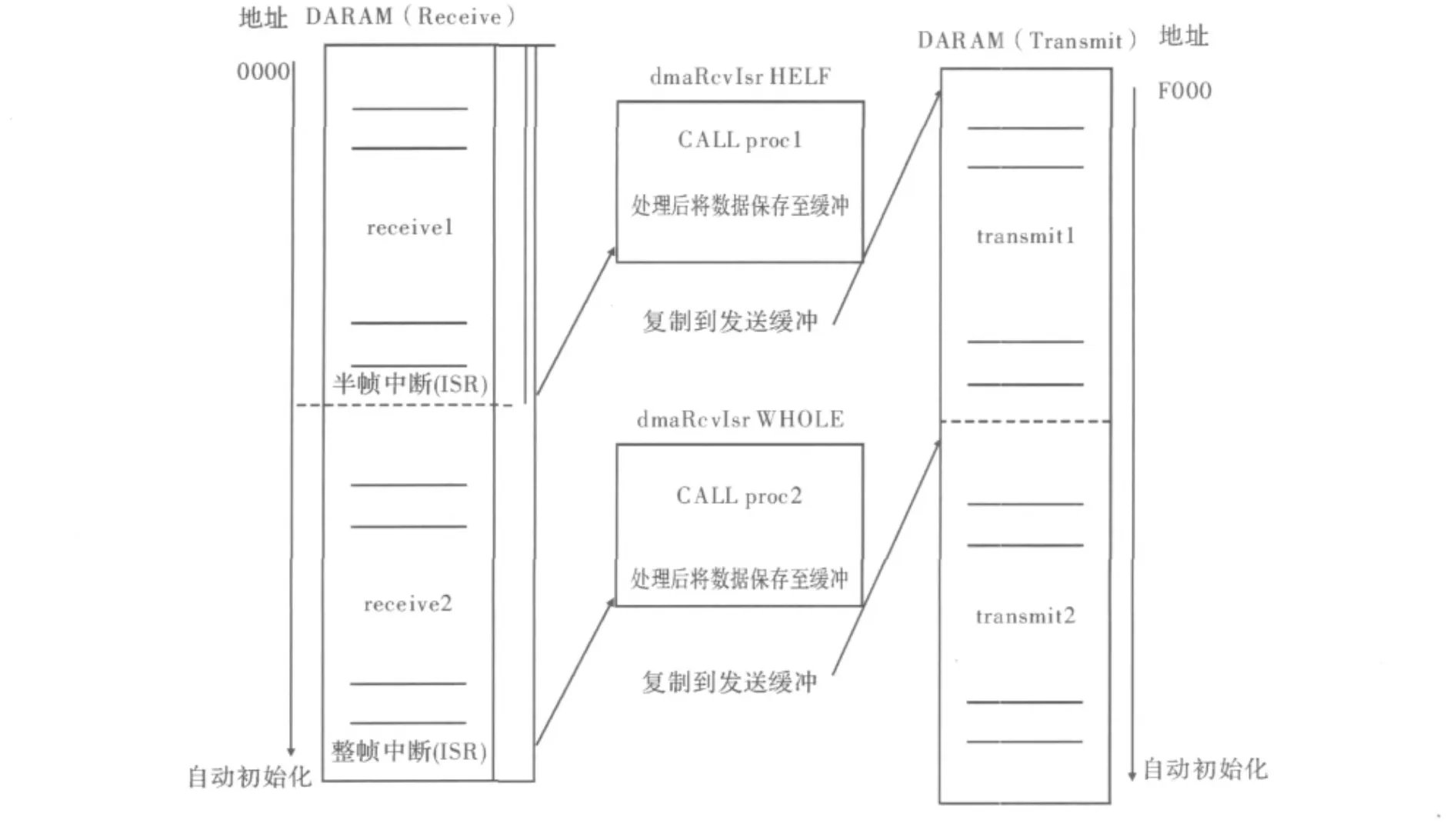

在DARAM中开辟缓冲和处理单元,数据传输均采用DMA独立于CPU的方式。CPU只有在接收DMA触发中断后对数据进行处理,并将处理后数据拷贝到DMA发送缓冲。为保证整个传输过程中无数据丢失,DMA接收端采用半帧中断的方式接收数据。在数据载入过程中,可以选择两个区域进行操作,将数据区分为receive1与receive2用于保存载入的数据,同时开辟程序运行区process1和process2用于运行程序。当receive区域触发半帧中断,CPU读取receive1中的数据并将其复制到process1中,调用处理函数proc1,在CPU进行相关信号处理时,DMA继续将数据载入receive2,其满时触发整帧中断,DMA自动初始化将receive1覆盖。CPU此时即可将receive2中的数据复制到process2中,调用处理函数proc2,这样receive区域交替更新,即可实现程序的不间断运行。

每次中断服务程序的运行时间必须小于半帧中断的间隔时间。此方案可以保证系统的延时足够小。在使用该方案时,用户必须根据自己的需要设计合适的采样频率和缓冲数据区的大小。为提高系统稳定性,实验可以根据要求设计中断的优先级。系统软件设计如图3所示。

图3 系统软件设计原理图

3 结束语

系统采用DSPVC5509作为核心处理器,充分利用了DSP片上资源,采用独立于CPU的DMA实现了数据的实时采集处理以及发送,降低了总线占用率。设计的可更新缓冲区不仅符合DMA传输要求而且避免了数据丢失,实时更新减少了数据空间的浪费。另外该系统具有低功耗、稳定性高的特点,可以根据用户需求进一步扩展。

[1] TI Conpration.TMS320VC5509 fixed-point digital signal processor data manual[M].Texas:TI Conpration,2001.

[2] 刘向宇.DSP嵌入式常用模块与综合系统设计[M].北京:电子工业出版社,2009.

[3] 丁玉美,高西全.数字信号处理[M].西安:西安电子科技大学出版社,2005.

[4] TI Conpration.Stereo Audio CODEC,8 to 96 kHz[M].Texas:TI Conpration,2001.

[5] 王念旭.DSP基础与应用系统设计[M].北京:北京航空航天大学出版社,2001.

[6] 尹勇,欧光军.DSP集成开发环境CCS开发指南[M].北京:北京航空航天大学出版社,2003.