基于SOPC的音膜内外边缘实时检测*

蔡浩聪 谢云 刘家晓 郑海成

(广东工业大学 自动化学院)

1 引言

基于可编程片上系统的SOPC技术是目前国内外电子领域中的研究热点,它将并行结构和并行计算集于一体,采用了软硬件协同设计和 IP复用的思想,能够减少产品开发时间,降低功耗,高效利用FPGA资源,因此可以实现高速低功耗低成本的实时嵌入式机器视觉检测系统。随着技术的不断进步,FPGA的集成度越来越高,可以实现的设计规模越来越大,而功耗越来越低。因此,基于FPGA的嵌入式视觉系统将是计算机视觉系统的重要发展方向[1]。

随着消费类电子产品的增多,各种小型的音响设备的需求也随之增多,音响设备的音质主要由扬声器的重要部件音膜决定,而音膜的质量主要由其内外圆的同心度决定,音膜的生产加工及质量检测便成为市场竞争中的重要因素。对音膜同心度的求取过程要解决的重点问题是对音膜内外圆边缘的在线实时检测。目前国内暂无成熟的音膜同心度机器视觉检测系统。

针对上述情况,本文采用SOPC、可编程逻辑器件、IP复用等技术,设计了一种基于SOPC的实时视觉检测系统。主要介绍了该系统中总体设计方案,并采用Sobel算子,以音膜的内外圆边缘检测为例,证明了该系统的高速实时性。本设计不仅带来一定的实用价值,也为高速智能相机的开发提供了有用的参考。

2 系统整体设计

2.1 系统硬件结构

SOPC技术是将CPU、存储器、I/O接口等系统设计所必须的模块封装为IP核集成在一片FPGA上,是一种新的系统设计技术。这种设计方式,有开发周期短、设计灵活、可裁减、可扩充、可升级、软硬件在系统可编程的功能,特别适用于复杂系统的设计[2]。由于SOPC技术的诸多优点,本文采用这种技术设计了一种基于SOPC的嵌入式视觉检测系统。系统总体框图如图1所示。

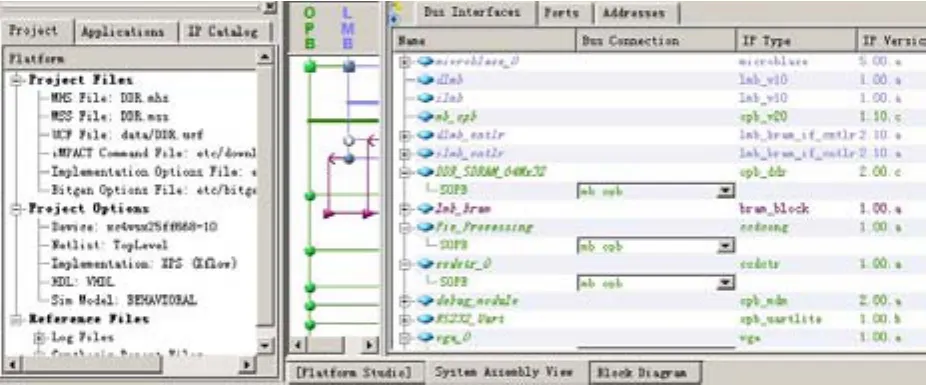

本系统采用了北京合众达公司的教学实验平台SEED-XDTK-V4为硬件开发平台和Xilinx公司的嵌入式开发工具 EDK 为软件开发平台。SEED-XDTK-V4实验箱配置了Xilinx公司的Virtex-4系列的FPGA芯片,该芯片拥有23040个逻辑单元和128 个信号处理单元(Xtreme DSP Slices)等丰富资源。EDK开发套件自带了许多工具和IP,可以用来设计完整的嵌入式处理器系统,主要包括Xilinx平台工作室XPS和软件开发套件SDK。本系统工程包括了 MicroBlaze软核处理器、OPB总线、DDR 控制器、DMA控制器、图像处理算法模块等。MicroBlaze软核是一种针对 Xilinx FPGA 器件而优化的功能强大的32位微处理器,支持CoreConnect总线的标准外设集合,具有较好的兼容性和重复利用性。各外设模块以IP核形式灵活的连接到OPB总线上,使系统的设计具有很好的重构能力和灵活性。系统的SOPC工程如图2所示。主要IP核的功能简单介绍如下:

UART模块:I2C 配置视频解码芯片TVP5150PBS工作模式;

DMA模块:内存与外设之间进行批量的数据传输。使用DMA控制器对图像数据的存储进行操作,这样可减少CPU的处理负担和功耗,提高图像处理速度;

CCD_Controllor模块:采集视频解码芯片TVP5150PBS解码后的视频数据,并进行图像格式转换。其中配置了TVP5150PBS为YUV格式输出,“Y”表示明亮度(Luminance),也就是灰阶值;“U”和“V”表示色度(Chrominance)。通过图像数据采集模块将接收到的YUV图像转换为8位灰度图像格式,将3个像素点共24位数据合并为32位数据(高8位补零),然后送OPB总线,因此,每一次总线传输相当于传输了3个像素的数据。这里不采用一次传输4个像素点的灰度数据的原因是:3个像素数据的传输有利于后面图像处理算法的实现;

PLC_Ctr模块:用于与外设 PLC 进行通信,控制 PLC进行相应的操作,例如控制外部传感器,启动剔除装置剔除流水线上不合格的产品等;

VGA模块:产生数字图像输出对应的时序,若图像数据未经MicroBlaze CPU处理,则直接数据流输出;若图像数据经CPU处理,则使用乒乓操作的方式,将图像数据转换为27MHz输出;

Pic_Processing模块:数字图像处理算法的实现。该模块可根据项目的具体要求设计相应的图像处理算法IP核,该图像处理 IP核既可以完全使用硬件设计方式完成整个图像处理过程,直接输出显示最终结果,也可以只完成图像的前期预处理部分,然后把处理后的关键数据送入MicroBlaze软核 CPU中,通过软件处理方式得到最终的处理结果再进行VGA输出显示。因此该模块的设计是项目设计的重点和难点。下面将以音膜图像的内外圆轮廓检测为例,具体介绍该模块IP的设计流程和实现方法。

图2 EDK中SOPC工程

2.2 系统的软件设计

由于系统中采用了DMA传输技术,图像处理算法完全由硬件实现,因此MicroBlaze CPU主要完成了系统的初始化、外设的配置和DMA的控制等简单操作。软件设计流程如图3所示。

图3 系统软件设计流程

3 音膜内外圆边缘检测算法IP

3.1 算法原理

该应用中的数字图像处理算法的主要思路是:读取音膜图像数据到图像处理模块IP,进行数据缓存,再进行中值滤波处理,滤除干扰噪声,接着运用Sobel算子对音膜图像进行内外圆边缘检测,然后对图像进行二值化处理。由于边缘检测算法的数据量较大,为达到实时处理的要求,本文采用了算法全硬件实现的设计方法。

3.2 Sobel算子介绍

Sobel算子是测量沿水平方向和垂直方向两个方向的灰度差,然后把测量值合并起来形成边缘强度。Sobel的水平方向梯度算子和垂直方向梯度算子分别如图4(a)和图4(b)所示,图4(c) 为图像的3×3区域(Z为8位灰度值)[3]。

图4 Sobel算子和图像3×3区域

得到Sobel算子的梯度的模的近似表达式为:

判断梯度模的值是否大于或等于设定的阈值T,若是则置该点为灰度值255,反之置0,即:

3.3 Sobel算子的硬件实现方法

Sobel算子的硬件实现使用了Xilinx公司的高性能 DSP系统的快速建模和实现工具 System Generator。该工具是Xilinx公司的系统级建模工具,在很多方面扩展了MathWorks公司的Simulink平台,提供了合适硬件设计的数字信号处理(DSP)建模环境,加速、简化了FPGA的DSP系统级硬件设计[4]。图5为在Simulink中使用System Generator工具搭建起的Sobel算子模型。输入图像数据通过水平方向和垂直方向两个滤波器后,再把两个滤波器输出的值进行相加,然后再通过阈值T相比,进行二值化,输出最终结果。整个Sobel算子使用了11个加减法器和一个双口随机存取存储器(Dual Port RAM)等资源。整个设计思路严格按照Sobel的算法步骤进行设计。

图5 Sobel算子模型

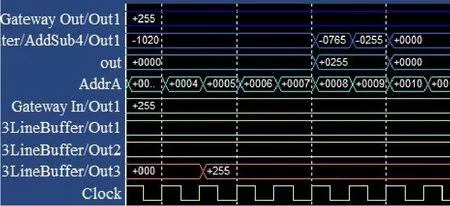

在 Sobel算子模型上加入中值滤波和二值化模块,使用 System Generator软件将算法模型转化为HDL工程,进行优化和综合,通过Modelsim仿真验证算法的正确性,仿真结果如图6所示。

图6 Modelsim中算法仿真结果

在EDK软件中,通过编写自定义IP中的MPD文件、PAO文件和用户逻辑(user_logic)模块,通过编写端口转换和时序调节程序,将图像算法模块封装成IP核,挂接到OPB总线上,配合一定的控制时序,通过MicroBlaze软核的软件程序调用该IP核模块,完成整个系统的运行。

4 实验及结果分析

图7 PC和FPGA检测结果

图7(a)为音膜的原图像,图7(b)为PC上在VC++软件中使用Sobel算子检测得到的音膜内外圆轮廓,图7(c)为基于FPGA上检测得到的结果。由两图对比可得,PC上检测得到的轮廓比较纤细,在边缘出现断裂,需要进一步的圆拟合,并且PC检测的噪声较大,而FPGA检测得到的轮廓明显,且无断裂部分。

由于PC和SOPC的图像采集时间和显示时间相差不大,因此对比PC系统和SOPC系统的处理速度快慢,主要是对比数字图像处理模块的处理时间。SOPC系统中图像处理模块在Modelsim中的仿真时间计算公式为:仿真时间=一个仿真周期时间*仿真周期数。仿真中设置了一个仿真周期时间为20ns,即系统频率为50MHz。得到音膜图片使用基于Sobel算子的图像处理算法分别在VC++平台上和FPGA平台上的处理时间,如表1所示。可见在FPGA上实现图像处理算法其处理速度比PC高出约22倍,可以实现高速在线实时检测。

表1 PC和FPGA上音膜内外圆边缘检测时间(单位:ms)

5 结论

本文以30mm以下的黑色音膜为研究对象,利用SOPC技术,设计了一种实时检测系统。采用了FPGA并行处理和软硬件协同设计,使系统具有实时性、可重构性强、体积小、低功耗低成本等优点。实验结果表明,基于SOPC的音膜内外圆边缘检测系统功耗低,运行稳定,检测速度快,可实现音膜的在线实时检测,解决了流水生产线上产品无法进行实时检测的关键问题。

[1]原魁,肖晗等.采用 FPGA 的机器视觉系统发展现状与趋势[J].计算机工程与应用,2010,46(36):1-5.

[2]黄云,杨尊先.基于 SOPC的数据采集与处理系统设计[J].电子器件,2010,33(1):68-70.

[3]李明,赵勋杰,毛伟民.Sobel边缘检测的 FPGA 实现[J].现代电子技术,2009,16:44-46.

[4]高展宏,王强.多媒体处理FPGA实现—System Generator篇[M].北京:电子工业出版社,2010:71-72.

[5]Babu T Chacko, Siddharth Shelly. Real-Time Video Filtering and Overlay Character .Generation on FPGA. 2010 International Conference on Recent Trends in Information,Telecommunication and Computing,2010,26:184-188.

[6]XILINX. Xilinx System Generator Manual[S]. 2008.