MEMS圆片级真空封装金硅键合工艺研究*

张 卓,汪学方,王宇哲,刘 川,刘 胜

(1. 华中科技大学机械科学与工程学院,武汉 430074;2. 华中科技大学能源与动力工程学院,武汉 430074;3. 华中科技大学光电国家实验室,武汉 430074)

1 引言

微机电系统(Micro Electro Mechanical System)是将微机械元件、微型传感器、微型执行器、信号处理与控制电路等集成于一体的微系统,是随着半导体集成电路、微细加工技术和超精密机械加工技术的发展而发展起来的[1]。许多MEMS器件,如陀螺仪、加速度传感器和谐振器等都需要采用真空封装以降低机械运动部件运动时气体的阻尼,极大地提高器件的品质,从而提高器件的性能。键合技术是一种将MEMS器件中不同材料的部件永久连结为一体的技术。近年来键合技术发展迅速,已成为MEMS器件开发和实用化的关键技术之一。而常用的真空键合技术主要是高真空(< 10-2Pa)环境下的阳极键合、共晶键合以及硅-硅直接键合等。阳极键合一般只限于硅-玻璃键合[2],键合温度为300℃~400℃,偏压为500V~1000V,键合过程中的高电压对微电路有影响,而使其应用受到极大限制;硅-硅直接键合[3]是指两片抛光硅片在不需要任何粘接剂和外加电场的条件下直接键合在一起,其缺点是温度太高(高于800℃);而共晶键合是利用某些共晶合金熔融温度较低的特点,将它们作为中间介质层,在较低温度下,通过加热熔融实现共晶键合。相对来讲,共晶键合的限制因素较少,可以选择的材料和工艺参数范围较大。选择Au/Si共晶键合方式是由于Au/Si共晶键合液相粘结性好,键合强度高,且键合温度要求不高,对界面的粗糙度不很敏感,并且避免了键合过程中低熔点金属(如Sn)存在的流动性问题。

2 试验

Au/Si共晶键合[4]是利用Au/Si共晶合金熔融温度较低(363℃,比纯金或纯硅熔点低得多)的特点,将它作为中间介质层,在较低的温度下通过加热熔融实现共晶键合。本文中键合工艺需要达到以下要求:(1)键合温度不可过高,保证键合过程中需要保护的器件不会受到损伤;(2)键合过程中不破坏腔体内的结构;(3)保证键合在高真空下(< 10-2Pa)进行,且键合完成后每个芯片的泄漏率达到应用要求;(4)保证一定的键合强度,保证管芯在划片、测试和使用过程中能对腔体内的结构提供很好的机械保护。

本文用作键合的两片硅圆片采用P型100硅片,单面抛光,电阻率为0.3Ω·μm ~0.5Ω·μm。作为盖帽的圆片厚度510 μm,作为基底的圆片厚度380 μ m。键合具体工艺流程如下:

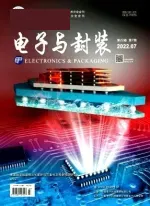

(1)盖帽片清洗(去除颗粒沾污、金属杂质和表面有机物);(2)热氧化,厚度为1.6μm;(3)正反面分别涂覆光刻胶;(4)正面曝光、显影并用BOE溶液刻蚀出待腐蚀窗口(窗口为6.4mm×6.4mm大小的正方形);(5)去除残留光刻胶;(6)湿法腐蚀:将盖帽片置于20%~25% KOH溶液(75℃~80℃)中3h,腐蚀出槽的深度为110μm ~130μm;(7)用BOE溶液去除残留SiO2;(8)磁控溅射Ti/Au,厚度分别为50nm和500nm;(9)将制作完成的盖帽与基底完成键合。

图1 键合工艺流程

对于键合试验中键合区域的宽度,我们设置了3组对比参数:0.2mm、0.4mm和1.6mm。键合工艺采用SUSS MicroTec公司的BA-6键合机,键合的温度-时间曲线如图2所示。开始阶段抽真空的同时升温至50℃,待键合腔体内抽真空至10-2Pa左右时,升温至363℃,保温10min,再加热至440℃,保温30min,同时给键合的两片圆片施加300kPa的压力。接下来降温至300℃,退火30min。最后阶段放气,使腔体内气压回复至常压,温度同时回复至常温。

图2 键合温度-时间曲线

通过上述工艺,成功将3对样品键合。键合完成后将样品在Sonoscan公司的D9500超声扫描仪(CSAM)上观察键合情况。超声扫描仪的原理是利用不同材料对超声波声阻抗不同、对声波的吸收和反射程度不同,来探测半导体、元器件的结构、缺陷,对材料做定性分析。键合样片在超声扫描仪下观测图片如图3所示(从左至右样品键合区域宽度分别为1.6mm、0.4mm、0.2mm),从整体上看键合质量良好,但局部仍然存在一些缺陷。

图3 键合样片在超声显微镜下的图像

3 性能检测

3.1 泄漏率检测

泄漏率的检测主要由He质谱仪细检[5]和氟油粗检完成。He质谱仪采用的示踪气体为氦气,采用质谱仪的方法对示踪气体的浓度进行检测。利用He质谱仪检漏仪加压法测量泄漏时,通常按照MIL-STD-883E的标准要求把待测封闭腔体放置在2~7.5个大气压的He气环境下2h~24h[6],如果存在泄漏,氦气会漏入待测封闭腔体内,然后把待测的密闭腔体放置到He质谱仪的检测腔体内,抽真空到 2.7×10-2Pa左右,这时如果存在泄漏,氦气就会从待测密闭腔体内泄漏出来,用质谱仪检测泄漏的He浓度。从泄漏的示踪气体He的浓度可以计算出漏孔泄漏的漏率。将3组样品在压强为0.4MPa的氦气中保压2h后进行漏率测量,测得键合区域宽度分别为0.2mm、0.4mm、1.6mm的三组样品(分别编号A、B、C)泄漏率均在2×10-8~5×10-8Pa·m3/s之间。

细检合格的全部样品进入下一步的氟油粗检。将每组在精检中合格的样品放入氟油中,观测是否有气泡产生。A组样品在氟油粗检中有90%的样品观察到了气泡的产生,判定为失效,故合格率仅为10%;B组样品在氟油粗检中的合格率为15%;C组样品在氟油粗检中的合格率为60%。统计键合缺陷区域的比例时发现,所有泄露样品中,键合缺陷区域位于四个角上和四个边上所占比例分别为42.2%和57.8%。可见四个边角上出现键合缺陷的情况较多。

3.2 键合强度检测

本文中选用直拉法检测键合片的强度。直拉法[7]是用拉开键合片的最大拉力来表示键合强度的。测试中所使用拉伸试验测试台为实验室自行研制和装配。测试之前需将样品通过粘结剂粘到拉伸样品夹具并固化24h以上以保证其粘合效果。接下来将粘合好样品的拉伸样品装夹在拉伸台上,加载直至样品断裂。

每组选取15个样品进行拉伸试验。测得的结果为:A、B、C三组平均最大拉伸力分别为39.62N、73.99N和248.40N。由于键合区域面积可知,可以算出三组样品单位面积的键合强度分别为15.24MPa、14.01MPa、10.76MPa。可以看出键合区域面积的增加对键合强度增大的影响比较显著,这是因为键合区域分布在整个圆片上而存在一定的不平整,致使局部键合质量受到影响的缘故。

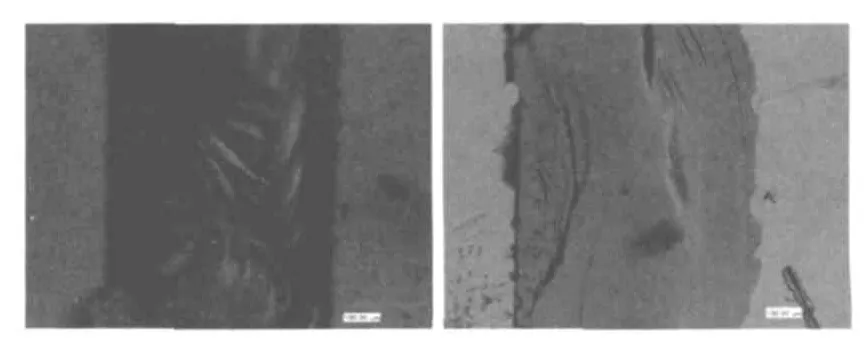

图4为键合样品在拉伸试验后断面在金相显微镜下的图片,观察3组拉伸样品键合区域的断裂表面,均可观察到硅表面裂开的现象,这表明局部区域金硅键合强度已经超过了单晶硅本身的强度。

图4 键合样品拉伸断面显微镜照片(500倍)

4 结论

本文对圆片级MEMS真空封装金硅键合工艺进行了初步的研究,通过对键合工艺的选择和优化、键合质量的分析、键合强度和气密性的检测,得出以下结论:

(1)金硅键合的优点是其液相粘结性好、键合强度高、键合温度较低,且可以避免焊料键合中熔点较低的金属(如Sn)存在焊料流动从而影响键合腔体内结构的现象。

(2)经过大量参数试验,得到圆片级金硅键合的理想条件为:溅射Ti厚度50nm左右,Au厚度500nm左右,键合温度430℃左右,键合时间30min,键合时所施加压力300kPa左右。

(3)对于圆片级金硅键合,由于在大面积的键合中整个圆片存在着一定的高度差,因此键合之前圆片上所沉积金的厚度应该尽量大。但是考虑到成本和溅射的工艺限制,选择沉积金的厚度为500nm。

(4)由3组键合区域宽度不同的试验数据对比可以看出,键合的结构(尤其是键合区域面积的大小)与键合质量(泄漏率、键合强度)有着很密切的关系。键合区域面积过小时,腔体的真空度对键合区域出现缺陷的容忍度较差,成品率较低。键合区域宽度增大到1mm以上时,键合成品率可以提升到50%以上。

(5)氟油检测中发现四个边角上发生泄露的现象比较多,分析其原因,是由于在进行湿法腐蚀工艺时各项异性腐蚀导致边角上出现向内过刻的现象(见图5),这样角上区域的面积变小,这也是导致角上出现泄露的原因之一。之后可以通过修改键合区域图形来改进这个问题,从而提高键合的合格率。

图5 键合样品角上出现的过刻现象

[1]张东梅,叶枝灿,丁桂甫,等.用于MEMS器件的键合工艺研究进展[J]. 电子工艺技术,2005,26(6):678-683.

[2]Jung-tang Huang, Hsueh-an Yang. Improvement of bonding time and quality of anodic bonding using the spiral arrangement of multiple point electrodes[J]. Sensors and Actuators A, 2002,102 (1 - 2) : 1-5.

[3]J.B.Lasky,Stiffler.S.R.,White.F.R,et al..Silicon-on-insulator by bonding and etch back[C].Proc.Int.Electron Device Meeting,USE,1985. 684-687.

[4]Liu Bing-wu, Zhang Zhao-hua, Tan Zhi-min,et al..Au-Si eutectic bonding technology for MEMS device. 2006,31(12): 896-899.

[5]甘志银. MEMS器件真空封装的研究[D].华中科技大学博士学位论文,2008:87-95.

[6]MSD.Test Method Standard Mieroeireuits.USA[S].MILSTD,1998.MIL-STD-883Evol.Au-Si eutectic bonding technology for MEMS device.

[7]Takao Abe, Tokio Takei, Atsuo Uchiyama , et al..Silicon wafer bonding mechanism for silicon-on-insulator structures[J] .Jap J Appl Phys,1990,29 (12) :2311-2314.