深亚微米工艺下系统芯片低功耗技术

王 栋,蔡 荭

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

1 引言

随着集成电路工艺技术迅速发展,单个芯片的规模已经发展到几十亿个晶体管。随着芯片规模的进一步扩大,功耗问题正在变得日益突出,并成为制约未来集成电路发展的十分关键的因素之一。功耗估计及低功耗系统设计工作已经在集成电路工艺制造、设计以及软件系统设计等层次全面开展。在动态和静态功耗的建模及优化方面都有大量的研究在进行探索,但其速度还远远跟不上以指数形式增长的功耗提高速度,特别是在静态功耗的快速估计和优化、面向片上系统的低功耗设计技术、面向特定应用的低功耗系统设计等方面。本文从不同的角度对超大规模集成电路存在的低功耗问题进行分析,并提出一些解决措施。

集成电路的功耗一般分为动态功耗和静态功耗两大部分。动态功耗是在电路工作状态发生变化时产生的,主要包括三个部分:由于逻辑跳变引起的电容功耗、由于通路延时引起的竞争冒险功耗、由于电路瞬间导通引起的短路功耗,动态功耗曾经是电路总功耗的主要部分[1]。

静态功耗是电路处于非活动状态时电路的功耗。当电路工艺进入深亚微米或者更深的纳米阶段后,漏电流带来的静态功耗占很重要的部分,并且其增长速度比动态功耗快得多。漏电流主要包括三个部分:亚阈漏电流、栅极漏电流、源漏级反偏漏电流[2]。主要原因是栅氧化层厚度按比例减小导致栅氧化层内的电场强度增大,产生较为明显的栅氧隧穿泄漏电路,加上漏极与衬底之间的反偏PN结电流等,使得泄漏功耗成为总功耗的重要组成部分。一般来说,影响泄漏电流大小的因素包括阈值电压、沟道的物理尺寸、沟道/表面的注入工艺、漏极/源极的结深度、栅氧化层的厚度和供电电压等,到纳米时代,泄漏功耗占总功耗50%左右[3]。

目前SoC 低功耗设计技术的研究主要集中在两个方面[4-5]:低功耗电路设计和低功耗EDA 软件研究。低功耗电路设计的研究和其本身的产品方向有着密切关系,拥有生产线的厂商主要集中在生产工艺方面(如LSI Logic TSMC等),EDA供应商则主要集中在低功耗软件研究方面(如Synopsys Mentor等),而一些大型处理器设计公司则比较关注SoC各个层次的设计技术和低功耗处理器模型的研究(如ARM、IBM和NEC等),低功耗EDA 软件的研究主要集中在功耗建模、功耗分析和功耗优化三个方面,国外各大学对低功耗技术的研究比较全面,但每个大学进行的侧重点不同,有的侧重低功耗处理器的研究,有的侧重进行低功耗综合技术的研究,另外一些则从事异步电路的研究。国内对低功耗技术的研究还处于发展阶段,虽然也有一些专门的低功耗研究机构如中科院,但目前开展的一些工作主要集中在工艺研究和功耗建模方面,SoC软件低功耗设计技术的研究较少,硬件低功耗设计技术也有待进一步完善和提高。

2 低功耗技术的实现

低功耗设计技术贯穿算法/系统级到版图/电路级的整个设计过程。在设计早期通过有效的分析、验证和优化技术发现并解决问题,使功耗等技术指标满足设计规范,然后进入下一阶段。

设计证明不同设计层次对功耗的改善程度是不同的,层次越高,改善的程度越大[4]。表1给出在各个不同硬件层次上可采用的低功耗设计技术以及这些低功耗设计技术对降低系统整体功耗的影响。

表1 不同层次低功耗设计技术及其效果

以我们设计的一款系统芯片为例,该系统芯片的架构如图1所示,其规模超过200万门,内嵌一个32位微处理器、一些通用的接口模块、128kB存储器模块、中断模块、功耗管理模块以及用户IP模块。

图1 系统芯片架构

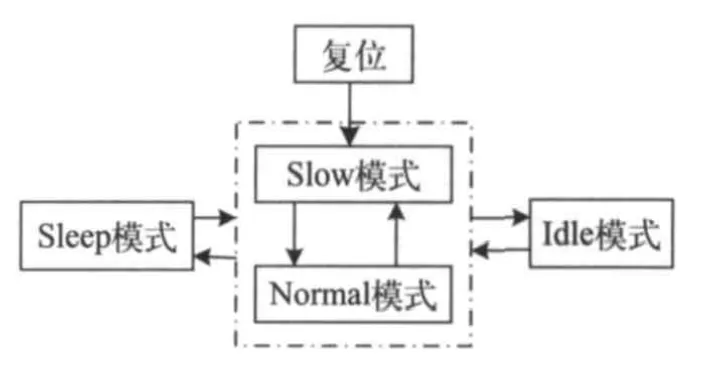

图2 芯片的工作模式

(1)系统级(system level)基本思想是在部分模块进入空闲状态后立即关闭(shut down),主要研究如何进行系统划分和状态预测。

在具体设计中,对芯片工作状态进行合理的设计,大致分为四种工作模式:Slow模式;Idle模式;Sleep模式和正常(Normal)工作模式。当系统复位完成或系统只需要低频下工作时(测试模式下),芯片可以在Slow模式;如果处理器结束所有工作,系统将进入很长的等待时间,此时芯片就会进入Idle模式,该模式下,CPU被关闭,所有任务都处于挂起或停止状态,但大多数的外设仍处于活动状态,该状态是外设工作、CPU不工作的低功耗模式。

Sleep模式下将关闭CPU核和所有模块的时钟源,仅给重要的内部电路供电,所以功耗最低。虽然可以从Slow模式或Normal模式切换到Sleep模式,但是当它退出Sleep模式时,系统只能回到Slow模式。

Nomal模式下系统中所有模块的时钟源都来自于时钟模块,该模式下,CPU和所有的外设都处在上电状态,系统满负荷运行,功耗最大。当然在这种模式下也可以根据系统的应用要求关闭某些模块。如果系统需要调整时钟频率,可以通过动态配置时钟电路来实现。

唤醒机制是为了帮助系统从Idle模式或Sleep模式中恢复出来,建立完整、有效的唤醒机制是必须的。有三种方式可以让系统从低功耗模式中唤醒。第一,通过内部所有模块的中断信号,可以让系统回到进入Idle之前的状态;第二,内部Watchdog reset信号使系统回到Slow状态;第三,外部输入中断信号可以使系统恢复到低功耗之前的工作状态。

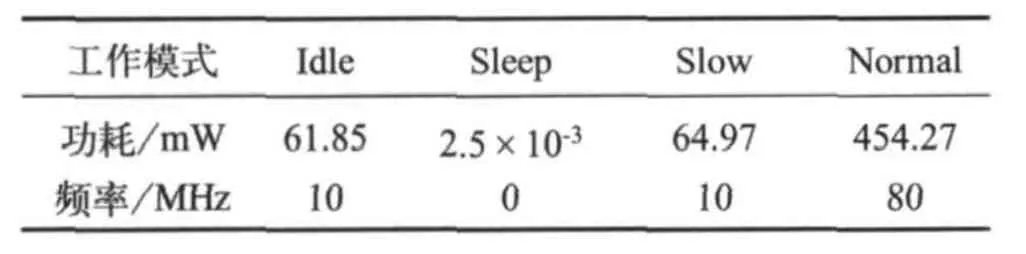

在进行程序开发时,为配合硬件进行低功耗设计,要充分利用电源管理机制,在电路不同工作模式切换过程中强调应用程序与其配合,减少系统的功耗。芯片上功耗管理模块具有动态控制整个芯片功耗的功能。仿真显示各个模式下的功耗如表2所示。

表2 不同模式下的功耗情况

(2)算法级(Algorithm Level)通过选择适当的算法表述减少跳变率,基本思想还是集中在通过软、硬件的合理划分来降低电路功耗[5]。

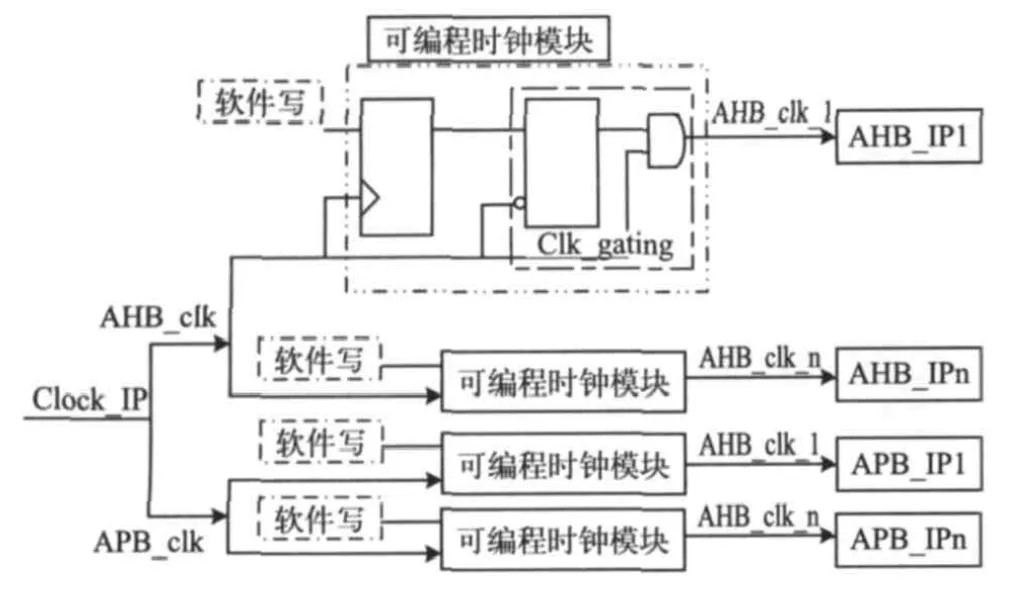

图3 可编程模块的控制

SoC工作时对内部IP模块的要求也不一样,在不同的时刻IP可以处在不同的工作状态,这样可以根据实际工作需要对IP模块进行合理的管理,控制整个芯片的功耗。为此我们提出图3 所示的一个时钟动态管理策略:每个外设时钟都有一组使能信号进行控制,当某个IP模块不工作时,用户可以通过软件对可编程IP时钟单元进行编程,当写入“0”时,该模块输入时钟就会停止工作;当写入“1”时,该模块就会重新工作。

(3)寄存器传输级(Register Transfer Level)主要有门控时钟(clocking gating)、有限状态机编码优化、通路平衡、总线编码优化等方法。

门控时钟可以在设计流程中实现自动化,减少工作量。其中寄存器替换是Synopsys的Power Compiler主要方法,它是将设计中的寄存器替换成带有门控时钟“使能”端的寄存器。对下面的一段代码(a)修改为代码(b),利用EDA工具在设计的逻辑综合阶段加入门控时钟综合脚本,可以综合出带有门控时钟的寄存器。

(a)

Module FFEN(ena,d,clk,q)

input ena, d, clk;

output q;

reg q;

always @(posedge clk )

begin

if(ena)

q <= d;

end

endmodule

(b)

Module G_FFEN(ena, d, clk,q)

input ena,d, clk;

output q;

reg q,g_clk;

always @(posedge g_clk)

begin

q<=d;

end

always @(clk or ena)

begin

if(!clk)

I_ena <= ena;

end

assign g_clk = I_ena &clk;

endmodule

利用综合工具Design Compiler,将实现在电路插入门控时钟,通过脚本灵活实现:

/*设置门控时钟设计常用的变量*/

Set power_preserve_rtl_hier_names true

Set hdlin_no_group_register true

/*设定门控时钟类型及相关参数*/

Set_clock_gating_style –sequential_cell latch –setup 0.2 –hold 0.1 –control_point before –control_signal scan_enable –minimum_bitwidth 2 –max_fanout 6

/*读入RTL代码,插入门控时钟*/

Analyze –fanout verilog –lib library_name –define SYNOPSIS

/*确定控制信号是否采用门控时钟*/

Set_clock_gating_signals –design design_name

Elaborate design_name –gate_clock –update –lib liabrary_name

/*将所涉及到的控制点信号连接到一起*/

Hookup_testports -verbose

/*插入门控时钟的报告*/

Report_clock_gating –gating_elements –gated –ungated –hier

/*插入门控时钟后的时钟定义与约束*/

Set CLK_PER 10

Set UNCERTAINTY 0.12

Set INSERTION_DELAY 0.2

Create_clock –period $ CLK_PER –name CLK[get_ports clk_power]

Create_clock –period $ CLK_PER –name POST_CG_CLK [get_pins –hierarchical “*clk_gate”/ENCLK]

Create_clock –period $ CLK_PER –name PRE_CG_CLK [get_pins –hierarchical “*clk_gate”/CLK]

Set_clock_latency $INSERTION_DELAY [get_clocks{CLK POST_CG_CLK}]

Source –e –v top_constraints.tcl

Propagate_constrains –gate_clock

Uniquify compile

采用SMIC 0.18μm CMOS工艺,目标工作频率100MHz。物理设计完成后最终的功耗分析结果见表3。分析结果表明,在不改变RTL代码的情况下,有效使用EDA工具进行门控时钟的插入可以使得电路功耗明显降低。

表3 由Power Compiler产生的功耗报告

3 结论

本文分析深亚微米工艺下系统芯片功耗的组成,并以实际设计的芯片为例,分别从不同层次(系统级/算法、寄存器级以及逻辑门级)采取低功耗优化方法进行设计,给出实际设计结果,这些方法的综合应用可以显著地降低芯片的功耗,同时也验证了功耗设计策略。

[1]Benini L,Bogliolo A,Micheli G,D. A survey of design techniques for system-level dynamic power management[J].IEEE Transactions on VLSI Systems, 2000,8(3):299-31.

[2]Xu,Y.,et al. Minimum leakage pattern generation using stack effect[C]. ASIC, 2003, Proceedings. 5th International Conference. 2003.

[3]Abdollahi, A.,F.Fallah, M.Pedram. Leakage current reduction in CMOS VLSI circuits by input vector control[J].VLSI Systems. IEEE Transactions,2004,12(2):140-154.

[4]Anand R, Niraj K J, Sujit D. High-level power analysis and optimization[M]. Boston, Kluwer Academic Publishers,2004.11-73.

[5]Lekatsas H, Henkel J,Wolf W. Arithmetic Coding for Low Power Embedded System Design[A]. Data Compression Conference (DCC’00),Snowbird, Utah,2000.430-439.