高速ADC时钟抖动及其影响的研究

胡智宏,廖旎焕

(1.郑州轻工业学院 电气工程学院,河南 郑州 450002;2.华北水利水电学院 电力学院,河南 郑州 450010)

高速ADC时钟抖动及其影响的研究

胡智宏1,廖旎焕2

(1.郑州轻工业学院 电气工程学院,河南 郑州 450002;2.华北水利水电学院 电力学院,河南 郑州 450010)

从ADC的输入信号及时钟源的自身参数着手,主要分析了输入信号幅值、频率、采样频率对时钟抖动及ADC信噪比的影响,根据ADC手册数据提供的信息给出了时钟抖动的计算方法,并对计算结果和实际测量结果进行分析比较,进一步提出了减少时钟抖动方法。

时钟抖动;SNR;频率

随着信息产业的快速发展,对A/D、D/A的性能要求越来越高。目前,针对高速、高精度ADC的研究很活跃。采样时钟是ADC变换电路的基本要素,对电路设计者来讲,ADC时钟电路采用的时钟方案、时钟类型、时钟电压等级、时钟抖动都是在实际电路设计时必须予以考虑的问题。采样时钟的抖动是一个短期的、非积累性变量,表示数字信号的实际定时位置与其理想位置的时间偏差。时钟抖动会使ADC的内部电路错误地触发采样时间,结果造成模拟输入信号在幅度上的误采样,从而恶化ADC的信噪比,采样时钟的抖动对高速、高精度ADC性能的影响也不可忽视[1-2]。

图1所示是一种典型的ADC时钟电路,高速ADC,例如ADS5500,经常采用这种时钟结构。本文针对图1所示时钟电路,分析其内部时钟的参数对ADC性能的影响,分析结果为外部时钟电路设计提供参考。

1 抖动与 Ain、fin、fS 的关系

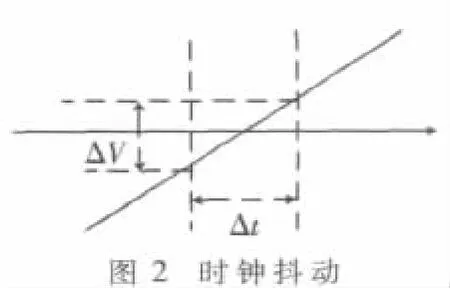

时钟信号启动采样保持器进行采样之前,采样保持电路的内部开关处于闭合状态,电容电压跟踪模拟输入信号的变化,时钟信号的一个边沿到来时开关打开,电容电压保持为该时刻的值。如图2所示,该时刻的电压值为垂直虚线所对应的值,在Δt的采样时间内,产生了一个采样电压误差ΔV,该瞬时误差就是时钟抖动Jitter,采样电压误差的大小取决于输入电压波形。如果没有其他噪声信号,根据图2可以计算出抖动电压的大小和信噪比。如果图1的输入信号为幅值为 Ain、频率为 fin的正弦波,则采样电压的时钟抖动Jitter正比于输入电压在该时刻的斜率和采样时间。则一个周期的时钟抖动Jitter有效值的平方σ2为:

式(1)中,K(t)表示采样时信号的斜率,J表示时钟抖动Jitter。如果忽略量化噪声、热噪声、非线性误差等的影响,仅考虑在时钟抖动作用下的信噪比为:

由式(2)可知,时钟抖动引起的信噪比与输入信号的频率fin有关,随着输入信号频率fin的增大,信噪比下降。也可知时钟抖动引起的信噪比与输入信号幅度Ain无关,但由图2可以看出随着输入信号幅度Ain的降低,时钟抖动Jitter随之减少,因而信噪比与时钟抖动Jitter密切相关。

ADC总噪声由热噪声、量化噪声和抖动三部分组成,如果假定所有的噪声源线性无关,则ADC的信噪比可以用式(3)表示。

式(3)中,T表示热噪声在一个周期内的有效值平方,Q表示量化噪声在一个周期内的有效值的平方,这两项与输入信号的频率fin无关,时钟抖动一个周期有效值的平方σ2则取决于输入信号频率fin。如果要求ADC在输入信号fin较大时SNR高,则必须用抖动小的采样时钟。因此,在高速高精度ADC的设计中,对时钟电路都采用特别的处理方法来降低时钟抖动,比如Maxim公司的Max104等。

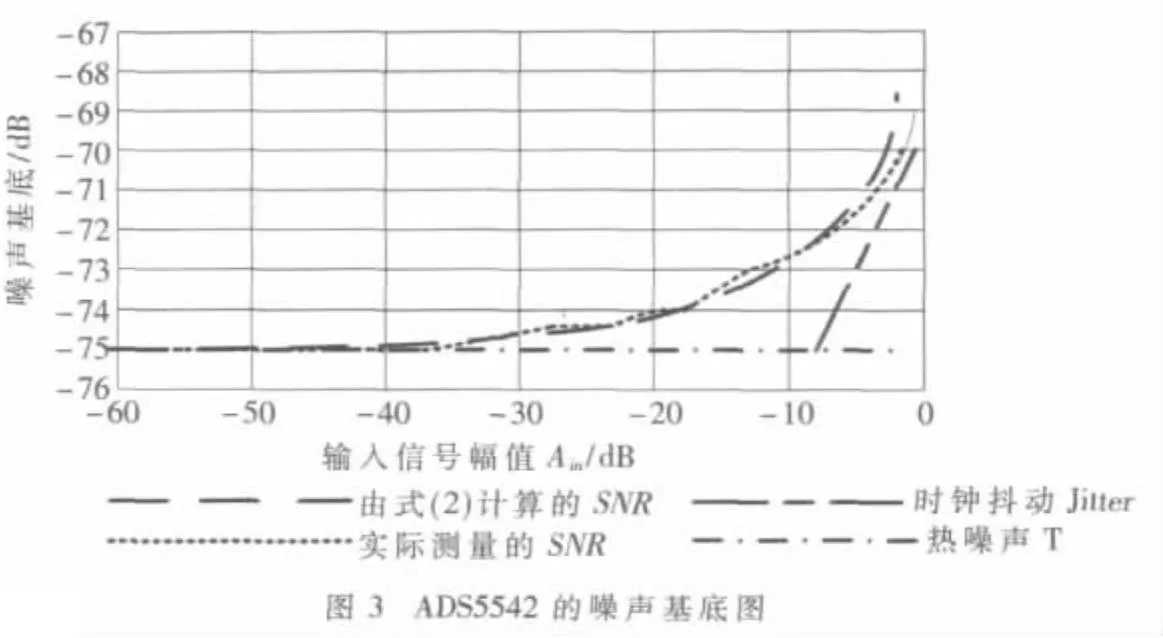

对于一个确定的ADC,当输入信号幅值 Ain低于一定值时,其信噪比主要取决于热噪声和量化噪声,这种情况下时钟抖动对其影响不大。图3所示为ADS5542工作在78 MSPS和230 MHz输入下的实际噪声基底。图3中的理论曲线是在加上250 fs的抖动和1LSB的热噪声下的条件下由式(2)计算得出的,由图可以看出理论曲线与实际测量的噪声基底曲线非常接近。表1所示为在不同的输入信号频率下的信噪比的大小。表中给出了两组数据,一组为实际测量的信噪比SNR,一组为由式(2)计算出来的信噪比SNR。表1中的测量值是在采样频率fs为60 MS/s,并假定抖动频率为200 fs的条件下测量出的数据。由表1可知,由式(2)估算出来的数据和实际测量的数据之间的误差较小,式(2)比较准确地表达了信噪比与输入信号频率之间的关系。

[4]的研究结果可知,采样频率fs不变时,信噪比会随着输入信号的频率增加而降低。如果输入正弦信号自身不受噪声影响,信噪比的下降则是由时钟抖动引起。

由式(2)可知信噪比与采样频率无关。然而实验数据表明,当增加采样频率时,信噪比也随着增加。因为采样频率的增加会把同样数量的噪声扩展到比较宽的频带上,这样可以有效地降低噪声基底。然而,实际计算信噪比时,总噪声还包含热噪声和量化噪声,因此参考文献[4]的研究结果并没有出现信噪比随采样频率增加而增大的现象[4]。

抖动是相位噪声的一种简化,出现在不同地方的相位噪声对系统的影响程度不同。距离载波近的相位噪声体现了采样瞬间的缓慢变化,在比较短的观测时间内与系统无关。距离载波远的相位噪声对系统影响大但容易被滤波器滤出[5]。目前市场上有一部分ADC不仅没有提供任何阻击输入抖动的方案,ADC内部的时钟链反而使抖动更加恶化。

2 抖动的计算

抖动源可能源于外部,例如由用户提供的时钟信号,也可能源于ADC内部时钟电路如放大器的(N1,N2)点和(N3)点。 对于源于在图 1 的(N1,N2)点的抖动,可以采取一定的措施来降低其影响。由图2知该部分抖动与时钟信号的边沿斜率有关。时钟信号的上升沿用于打开采样保持器的开关,理论上时钟信号下降边沿的抖动不影响信噪比,为简化分析假定时钟信号的上升沿和下降沿的斜率相同。

当输入时钟边沿的斜率为无穷大时,加在边沿上的任何电压噪声都不会影响边沿上的时间定位。当时钟边沿斜率变小时,加上边缘上的电压噪声就会产生一个较大的时间误差。当时钟信号为正弦波信号时,增加信号的幅值或提高采样频率都可以提高边沿的斜率。总时钟抖动可以用下列方程描述:

表1 ADS5542的信噪比

式(4)中,JE为外部时钟信号的抖动,JN3为 N3点引起的抖动。K(N1,N2)表示输入放大器的抖动影响,对 ADC而言它是一个常数[6]。C为时钟信号边沿斜率。当输入信号的频率fin比较大时,时钟边沿斜率C相当大,式(4)中第三项的影响甚微,此时信噪比取决于外部抖动和N3点的抖动,根据参考文献[6]中提供的ADS5413的图表,确定出方程(4)中的前两项及 K(N1,N2)的数值。式(4)可以写成:

由式(5)计算出时钟抖动大小,进而由式(4)计算出的信噪比如图4所示,可知用上述方法计算出的信噪比数值和实际测量的数值之间误差较小,表2所示为具体数值比较。

表2 SNR的实际值和测量值

分析表2,如果时钟采用正弦信号,则要求时钟的峰峰值为4 V左右效果较好;如选择单边时钟信号,则其幅值最大值为3.3 Vpp;利用差分时钟信号可以把时钟幅值提高为该值的2倍,而且可以抑制共模干扰,但使用差分时钟信号又带来两个边沿的对称性问题。由参考文献[4]可知,采用较小幅值的单边时钟信号的效果较好于差分时钟信号,主要原因在于差分时钟信号两个边沿的不对称性,而且当数字输出电压增加时会产生耦合在时钟电路中的开关噪声。可以采取降低输入信号频率来减少这种影响。

3 改进措施

由上述分析可知,要降低时钟抖动,关键在于提高时钟信号的边沿斜率,产生近似于方波的时钟信号,具体可以从以下几个方面着手:

(1)使用步进变换器方法,正弦时钟信号经过步进变换器后产生类似于方波的时钟信号。

(2)外加门电路作为比较器把正弦时钟信号方波化。这种方法可以减少N1和N2的影响但是带来的问题是在比较器的输入端N1和N2的平衡性问题。市场上ADC的时钟抖动都比较小,但这些数据都是基于输入信号是方波的假设下得出的,如果使用正弦时钟信号抖动则明显增大。

(3)采用一个具有方波输出的低抖动的时钟源。例如使用电压控制晶体振荡器(比如CDC7005)。但是使用这种电路要受到VCXO的相位噪声质量和CD7005所附加的恶化的限制。不过该电路节省了一个转换器来产生差分时钟。

(4)外部加带通滤波器可以消除时钟信号的抖动,然而,滤波器的幅值衰减降低了时钟的幅度,降低了边沿斜率,增大N1和N2的影响。所以需要在滤波器前面加上放大器或者步进变换器来降低这种趋势。

本文从ADC的输入信号及时钟源的自身参数着手,分析输入信号幅值、频率、采样频率对时钟抖动及ADC信噪比的影响,根据ADC手册数据提供的信息给出时钟抖动的计算方法,并对计算结果进行验证,进而提出减少时钟抖动方法。这种时钟抖动的计算方法不需要外设电路,而且综合考虑了时钟电路的各种噪声源的影响,计算方法简便,而且比较精确。该研究结果为ADC外部电路设计和ADC选型提供了理论依据。

参考文献

[1]赵继勇,彭飞.高速 ADC的低抖动时钟设计[J].电子设计应用,2005,4(2):79-83.

[2]SHINAGAWA M,AKAZAWA Y,WAKIMOTE T,et al.Jitter analysis of high speed sampling systems[J].IEEE JSolid2state Circuit s,1990,25(1):220-224.

[3]唐世悦,王砚方,何正淼.基于 ADC的时钟 Jitter测试平台的研究[J].电路与系统学报,2008,13(6):13-17.

[4]14 Bit,125 MSPS Analog-to-Digital Converter[M].ADS5500 Data Sheet,13-17.

[5]ZANCHI A,BONFANTI A,LEVANTINO S,et al.General SSCR vs.cycle-to-cycle jitter relationship with application to the phase noise in PLL[J].Proceedings of the 2001 IEEE Southwest Symposium on Mixed-Signal Design,2001(2):32-37.

[6]ZANCHI A,PAPANTONOPOULOS I,TSAY F.Measurement and Spice prediction of sub-picosecond clock jitter in A/D converters[J].Proceedings of the 2003 IEEE International Symposium on Circuits and Systems,2003(5):557-560

Research of clock jitter and its effect on high-speed data conversion

Hu Zhihong1,Liao Nihuan2

(1.College of Electric and Information Engineering,Zhengzhou University of Light Industry,Zhengzhou 450002,China;2.Institute of Electric Power,North China University of Water Resources and Electric Power,Zhengzhou 450010,China)

The effect on clock jitter and the SNR of the ADC caused by the input amplitude,input frequency and sampling frequency is studied in this paper.The mathematical estimated method of clock jitter is given based on the data sheet of ADC,and the results of the measurements are analyzed.The real measured result and the estimated result were compared.Some methods to minimize the clock jitter are put forward.

clock jitter;SNR;frequency

TP3

A

1674-7720(2011)02-0085-04

2010-07-24)

胡智宏,男,1974年生,副教授,主要研究方向:电子信息技术、检测技术。

廖旎焕,女,1975年生,硕士,讲师,主要研究方向:非线性控制及应用。