改进型双频段低噪声放大器设计*

程知群,徐胜军,朱雪芳,高俊君

(杭州电子科技大学射频电路与系统教育部重点实验室, 杭州310018)

低噪声放大器是无线通讯系统中接收机的重要组成部分,它的噪声和增益等参数直接影响着接收机的灵敏度等性能。近20年来CMOS技术在射频电路中不断应用和发展,一方面使得电路的功耗和成本的降低,同时也使得片上集成系统成为了可能。随着无线通信技术的发展和技术的不断创新,人们对通信技术有的更高的追求,市场对多模式、多频段的通讯接收机的需求和要求也不断的增加,在此领域已经开展的相关的研究[1-2],成为了无线通讯射频前端的研究热点之一。早期提出的双频带低噪声放大器是由射频开关控制,每次只能工作在一个谐振频率上[3-4]。这种解决方案不能使电路同时工作在两个频率上且由于开关的插入损耗会恶化电路的噪声。

本文设计一种可同时工作在900MHz/1900MHz双频带低噪声放大器,通过对电路进行优化设计,即用高Q的LC网络替代级间低Q电感,实现了电路总体性能的提高,也降低了芯片面积;仿真结果表明电路在两个频段内实现了高增益、低噪声,同时具有良好输入输出端口匹配。设计的电路中同时采用电流复用技术降低了电路的功耗。

1 电路分析与设计

设计的低噪声放大器电路拓扑结构如图1 所示。电路由两个共源晶体管M1和M2构成,第一级电路采用的是电感源极负反馈结构[5],这种结构可以在提供低噪声系数的同时,实现50 Ω的输入阻抗。在M1的漏端和M2源端之间加入一个并联LC网络来产生一个交流高阻抗, M2管的栅端和M1管的漏端之间串接电感Lg2和电容C2并在工作频带高端产生谐振。M1管栅极接两个LC并联网络,电感Lg1,L0和电容Cg, C0, Cex和M1的寄生电容Cgs使输入阻抗Zs虚部为零。晶体管M1, M3, Rref和Rb1为电流镜结构,为M1管提供偏置电压。电阻Rb2为M2管提供偏置电压的同时阻止交流信号对地短路,在M2管漏端接Ld2与其漏端寄生电容形成高阻抗谐振电路, Rd的引入增大谐振频率处的带宽。 C01、L01和C02实现双频段阻抗下变换,将Ld2和Rd提供的大阻抗实部在两频段下均匹配到50 Ω, L02对虚部进行匹配,实现虚部共轭。C1和C4为隔直电容。

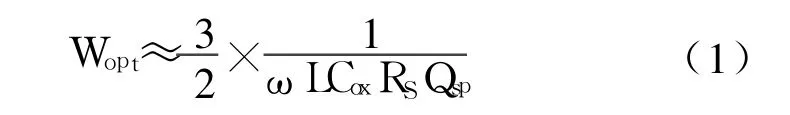

根据功耗约束条件下获得最优噪声,输入管的栅宽公式[6]为,

式中:Cox单位面积氧化层电容, L为有效栅长, Rs为源电阻, Qsp为噪声最优匹配时输入端的品质因数,其取值范围一般为3.5到5.5[7]。本文取Qsp的值为4.5。Cox的值可根据工艺参数计算得到。由于噪声会随着频率的增加而恶化,因此我们选择在高频工作点进行优化,以减少高频点噪声因子的“短板效应”[8]。所以取ω=1 900 MHz进行最优化设计,根据公式(1)可计算出栅宽大约为350 μm,根据电路的最终优化取M1栅宽为400 μm。 M2管与M1管取相同的尺寸,为了限制整个电路的功耗,应尽可能减小偏置电路的功耗,取M3的栅宽为60 μm。

图1 双频段LNA电路拓扑图

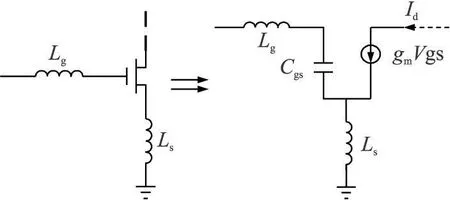

1.1 电流复用结构分析

图2所示,这是一个采用电流复用技术的两级共源放大器结构[9]。图中Ld1、ZL分别是每个共源放大器的负载, C2为耦合电容,调节Lg2使得它与第二级输入等效电容Cin2产生级间串联谐振。当它们发生谐振后,为M1漏级实现低阻抗通路。同时, C3是旁路电容,为M2提供交流接地。 Ld1提供一个交流高阻抗,这样Ld1、C3、Lg2和C2的引入使得共源共栅连接的M1和M2变成了两级共源放大器结构,而与常规的两级放大器不同是该电路采用了同一个电源。这样就有效地降低了电路的功耗。

图2 电流复用结构

1.2 输入匹配分析

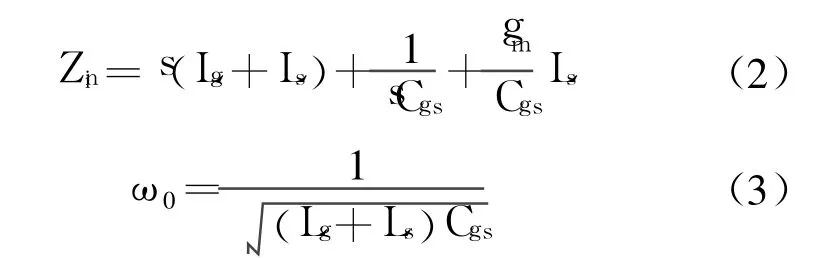

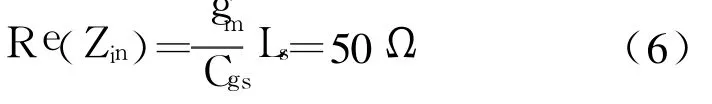

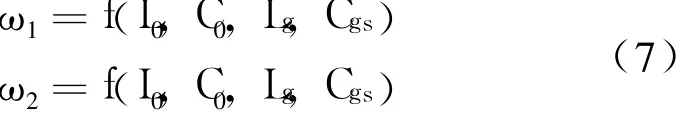

通常在射频接收机中, LNA的输入端直接接天线,或者是接一个带通滤波器,因此,要对电路进行输入匹配来实现功率的最大传输[10]。图3为传统输入匹配电路及等效电路,其输入阻抗表达式为:

其中gm是M1的跨导, ω0是谐振频率。

图3 传统输入匹配结构及等效电路

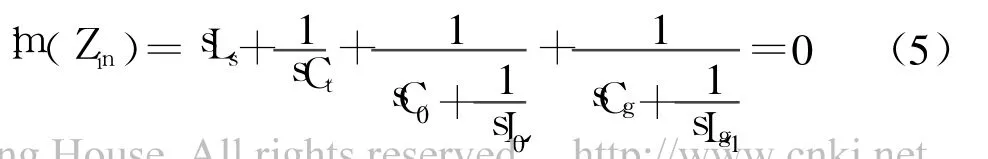

本文设计的是双频段LNA,这就对电路输入匹配提出了更高的要求。使阻抗和噪声要在两个不同的频率ω1和ω2同时达到最佳匹配。为此,我们在输入端加入一个LC并联电路L0和CO,如图1 所示,其输入阻抗表达式为:

此输入阻抗匹配必须满足下面两个等式:

其中Ct=Cgs1+Cex, s=jω

通过等式(4)得出ω1和ω2。

根据式(4), (5), (6)可以确定它们的值,如表1所示。

表1 电路主要元件参数

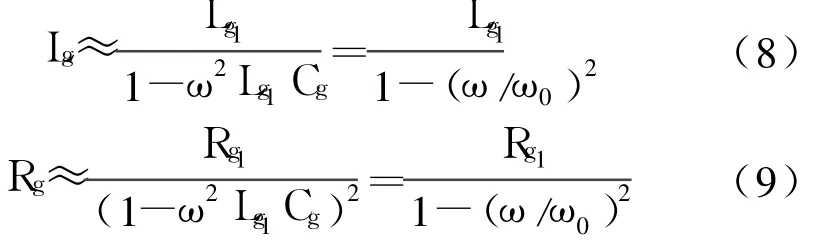

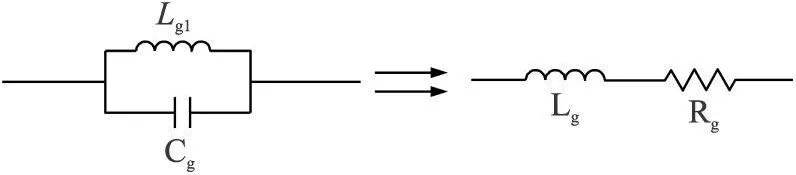

1.3 LC网络的设计

在输入匹配中,栅极电感如图3中的Lg和电流复用电路的级间匹配电感如图2中的Ld1都比较大。这样就使得电路占用的面积比较大,同时也引入更大的噪声。因此,本设计中采用了一种LC并联网络来替代大电感的方法[11],如图1中的Lg1、Cg并联网络和Ld1、Cd1并联网络。使用这种LC网络可以达到与一个大电感相同的效果,但是并联网络中电感要小很多,使得电路的面积得到减小,电路的噪声也得到改善。下面给出进一步的原理分析,图4为LC并联网络及其等效电路。图4左边为一个并联网络,可以等效成一个理想的感抗Lg和一个电阻Rg的串联,如图4 的右边图,其等效阻抗为Z=Rg+jωLg。其中, Rg1为电感Lg1的寄生电阻, ω为工作频率。根据式(8),如果能满足

也就是说工作频率ω在0 和近ω0之间, Lg的电感值都比Lg1大,并随着ω从0趋近ω0, Lg1将远小于电感Lg。这样就可以用较小电感Lg1与Cg组成的并联网络来代替大电感Lg,满足了电路的功能,又节省芯片面积,降低了因大电感产生的热噪声。

图4 并联LC网络及其等效电路

2 仿真结果

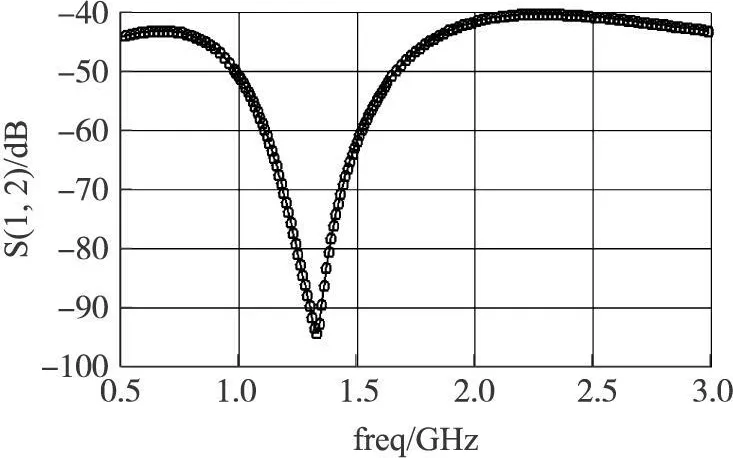

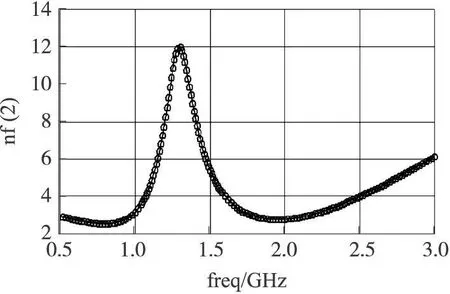

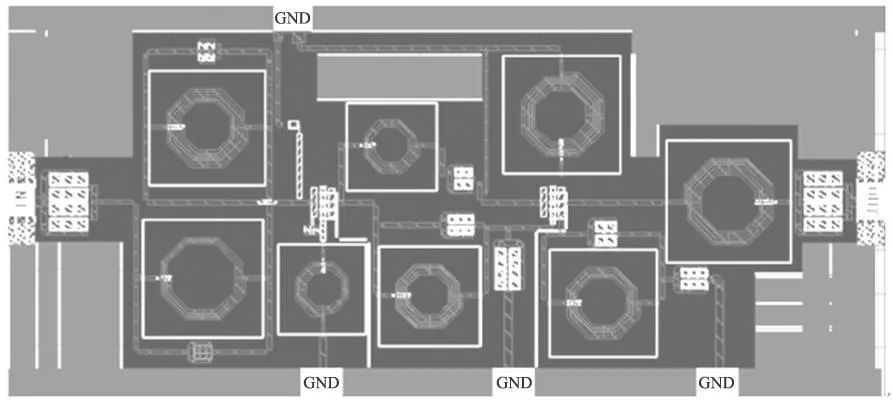

设计采用了SMIC 0.18 μm CMOS工艺库,使用ADS和Cadence软件进行电路仿真和版图绘制。由图5可以看出,当LNA工作在900 MHz/1 900 MHz两个频段的要求带宽50 MHz/75 MHz内,正向传输增益S21分别大于16.6 dB和16.0 dB,表现出较高的增益。图 6 显示了输入反射系数 S11均小于-18.6 dB,输出反射系数S22也均小于-12 dB,表明两个端口在双频带内都具有良好的阻抗匹配。图7给出了反向传输曲线, S12均小于-40 dB,表明电路的反向隔离特性很好。图8所示噪声系数NF在两个频带内分别小于2.6 dB和2.8 dB。图9给出了三阶交调测试曲线,图中显示两个频段的中心频率点的IIP3分别为-9.5 dBm和-7.9 dBm,表现出电路具有较好线性度。图10是采用Cadence Virtuoso Layout Editor优化设计的低噪声放大器的版图,其面积(包括电极)为0.83 mm×1.62 mm。

图5 正向传输增益

图6 输入输出反射系数

图7 反向传输增益

图8 噪声系数

图9 IIP3仿真结果

图10 低噪声放大器版图

3 结论

本文采用SMIC 0.18 μm CMOS工艺技术成功地设计了一种应用于双模手机通信的双频带低噪声放大器。通过对电流复用技术的电路拓扑改进,采用高Q小电感的LC网络代替低Q大电感实现输入和节间匹配,提高了放大器的噪声性能,也减小了电路的芯片面积。仿真结果表明,放大器还同时具有较好的增益、端口驻波比和线性度。该低噪声放大器具有很好的实用价值。

[ 1] Lu L H, Hsieh H H, Wang Y S.ACompact 2.4/5.2GHz CMOS Dual-Band Low-Noise Amplifier[ J].IEEE Microwave Wireless Components Letters, 2005, 15(10):685-687.

[ 2] Agnelli F, Albasini G, Bietti I, et al.Wireless Multi-Standard Terminals:System Analysis and Design of a Reconfigurable RF Front-Dnd[J].IEEECircuits and SystemsMagazine, 2006, 6(1):38-59.

[ 3] Martins M A, Fernandes JR, Silva M M.Multi-Band Combined LNA and Mixer[ C] .Circuits and Systems, 2008.ISCAS 2008.IEEE International Symposium on, 2008, 18-21:920-923.

[ 4] 景一欧,李勇,赖宗声,等.基于0.18 μm CMOS工艺的2.4/5.2 GHz双频段LNA的设计[ J] .电子器件, 2007, 30(4):1144-1147.

[ 5] Pietro Andreani, Henrik Sjoland.Noise Optim ization of an Inductively Degenerated CMOS Low Noise Amplifier[ J] .IEEE Transactionson Circuits and Systems, 2001, 48(9):835-841.

[ 6] Shaeffer D K, Lee T H.A 1.5 V 1.5 GHz CMOSLow Noise Amplifier[J] .IEEE JSolid-State Circuits, 1997, 32(5):745-759.

[ 7]Lee T H.The Design of CMOSRadio-Frequency Intergrated Circuits[ M] .Cambridge:Cambridge University Press, 1998:287.

[ 8] 杨帆,任军,郑薇.宽带CMOS低噪声放大器[J].电子科技大学研究生学报, 2006, 36:40-44.

[ 9] Yi-Jing Lin, Shawn S.H.Hsu, Jun-De Jin, C.Y.Chan, et al.A 3.1-10.6 GHz Ultra-W ideband CMOS Low Noise Amplifierwith Current-Reused Technique[ J].IEEE Micowave and Wireless Components Letters, 2007, 17(3):232-234.

[ 10] 池保勇,余志平,石秉学.CMOS射频集成电路分析与设计[ M] .北京:清华大学出版社, 2006:197-199.

[ 11] Mou Shouxian, Ma jian-Guo, Yeo kiat Seng, etal.A Modified Architecture Used for Input Matching in CMOS Low-Noise Amplifiers[ J] .IEEE Transactions on, 2005, 52(11):784-788.