一种基于数字信号处理器和现场可编程门阵列的磁悬浮控制器

徐俊起,吴小东

(上海磁浮交通发展有限公司,上海 201204)

0 引言

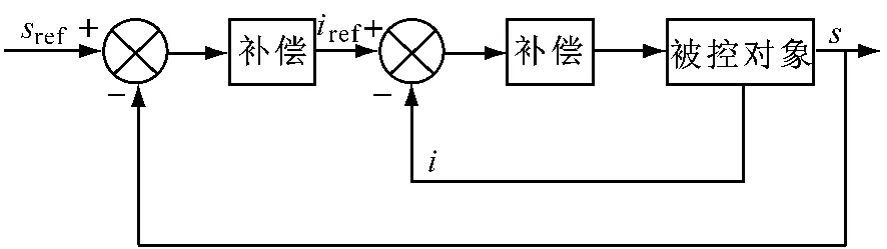

为增强控制系统对磁悬浮列车系统参数变化的适应性、抑制车轨共振,磁悬浮控制器通常采用双环控制[1-2],即把磁悬浮控制器分为电流环子控制器和位置环子控制器,如图1所示:位置环由间隙信号测量值s和给定间隙值sref组成;电流环由电流信号测量值和给定电流值iref组成。文献[1]提出将磁悬浮系统分解为电流环和悬浮子控制系统两个串行、解耦的子系统来设计控制器;文献[2]提出将悬浮系统分为电流环和位置环进行控制,并设计了以TMS320F2407数字信号处理器(Digital Singal Processing,DSP)为核心的控制器对其进行试验验证;文献[3]对磁悬浮控制器的电流环作了研究,并设计了实用模拟电流环电路;文献[4]对磁悬浮列车悬浮控制器的电流环进行了深入研究,并提出了次速电流环的概念;文献[5]对磁悬浮控制器数字化进行了分析,并采用MC80C196单片机予以实现;文献[6]用 DSP实现了磁悬浮控制器。

图1 磁悬浮系统的双环控制示意图

在磁悬浮控制系统中,电流环控制非常重要,系统降阶的依据就是电流环具有足够快的速度[1]。但是,在电流环调节过程中,由于电磁铁线圈电感和电阻不断变化,因此电流环的系统参数不是固定的。另外,由于电流环是内环,位置环是外环,要求电流环比位置环具有更快的速度。

在以往的磁悬浮控制中,由于硬件成本和单片机运算速度等原因,通常采用模拟电路实现磁悬浮控制器。模拟磁悬浮控制器存在灵活性差、抗干扰性差、参数调整困难等方面的缺点。随着DSP等的应用,数字化磁悬浮控制器得到了广泛推广,并且随着双环控制理论的应用,出现了三种数字磁悬浮控制器结构:第一种是半数字化结构的控制器,即位置环采用DSP实现,电流环采用模拟电路实现;第二种是用单个DSP实现位置环和电流环的数字双环单DSP控制器;第三种是双DSP结构的磁悬浮控制器,即用一个DSP实现电流环控制,另一个DSP实现位置环控制。

本文对各种数字磁悬浮控制器进行分析,提出了一种结构简单、性能优越,更适合于双环控制的基于DSP和现场可编程门阵列(Field Programmable Gate Array,FPGA)的新型磁悬浮控制器。

1 数字双环单DSP磁悬浮控制器

第一种半数字化结构磁悬浮控制器还没有完全实现电流环的数字化,存在明显不足,这里不作详细分析。本文重点分析数字双环单DSP控制器和双DSP结构的磁悬浮控制器。

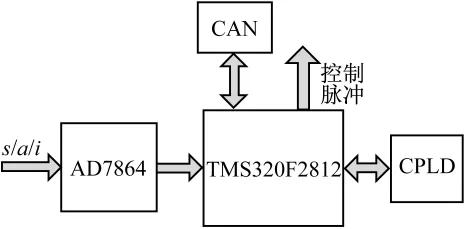

数字双环单DSP控制器如图2所示。图中DSP采用TI公司的TMS320LF2407或TMS320F 2812。由于TMS320LF2407和TMS320F 2812内部自带的片内AD芯片转换误差较大、抗干扰能力较弱,对于悬浮控制器这种采样精度要求较高,且工作环境比较恶劣的情况,其片内A/D往往不能达到要求,因此需要外扩A/D。DSP与外围芯片之间的地址逻辑由复杂可编程逻辑控制器(Complex Programmable Logic Device,CPLD)实现。

这种数字双环单DSP控制器虽然能够实现位置环和电流环的数字化控制,但存在以下缺点:

(1)采样频率必须以电流环采样速度为准,需要保持高采样速度;

(2)控制周期必须以电流环控制周期为准,保持高速运行,系统负荷重;

(3)在软件设计上,电流环和位置环不能完全解耦,调试困难;

(4)试验证明,如果选用的DSP速度较慢,则很难实现系统的稳定悬浮。

图2 数字双环单DSP磁悬浮控制器原理框图

2 双DSP结构磁悬浮控制器

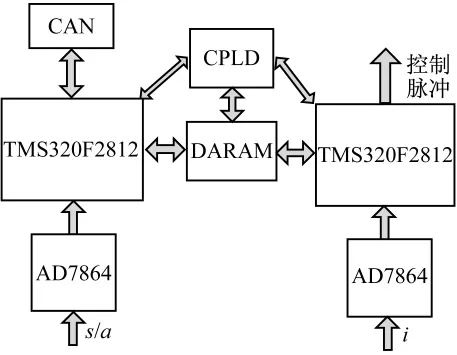

双DSP结构的磁悬浮控制器如图3所示。图中 DSP采用 TI公司的 TMS320LF2407或TMS320F2812。由于两个DSP之间需要通信,因此增加双口RAM芯片。两个DSP之间及DSP与外围芯片之间的地址逻辑由CPLD实现。由于采样精度的原因,需要外扩A/D芯片。另外,需要扩展CAN等通信接口,实现磁悬浮控制器与上位机之间的通信。DSP1实现位置环控制和对外通信,DSP2实现电流环控制。

图3 双DSP结构磁悬浮控制器原理框图

双DSP控制器虽然能够实现位置环和电流环的独立双环控制器,但具有以下不足:

(1)硬件系统结构复杂,容易发生硬件故障;

(2)需要增加双口RAM和CPLD,成本较高;

(3)DSP外围接口丰富,用于电流环控制的DSP2资源浪费;

(4)系统扩展不灵活。

3 基于DSP和FPGA的磁悬浮控制器设计

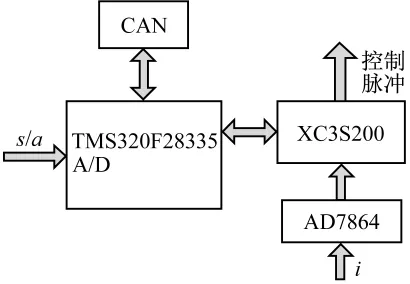

在以上几种数字控制器的基础上,本文介绍基于DSP和FPGA的磁悬浮控制器,其结构如图4所示,图中DSP用于实现位置环控制和对外通信,FPGA用于实现电流环控制及DSP与外围芯片之间的地址逻辑,DSP和FPGA之间采用并口通信。该系统结构简单、高速有效,达到了对DSP和FPGA资源的各取所长、合理配置的目的。为提高AD采样精度和抗干扰能力而不外扩AD,DSP选用 TI公司新型浮点 DSP芯片TMS320F28335。TMS320F28335对片内AD进行了改进,性能大大提高,并采用了浮点运算器。FPGA选用XINLIX公司的XC3S200系列,外扩高速AD转换器AD7864,实现电流值i的高速采样,以适应高速的电流环控制。

图4 基于DSP和FPGA的磁悬浮控制器原理框图

4 基于DSP和FPGA的磁悬浮控制器实现

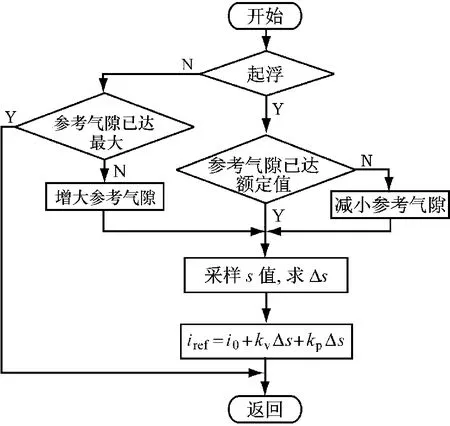

(1)位置环控制器的实现。位置环采用位置反馈和垂向速度反馈的方法,控制周期设为200 μs,控制算法可采用PID控制,也可采用非线性控制等先进的悬浮控制算法。PD控制算法软件流程如图5所示。

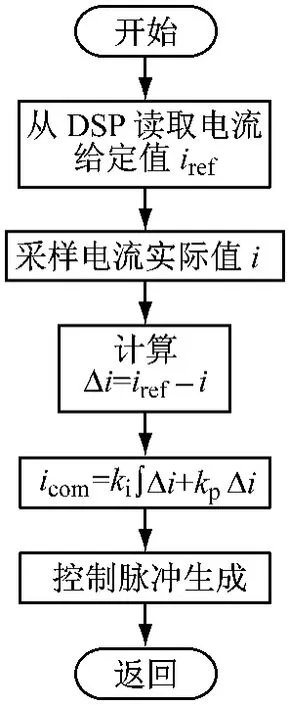

(2)电流环控制器的实现。电流环控制器在FPGA中实现,采用VHDL语言书写,采用PI调节控制策略,控制周期为50 μs。试验中可采用反复凑试的方式,确定合理的PI参数。软件流程图如图6所示。

图5 位置环控制器软件流程图

图6 电流环控制器软件流程图

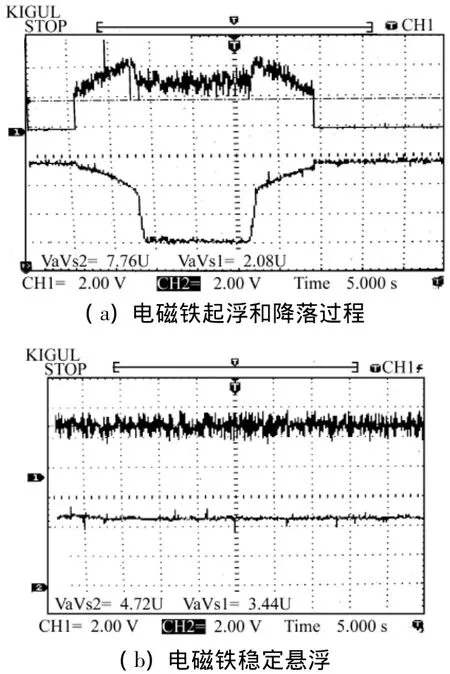

图7 悬浮控制试验波形

(3)悬浮控制试验结果。对根据以上方法设计的磁悬浮控制器进行悬浮控制试验。悬浮电磁铁起浮、下落和稳定悬浮的试验结果如图7所示。图中信号1为电流波形,信号2为间隙波形。电磁铁落下时,悬浮间隙信号电压值约为10 V(表示20 mm),浮起后约为4.7 V(表示9.4 mm)。稳定悬浮时电流值约为35 A。试验证明,系统能够很好地实现稳定悬浮。

5 结语

本文通过对传统控制器硬件不足的分析,根据磁悬浮系统双环控制理论,设计了新型的基于DSP和FPGA的磁悬浮数字控制器的软、硬件,并进行了试验验证。理论分析和试验结果表明,该控制器结构简单合理、高速有效,能够完成先进的悬浮控制算法。

[1]李云钢.磁浮列车悬浮系统的串级控制[J].自动化学报,1999,25(2):247-251.

[2]刘横坤.磁悬浮列车的双环控制[J].控制工程,2007,14(2):198-200.

[3]徐晓峰,连级三.磁悬浮斩波器电流闭环误差放大器设计研究[C]∥中国首届电子电源及功率自关断器件应用技术研讨会,1999(8):191-194.

[4]李云钢.磁浮列车悬浮控制器的电流环分析与优化设计[J].国防科技大学学报,2006,28(1):94-97.

[5]李熹,蒋启龙.基于MC80C196的单磁铁悬浮控制[J].机车电传动,2000(1):25-27.

[6]吴建军,张昆仑.用DSP实现新一代磁浮列车悬浮控制器[J].电子技术应用,2000,26(7):25-27.