XCTD剖面仪数据传输电路的设计与实现

贾志成,于晓山,尼建军,李永军,陈雷

(1.河北工业大学信息工程学院,天津300401;2.海军司令部航海保证部,天津300042;3.国家海洋技术中心,天津300112;4.天津商业大学信息工程学院,天津300134)

XCTD剖面仪数据传输电路的设计与实现

贾志成1,于晓山1,尼建军2,李永军3,陈雷4

(1.河北工业大学信息工程学院,天津300401;2.海军司令部航海保证部,天津300042;3.国家海洋技术中心,天津300112;4.天津商业大学信息工程学院,天津300134)

针对XCTD(投弃式温盐深)剖面仪数据传输速率低、可靠性差的缺点,提出基于曼彻斯特编码的基带传输技术。在系统结构设计的基础上,着重讨论了基于FPGA的曼彻斯特编码器、位定时提取电路和自动增益控制电路的设计。通过测试表明,编码后的系统不仅可以使用基带信号直接传输,而且能够满足系统的通信速率要求。

XCTD;曼彻斯特码;自动增益控制;全数字锁相环

1 引言

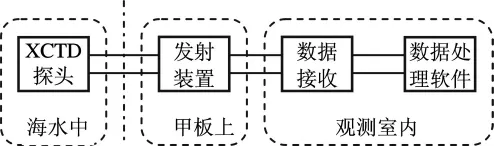

XCTD是投弃式(Expendable)电导率(Conductivity)、温度(Temperature)深度(Depth)剖面仪的简称,是国外近年研制并得到快速发展的一种先进的海洋测量设备。在海洋科学研究、海洋经济、国防建设等诸多方面都有非常重要的意义。XCTD由投弃式测量探头、传输导线、数据接收装置、实时数据处理软件四部分组成。系统结构如图1所示。

图1 XCTD剖面仪结构

XCTD测量探头为一次性使用,由位于甲板上的发射装置发射入水,入水后探头中的温度、电导率传感器即开始测量,随着测量探头在水中的下沉(速度约3~5 m/s),探头内部的数据采集器实时完成温度和电导率的采集、处理,并以数字信号形式通过直径为0.1 mm的传输线同步传输到船上接收装置。探头入水的同时数据处理软件开始计算探头入水深度,并对温度、电导率数据进行合理的对应、平滑、平均、滞后修正等处理,实时获取温盐深剖面数据,绘制温盐剖面曲线[1]。可见,系统水下探头与测量船上数据接收板之间的数据传输性能的优劣至关重要,数据传输电路是船用投弃式温盐深剖面仪的重要组成部分。

系统有线信道是3 000 m长、直径约0.1 mm的两条漆包线,绕成两个线轴分别安装在水下探头和船上发射装置内部。由于线径很细,当探头下落时,线轴能够自由展开,而不影响到探头的下降速度。针对这种特殊的信道,传统方法采用频带传输技术,系统由分立元器件和小规模集成电路构成,因而信息速率低,且灵活性差。本文提出一种基于现场可编程门阵列FPGA的基带传输系统,可以提高信息传输速率,并具有很大的灵活性和实用性。

2 信道和方案分析

在静态条件下测量传输线开路电感246 mH,开路电容66.4 nF,短路电阻13.7 kΩ。随着线圈的展开,这些分布电容和等效电感会发生很大变化。在线轴未展开的情况下,输入峰峰值为5 V的正弦波,信道的幅频响应特性如图2所示。试验证明,该有线信道在频率大于150 Hz以后,随着信号频率的提高,信号幅度将迅速衰减,此通信信道是典型的带限和非线性变参信道,对于数据传输非常不利。

图2 信道的幅频特性

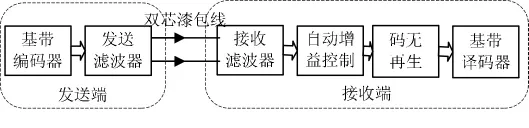

水下数据采集系统的原始数据是单极性的非归零码(NRZ),直接传输不仅会造成严重的波型畸变以致无法接收,而且信号频谱中不含有定时分量,使位时钟恢复困难。频带传输是一种常用的数字信号传输方式,但是工作频段高,信道衰减严重,传信率和误码率指标较低,不能满足系统要求。因此为了提高信息传输速率,并考虑到在接收端提取时钟方便,采用基于曼彻斯特码的基带传输系统,系统结构如图3所示。

图3 XCTD剖面仪基带传输系统结构

曼彻斯特码又称为数字双相码,其功率谱中无直流分量,且低频和高频分量较小,适合在此信道中传输。波形在每一位码元中间都有跳变,因此具有丰富的定时信息,在接收端利用简单的非线性变换后即可提取位时钟[2]。

3 系统设计

3.1 发送端电路设计

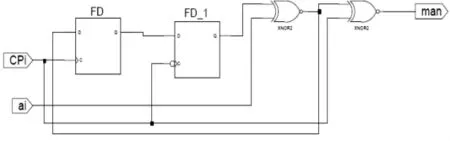

由于曼彻斯特码译码有时候会出现相位不确定的问题,所以在编码之前需要对原信码进行差分编码,根据差分编码的原理,di=ai+di-1,ai是绝对码,di是相对码,di-1为相对码延时一个码元周期。曼彻斯特码的编码规则是:将输入的二进制符号“0”编码为一对比特“10”,又将二进制符号“1”编码为一对比特“01”。可以用单极性非归零码与定时信号的模二和来产生,即:man=di+CPi,man是曼彻斯特码,同步定时信号CPi的码速率为基带码速率的2倍。用Verilog HDL语言编写基带编码器代码,通过ISE9.1i软件观察其RTL级示意图,如图4所示。

图4 编码器RTL级示意图

FPGA输出的曼彻斯特码实际是单极性码,可以通过一个发送滤波器滤除其直流分量,变为双极性。发送滤波器的另一个重要作用就是波形形成。如果直接用矩形脉冲作为传输码,由于矩形脉冲的频谱很宽,而如图2所示信道的可用频带有限,会对信号造成严重的失真。因此需要设计发送滤波器和接收滤波器共同来补偿整个传输系统的幅频特性和相频特性,使其传输特性接近基带无失真传输条件,即理想低通特性。

3.2 接收端电路设计

3.2.1 自动增益控制

随着探头的下降,导线自然展开,因此信道特性是时变的。经过大量实验证明,随着线的展开,信号的衰减量呈现出减小的趋势。当传输1200 Hz信号时,输出端信号的动态范围达到20 db,所以为了保证后续电路的正常工作,线上信号经过接收滤波器滤除噪声后,需要增加自动增益控制电路,使输出电平保持在一定的范围内。

本文使用性价比很高的集成电路SA571,实现自动增益控制电路。实际电路如图5所示。

图5 自动增益控制电路

此电路分为两部分,第一部分是精密小信号差分放大器AD620,对接收到的微弱信号进行初步放大,达到后续电路对输入信号的要求,并可以滤除共模噪声。第二部分是由SA571组成的自动增益控制电路,对AD620放大后的信号进行自动增益控制。当输入信号在20 db范围内变化时,输出信号的电平保持在±1 db范围内,峰峰值约为2 V,满足系统要求。

3.2.2 位定时提取电路

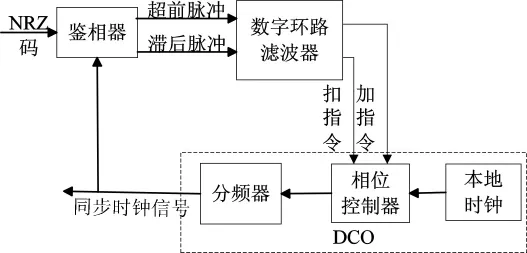

自动增益控制后的信号经过码元再生电路,恢复出NRZ数字信号后译码。译码的关键是恢复出同步定时信号,曼彻斯特码含有丰富定时信息,可利用电平的正、负跳变提取定时,但是它所提取的时钟频率是符号速率的2倍,再由它分频得到定时信号[2]。位定时信号是由基于FPGA的全数字锁相环提取的。全数字锁相环的组成可分为3部分:数字鉴相器(DPD)、数字环路滤波器(DLF)和数控振荡器(DCO)。其工作原理框图如图6所示。

鉴相器采用超前—滞后鉴相器(LL-DPD),它的输入是单极性非归零信号,输出的超前—滞后脉冲经环路滤波器的过滤后输出“加”脉冲指令或“扣”脉冲指令。超前-滞后鉴相器通常有两种实现方式:微分型和积分型,积分型LL-DPD具有优良的抗干扰性能,而它的结构和硬件实现都比较复杂。微分型LL-DPD虽然抗干扰能力不如积分型LL—DPD,但是结构简单,硬件实现比较容易。本文采用微分型LLDPD,将环路抗噪声干扰的任务交给DLF模块负责。

图6 全数字锁相环原理图

环路滤波器的作用在于提高环路相位校正的准确性,因为输入信号在信道传输过程中,受到了噪声的干扰。环路出现误控和漏控的可能性较大,尤其是在输入信噪比很低的时候。为此,首先将鉴相器输出的超前或滞后脉冲经过环路滤波器过滤后再加到相位控制器上,这样就可以大大地减少噪声对环路的干扰。虽然采用环路滤波器提高了相位校正的准确性,与此同时,因为环路滤波器是用寄存器进行累计计数,输入N个脉冲才输出一个控制指令脉冲,这必然使环路的锁定过程或同步建立时间加长。因此,减小同步误差与减小同步建立时间两者相互矛盾。

DCO由本地信号时钟、相位控制器和分频器构成。频率稳定的本地信号时钟输出频率为F的脉冲序列,在未经控制的情况下,该序列经M次分频后得到频率为f0的方波信号。M分频器的输出信号与输入的二进制数字信号通过鉴相器进行相位比较。鉴相器输出表征输入信号是超前还是滞后于DCO输出同步信号的超前脉冲或滞后脉冲。再经环路滤波器后变为“加”脉冲指令或“扣”脉冲指令,去控制本地信号时钟脉冲序列“加”入一个脉冲或“扣”除一个脉冲,从而改变分频器输出的脉冲信号相位。经环路的反复调整,就可以得到较为准确的同步信号[3]。

从LL-DPLL得到的同步时钟CP1频率是信号速率的2倍,再由它分频得到的定时信号CP2必定存在相位的不确定问题。这可以靠后面的差分译码得以解决。由于锁相环存在相位误差和同步建立时间,所以当NRZ码与CP1做模二加的时候,会出现毛刺。因此,在做模二加之前用同步时钟信号的上升沿对NRZ信号采样得到an,差分码。对差分码dn进行差分译码,译码后恢复出的原信码,其中dn-1为dn通过时钟信号CP1延时一个码元周期后的信号。

4 仿真与实现

FPGA(Field Programmable Gate Array,即现场可编程门阵列)具有性能好、规模大、可重复编程、开发投资小等优点[4]。本设计中基带编译码器均采用XILINX公司的EDA软件ISE9.1进行设计,并在Spartan3E系列的FPGA芯片XC3S100E上实现。为了仿真实验方便,基带数据输入采用四级伪随机码电路——从ISE器件库中调用4个D触发器、2个异或门和一个四或非门。利用ModelSim SE PLUS 6.2b对编译码电路进行仿真,仿真波形如图7所示。图7中ai表示四级伪随机码电路数据输出,di表示四级伪随机码电路数据输入在同步时钟的作用下差分编码输出,man表示由CPi和di产生的差分曼彻斯特码,CP1为锁相环提取的同步时钟,an表示man信号经过CP1采样后的信号,dn表示曼彻斯特解码后的差分信号,bn表示差分译码后得到的绝对码。

图7基带编译码电路的ModelSim仿真波形

图7 的仿真结果表明:基带编译码器均可正确完成各自功能。从图中可以看出锁相环开始时输出的同步时钟信号CP1超前于man信号,经过环路的逐步调整,最近达到相位的锁定,译码输出bn延时约1 ms后与ai一致,实现正确地译码。然后将生成的配置文件通过集成开发环境配置到FPGA中进行实际测试。将bn引脚电平通过Max232芯片转换成RS-232电平后与PC机串口相连,在3 000 m漆包线逐渐展开的过程中用串口软件监测解调电路输出,实测结果完全正确,达到了设计要求。

5 结语

本文针对XCTD剖面仪的信道特征,采取基于FPGA的曼彻斯特码基带传输技术,提高了通信速率和系统稳定性,而且降低了电路复杂程度,减小了电路面积。该电路在目前的实际测试中,信息速率为1 200 bit/s,误码率小于0.01%,完全可以满足整个数据采集系统的要求。

[1]武玉华.XCTD定标方法研究[J].海洋技术,2007,26(2):14-16.

[2]周炯槃,庞沁华,续大我,吴伟陵.通信原理[M].北京:北京邮电大学出版社,2005.

[3]胡华春,石玉.数字锁相环原理与应用[M].上海:上海科技出版社,1990.

[4]薛小刚,葛毅敏.Xilinx ISE 9.X FGPA/CPLD设计指南[M].北京:人民邮电出版社,2007.

Abstract:Aiming at low data transmission rate and reliability of the XCTD(Expendable Conductivity,Temperature and Depth)Profiler,baseband transmission technology based on Manchester code is proposed.Based on system structure design,the emphasis is to discuss the design of Manchester coder and bit synchronization extraction circuit and AGC circuit.The test result shows that the system after coding can make baseband signal transmit directly and meet the requirement of communication rate.

Key words:XCTD;Manchester code;automatic gain control;all digital phase-locked loop

Design and Realization of Data Transmission Circuit for XCTD Profiler

JIA Zhi-cheng1,YU Xiao-shan1,NI Jian-jun2,LI Yong-jun3,CHEN Lei4

(1.College of Information Engineering,Hebei University of Technology,Tianjin 300401,China;2.The Navigation Guarantee Department of Chinese Navy Headquarters,Tianjin,300042,China;3.National Ocean Technology Center,Tianjin 300112,China;4.College of Information Engineering,Tianjin University of Commerce,Tianjin 300134,China)

TP76

B

1003-2029(2010)02-0001-04

2010-02-18

国家高技术研究发展计划(863)资助项目(2006AA09Z131)

贾志成(1957-),男,教授。主要研究方向:现代通信,遥测遥控,最佳信号设计;于晓山(1984-)男,硕士研究生。主要研究方向:数字通信,电子测量。