可变波特率和载频的2FSK数字调制器的FPGA实现

(广西民族师范学院 物理与信息技术系,广西 崇左 532200)

1 引 言

二进制移频键控(2FSK)是数字通信中常用的调制方式之一,由于具有较好的抗噪性能和抗衰落性能,因此,在电力载波通信、铁路通信系统和低速Modem等领域中得到了较为广泛地应用[1-2]。然而,目前大多数的2FSK调制器仍采用固定的波特率和调制频率进行通信,由于其参数(波特率和调制频率)不能随着信道状态的变化而变化,不利于通信质量的提高。

针对以上情况,本文充分利用现场可编程门阵列(FPGA)的灵活性,设计2FSK调制器,其波特率和调制频率均可编程可调:当信道无干扰时,提高波特率;当信道中存在干扰时,降低波特率或者改变调制器的调制频率。因此,本系统在提高系统的频带利用率和降低误码率等方面具有较好的优势。

2 硬件设计结构及其工作原理

为了减少现场可编程门阵列(FPGA)的I/O口占用数量,决定把调制器设计成基于Avalon总线的IP核形式。

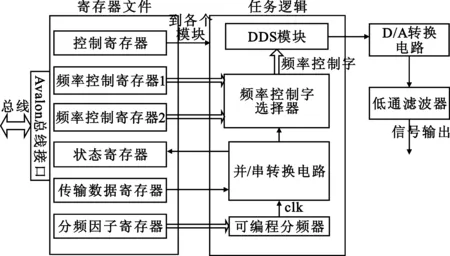

图1为本IP核的硬件设计结构框图,它主要由Avalon-MM总线接口、寄存器文件、任务逻辑、D/A转换电路和低通滤波器五大部分组成。

图1 硬件设计结构原理图Fig.1 Schematic diagram of hardware design

Avalon-MM总线接口是Nios II软处理器与调制器之间的通信接口,它满足Avalon-MM通信协议。寄存器文件由多个寄存器构成,用于寄存各种控制信息、状态信息和传输数据。任务逻辑完成调制参数可变的数字调制功能,是本设计的关键,它主要由可编程分频器、并/串联转换电路、频率控制字选择器和DDS模块组成。在本单元中,用一个可编程分频器来实现传输速率的可变功能:由图1可知,可编程分频器的输出信号作为并/串转换电路模块工作系统时钟,分频因子越大,得到的频率越小,并/串转换电路模块的转换速度越慢,波特率变得越小;相反,分频因子越小,得到的频率越大,并/串转换电路模块的转换速度越快,即波特率变得越快。因此,本调制器传输速度的变化是通过改变分频因子值来实现的。除此之外,并/串联转换电路还要根据当前所处的状态,修改状态寄存器的值:当并/串联转换电路正在转换时,状态寄存器被设为“忙”状态(设“1”电平),此时禁止Nios II 软核CPU对传输数据寄存器进行写操作;频率控制字选择器,可根据并/串转换电路送来的值(0或1)选择不同频率控制字,从而实现把“0”和“1”数字信号调制在不同的频率上。

3 数字调制器硬件设计

3.1 寄存器文件设计

为了保证Nios II处理器与任务逻辑之间能正常通信,在本IP核中要定义一组寄存器。这些寄存器寄存着调制器的控制信息、状态信息和传输数据。表1列出了这些寄存器的名称、相对地址、读写属性、位宽和功能描述等。

表1 寄存器组定义与地址分配Table 1 Definition of registers and address assignment

3.2 逻辑任务设计

3.2.1DDS模块设计[3-4]

DDS信号发生器模块也是本设计中最为关键模块之一,它能根据不同的频率控制字的值,合成不同的调制频率。图2为DDS模块的原理框图,主要包括相位累加器、相位寄存器、正弦波存储器。相位累加器完成累加操作,相位寄存器寄存累加结果,正弦波存储器存储了一个周期正弦数据信号。相位寄存器输出结果,一路作为累加运算的一个输入值,另一路作为正弦波存储器的地址值,正弦波存储器根据地址值,查找本存储器中相应地址单元的波形内容。在整个过程中,当相位累加器产生一次溢出时,DDS模块完成了一个周期输出任务。

图2 DDS模块组成原理图Fig.2 Schematic diagram of DDS module

频率控制字K与输出波形频率的函数表达关系式为

(1)

式中,K为频率控制字,N为累加器的位宽值。

3.2.2并/串联转换电路设计

并/串联转换电路除了完成对数据进行并/串联转换功能之外,还要产生握手信号,使Nios II软核CPU与并/串联转换电路之间的步调一致,防止数据丢失或重复传输。图3为利用硬件描述语言来设计本模块的算法流程图。在并/串转换之前,转换器首先判定状态寄存器的第1位是否有新的数据,如有,置状态寄存器第0位为“1”状态,禁止Nios II进行写入数据,然后再把32位的并行数据转换成串行数据,等到转换结束后,再分别置状态寄存器第0和第1位为“0”和数据“0”状态。

图3 并/串联转换电路模块的算法流程图Fig.3 Algorithm flowchart of parallel-series converting circuit

3.2.3可编程分频器设计

为了实现数字调制器传输的速率任意可调,在本设计中,还专门设计了可编程分频器。Nios II软核CPU按一定关系式把不同的传输速率转换成不同的分频因子,并把分频因子写到寄存器中。可编程分频器根据这个分频因子对系统时钟进行分频,得到不同频率(周期)的输出信号。因为分频器的输出作为并/串转换器的工作时钟,所以,不同的工作频率控制着转换器工作的快慢,从而能控制调制器传输速率的大小。

4 Avalon-MM总线接口设计

Avalon总线接口设计放在本IP 核的添加到SOPC Buidler[5-6]的IP库过程中进行。Altera公司SOPC Builder开发工具不仅允许设计者把自定义的IP核添加到SOPC Buidler的IP库中,还允许选择不同的总线接口类型。在本设计中选择了Avalon-MM总线接口。

5 软件设计

硬件系统工作离不开软件的支持,硬件系统的设计结构和工作原理决定了软件的编写方法。图4为本系统的软件算法流程图:首先启动并设置调制器的传输速率与载波频率;然后读取状态寄存器的第0位,只有在读到低电平“0”的情况下, CPU才把32位的数据写到传输数据寄存器中;最后设置状态寄存器的第1位为高电平“1”,启动转换电路工作。

图4 主程序的算法流程图Fig.4 Algorithm flowcharts of master program

6 验证结果

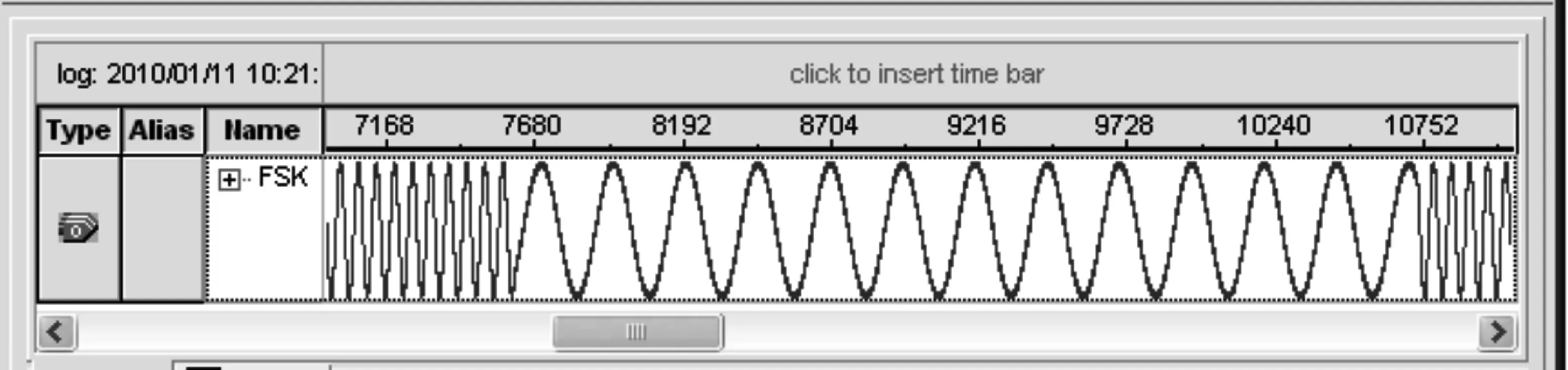

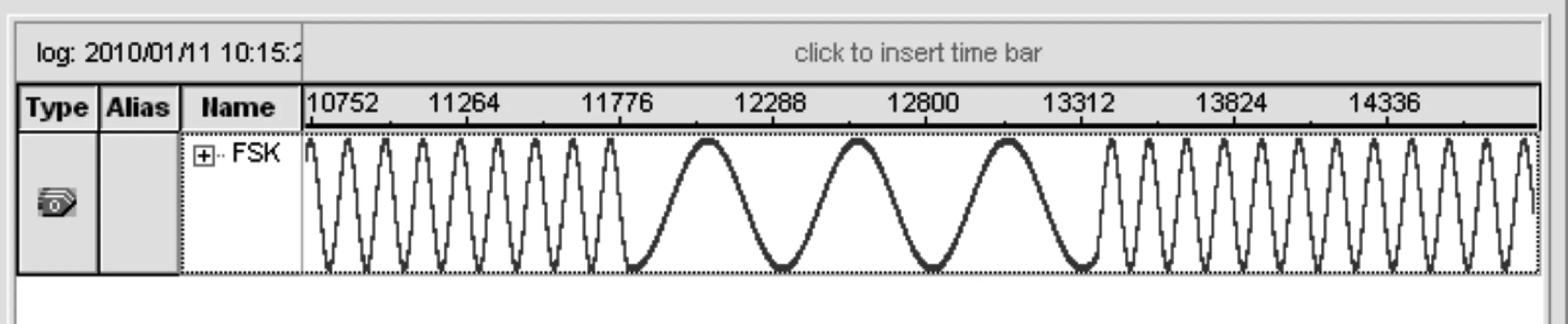

利用嵌入式逻辑分析仪(SigalTap II Logic Analyzer)对本设计进行验证。嵌入式逻辑分析仪是Quartus II软件自带的分析工具,它使用方便、便捷和灵活,可嵌入到设计单元中,直接观察被观察点的波形,完全可以代替数字示波器功能。图5为在嵌入式逻辑分析仪中观察到的波形图, FSK为调制输出信号,其中,图5(a)是载频分别为200 kHz和800 kHz、传输信息速率为8 000 bit/s的输出波形,图5(b)是载频分别为200 kHz和800 kHz、传输信息速率为16 000 bit/s的输出波形,图5(c)是载频分别为100 kHz和400 kHz、传输信息速率为16 000 bit/s的输出波形。从图中可以看出,无论是信息传输速率还是载波频率都变化了2倍:图5(a)与图5(b)的载波频率不变,而信息速率变化了2倍;图5(b)与图5(c)信息速率不变,而载波频率变化了2倍,验证了其正确性。

(a)载频分别为200 kHz、800 kHz,速率为8 000 bit/s的输出波形

(b)载频分别为200 kHz、800 kHz,速率为16 000 bit/s的输出波形

(c)载频分别为100 kHz、400 kHz,速率为16 000 bit/s的输出波形

7 结束语

本文介绍利用现场可编程门阵列(FPGA)器件设计波特率和载频均可变化的2FSK数字调制技术,利用直接数字频率合成器(DDS)来合成调制器的调制频率,通过修改DDS的频率控制字,控制调制频率变化,通过修改可编程分频器的分频因子,控制波特率的变化。实验结果表明,调制器具有较好的灵活性,可用于跳频通信的数字调制部分,具有一定的参考价值。

参考文献:

[1] 邱雅,李兵,肖乐. 基于DSP的2FSK实现[J].西华大学学报(自然科学版), 2009, 28(6):62-65.

QIU Ya,LI Bing,XIAO Le.Realization of 2FSK Modulation Based on DSP[J].Journal of Xihua University(Natural Science Edition), 2009, 28(6):62-65.(in Chinese)

[2] 吴海涛,梁迎春,陈英俊.基于FPGA的全数字FSK调制解调器设计[J].现代电子技术,2007,30(23):72-73.

WU Hai-tao,LIANG Ying-chun,CHEN Ying-jun.Design of Full Digital FSK Modern Based on FPGA[J].Modern Electronics Technique,2007,30(23):72-73. (in Chinese)

[3] 郭书军,谢定华,王玉花. 基于SOPC的DDS信号源的实现[J].电讯技术, 2005, 45(5):69-71.

GUO Shu-jun, XIE Ding-hua,WANG Yu-hua. Implementation of DDS Based on SOPC [J].Telecommunication Engineering, 2005, 45(5):69-71. (in Chinese)

[4] 杨秀增.基于FPGA和DDS的信号源设计[J].电子设计工程,2009,17(11):7-8.

YANG Xiu-zeng. Design of a signal generator based on FPGA and DDS[J]. Electronic Design Engineering, 2009,17(11):7-8. (in Chinese)

[5] 张福洪,肖怀锋,方洪灿,等.基于Nios II的UHF RFID读写器设计与实现[J].电讯技术,2009,49(5):25-28.

ZHANG Fu-hong,XIAO Huai-feng, FANG Hong-can,et al. Design and Implementation of UHF RFID Reader Based on Nios Ⅱ[J]. Telecommunication Engineering, 2009, 49(5):25-28. (in Chinese)

[6] 杨秀增.基于Nios II的自适应高精度频率计设计[J].自动化与仪表,2009(7):13-16.

YANG Xiu-zeng. Design of Equal Precision Digital Frequency Meter Based on NiosII[J]. Automation & Instrumentation, 2009(7):13-16. (in Chinese)