某机载雷达虚警的解决方法*

杨昌福,王 坚2,周敏琦

(1.中国西南电子技术研究所,成都610036;2.总参陆航部成都地区军事代表室,成都610036)

1 问题描述

某机载雷达设备在外场试飞的一次检飞过程中,发现设备存在虚警。进行了多次现场试验,先后排除了现场电磁环境、机上其它电子设备及其电缆等可能引入的干扰。

为进一步定位故障点,我们用备份雷达进行了对比试验,在相同的电磁环境中备份雷达未出现虚警。随后进行设备互换性试验,即用备份雷达的收发处理机和功率放大器分别替换装机雷达的相应部分,试验结果发现引起虚警的故障点位于装机雷达的收发处理机内部。

2 故障分析与定位

在排除了外部干扰和设备互换性试验验证的情况下,工作重点就放在装机雷达收发处理机内部进行故障分析和定位。

故障定位流程如图1所示。

图1 故障定位流程图

具体故障排查流程按照以下步骤进行:

(1)按照单元技术要求对收发处理机内部激励单元、接收机、本振源、控制单元、信号处理单元分别进行检查,对出现信号输出异常的单元做进一步的分析和故障定位,如表1所示。

表1 故障排查项目表

从表1中可以看出,激励单元、接收机、本振源、控制单元经过单独检测,没有发现故障。

(2)设备按照装机状态加电对外发射大功率微波信号,在接收端接收回波信号,按照系统信号流程对各单元的输出信号进行检测和分析,直到信号处理的FPGA数据输出。

在经过以上步骤的检查后,可以确定虚警问题最有可能来自信号处理部分,所以进一步的排查目标为信号处理部分。

在设备加电发射的情况下,我们分两步来分析隔离问题所在;第一步检测A/D采样后的雷达回波数据,第二步检测FPGA缓存打包之后的数据。

我们用VISUAL-DSP软件开发器对接收机I/Q信号经过AD采样后的数据进行读取和分析,未发现数据有失真的情况。在观察FPGA读取AD单元采样数据后并缓存打包后的数据时,发现目标检测单元中FPGA读取的数据不稳定:在同一距离单元的一个CPI内的数据存在跳变(正常情况下同一距离单元的数据相对稳定),数据跳变的位置不确定,数据跳变的次数约1~2次,这样的数据跳变可能会导致设备虚警,还要结合其它的分析结果进行证实。

图2为FPGA读取的数据产生跳变的瞬间图形。

图3为数据跳变后的原始频谱,可以看出,频谱在低速通道有较大的展宽。

图3 数据跳变后的频谱图

从图3中可以看到,低频端的谱线明显抬高,20频率通道以下的频谱抬高情况比较严重。在试飞试验中配置的协同目标,其速度频率基本上都是低于20频率通道的速度,设备为了能够检测到这些低速协同目标,只能将速度通道门限开得低于20,实际在第10速度通道左右,这样低端抬高的频谱分量也会进入下一级谱估计处理过程之中,会得出有目标的结论[1]。

经过以上分析,可以确定设备出现虚警问题的原因就是:装机雷达收发处理机信号处理部分FPGA数据跳变引起频谱低端展宽,在给定的试飞试验条件下,导致在雷达检测通道内形成虚警目标。

3 机理分析

3.1 信号处理部分基本工作原理

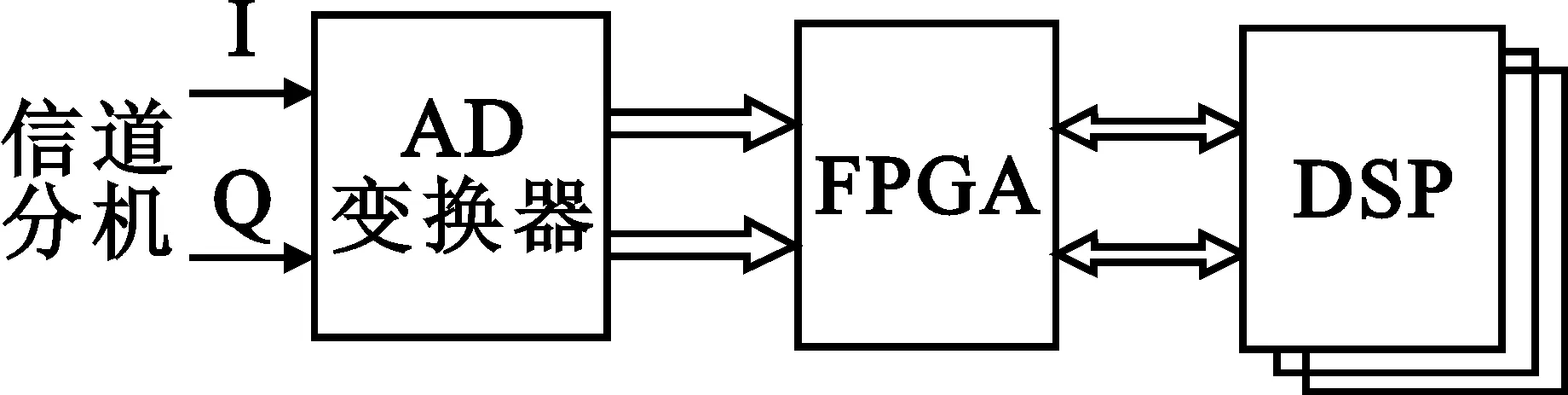

图4为信号处理简图,整个信号处理的工作流程是:A/D变换器把信道分机输出的I、Q正交视频信号由模拟信号变为数字信号,并把变换后的数据送到FPGA,并在FPGA内对数据进行预处理,把相加后的数据以DMA方式送到DSP,然后在DSP内对数据进行处理(如FFT、非相参积累、恒虚警处理、目标判决等),随后把目标参数传到FPGA进行缓存,最后接口控制部分把目标参数(包括目标方位、距离、速度和截击时间)传到外部系统[2]。

图4 信号处理框图

3.2 故障原因分析

如图4所示,雷达回波信号经过接收机处理,产生I、Q两路视频信号经AD单元变换后,送入动目标检测单元FPGA缓存打包,再通过DSP的链路口送入DSP进行处理,如果FPGA读取数据的时钟不稳定,在读取一个主触发信号周期的雷达回波数据时就会漏掉一个距离单元的数据,在进行数据矩阵转换的过程中使得数据错位而发生跳变。对发生跳变数据进行谱分析时,低频端的谱线会明显抬高(类似sinc函数),会导致雷达对低速目标检测的虚警率偏高。

可以判断: FPGA读数时钟的相关软件部分存在一定的不可靠性,使得该时钟有抖动的情况。一旦该时钟的抖动值超出了容限范围之外,就会发生漏读数据的情况,从而在后续的数据处理中出错,产生虚警。

4 验证/复现试验

4.1 验证试验分析

按照装机试飞状态对设备进行了全面检测,在信号处理板上加入了VISUAL-DSP开发器,用于检测FPGA读入的数据,并且可以实时观测到DSP频谱处理的结果。

图5为复现/验证试验测试框图。

图5 信号处理测试框图

在验证试验中,对FPGA读数时钟产生软件部分进行更改,对读数时钟信号做再锁定处理,提高读数时钟的稳定性,避免在读取一个主触发信号周期的雷达回波数据时漏掉一个距离单元的数据,使得DSP进行数据矩阵转换时数据不会因为错位而发生跳变,避免谱分析时低频端的谱线明显提高。

图6为实施读数时钟锁定处理后的FPGA读取数据。

图6 时钟锁定处理后FPGA读取数据图

以及实时观测到的数据频谱如图7所示。

图7 时钟锁定处理后的频谱图

从图6和图7可以看出,读数时钟经过再锁定处理之后,FPGA读出的AD数据不再有跳变,数据频谱也恢复正常值,同时终端屏幕上也没有再出现虚警。

4.2 复现试验

为验证故障定位的准确性和故障机理分析的正确性,以及采取的改进措施的有效性,我们将FPGA程序改回到未作更改的状态,进行故障复现,经再次加电验证,得到的结果和故障定位时一样,存在数据跳变,数据频谱有低频端扩展的情况。

5 结论

从以上验证试验和复现试验的结果可以看出,FPGA读数时钟信号抖动就是造成特定试验条件下雷达虚警的直接原因。为了消除这种不稳定带来的影响,我们对读数时钟信号产生进行了优化,加入信号锁定处理,消除信号的不稳定状态,解决了雷达虚警问题。

参考文献:

[1] Albert A Black.Pulse Doppler for Missile Approach Warning[J].Journal of Electronic Defense,1991,14(8):23-26.

[2] George Stimson.机载雷达导论[M].吴汉平,等,译.北京:电子工业出版社,2005.

George Stimson.Airborne Radar [M].Translated by WU Han-ping,et al.Beijing:Publishing House of Electronic Technology,2005.(in Chinese)