基于FPGA的电缆遥测系统接口电路设计

吴爱平李勇华

(1.长江大学电子信息学院 湖北荆州) (2.胜利油田钻井院 山东东营)

基于FPGA的电缆遥测系统接口电路设计

吴爱平1李勇华2

(1.长江大学电子信息学院 湖北荆州) (2.胜利油田钻井院 山东东营)

根据FPGA可编程技术具有功能集成度高,设计灵活,可靠性高的特点,提出了利用FPGA实现电缆遥测系统接口电路的方法,给出了FPGA设计的顶层图,并对设计进行了仿真。结果表明,使用该方法设计的电缆遥测系统接口电路结构简单,可靠性高。

FPGA;VHDL;电缆遥测系统

0 引 言

电缆遥测系统(CTS)是井下仪器与地面计算机测井系统之间的一种高速数据传输系统,它在计算机指令的控制下,进行数据的采集,格式编排和传输,每一帧上行数据与下行指令中均含有帧同步字FSP和循环冗余校验码CRC。因此,CTS不仅数据传输率高,而且遥测高度可靠。任何新设计的井下仪器只要增加一个标准接口,就可以与CTS匹配。随着电子技术的高速发展,可编程逻辑器件的广泛应用为数字系统的设计带来了极大的灵活性[1]。本文介绍一种基于FPGA的电缆遥测系统接口电路设计,利用VHDL语言编写程序来实现,提高了设计的可靠性和集成度。

1 CTS井下总线

CTS在井下采用了类似于计算机的体系结构,即在各井下仪器之间安排了三条串行总线,各井下仪器均与井下总线相连,每一井下仪器分别有规定的地址码,地面计算机向井下发送指令,指令中包含井下仪器的地址码和操作指令,井下仪器从指令中识别出自己的地址码后执行该指令,并把数据送至井下数据总线上。井下总线由下行信号线、上行时钟线和上行数据/启动线组成,下行信号线DSIG用来传送下行指令,从井下遥测单元至井下仪器单向运行,下行信号DSIG既含数据信息也含下行时钟信息,二者由井下仪器的总线接口电路分离;上行时钟线UCLK单向运行,井下仪器的数据在上行时钟UCLK的作用下逐位(串行)输出至上行数据线上。由于各井下仪器是顺序传送数据的,所以上行时钟线是按“菊花链”方式与各井下仪相连接。每帧开始时,上行时钟UCLK先送至第一个井下仪[2],当第一个井下仪器的数据送完后,UCLK送至第二个井下仪器,依次类推直至把最后一个井下仪器的数据送完为止;上行数据线/启动线UDATA/GO是双向运行的,每帧开始时,井下遥测单元通过UDATA/GO总线发出GO脉冲,通知各井下仪器,做好传送数据的准备,各井下仪器在上行时钟UCLK的作用下,依次把数据送至上行线上进行数据上传。

2 FPGA内部设计

本文设计的CTS接口电路以两支井下仪器的组合为例,井下仪器1的每帧数据量为64位,井下仪器2的每帧数据量为192位。每帧开始时,井下遥测单元发出GO脉冲,320μs后,井下遥测单元发出256个UCLK,UCLK的下降沿把井下仪器1的64位数据逐位选通到UDATA/GO总线上。第一个井下仪器的数据送完之后在控制电路的作用下,UCLK送至第二个井下仪器,直至把井下仪器2的数据送完。井下遥测单元下发的指令DSIG经信号分离后,分离出串行的数据信息和下行时钟,通过移位寄存器进行串并转换。FPGA器件选用ALTERA公司的FLEX10K10TC144,笔者在FPGA内设有四个模块:移位寄存器模块、延迟电路模块、比较器模块和时钟控制电路模块。FPGA中顶层设计框图如图1所示。DCLK为下行时钟,DDATA为下行指令,UCLK为上行时钟,UDATA为仪器上传的数据,GOP为启动脉冲。在下行时钟下利用移位寄存器将下发的指令解析出来,BIW高七位是仪器的地址码,BIW低八位是下发给相应仪器的指令,延迟电路模块是移位结束待数据稳定后再进行地址比较识别,以免出错。比较器模块用于地址识别,判断指令对哪支仪器操作。控制电路模块根据仪器的数据量控制菊花链的断开和接通,依次将各仪器的数据上传。

图1 FPGA顶层设计框图

3 软件设计

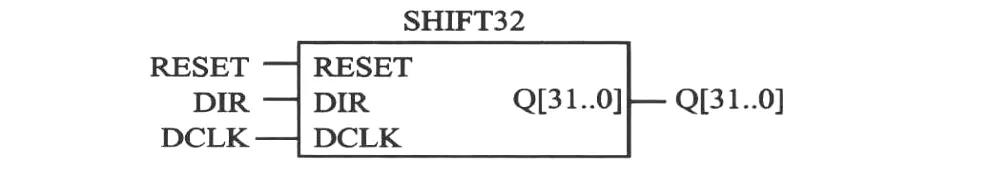

FPGA中移位寄存器模块、延迟电路模块、比较器模块和时钟控制电路模块程序采用VHDL语言编写,开发平台为MAXPLUSII。下面以移位寄存器模块为例讲述FPGA中的程序设计。RESET为系统复位信号,高电平有效,DIR为32位串行数据,DCLK为下发时钟,q[31..0]为移位数据输出。串行数据在DCLK作用下进行移位,程序结构体中使用一个进程,以DCLK为敏感信号,DCLK上升沿触发,移位寄存器模块生成的元件图如图2所示。FPGA顶层亦采用VHDL语言编写,利用元件例化语句,采用位置关联方式将移位寄存器模块、延迟电路模块、比较器模块和时钟控制电路模块进行有效连接,实现CTS的接口。

图2 移位寄存器元件图

4 结果分析

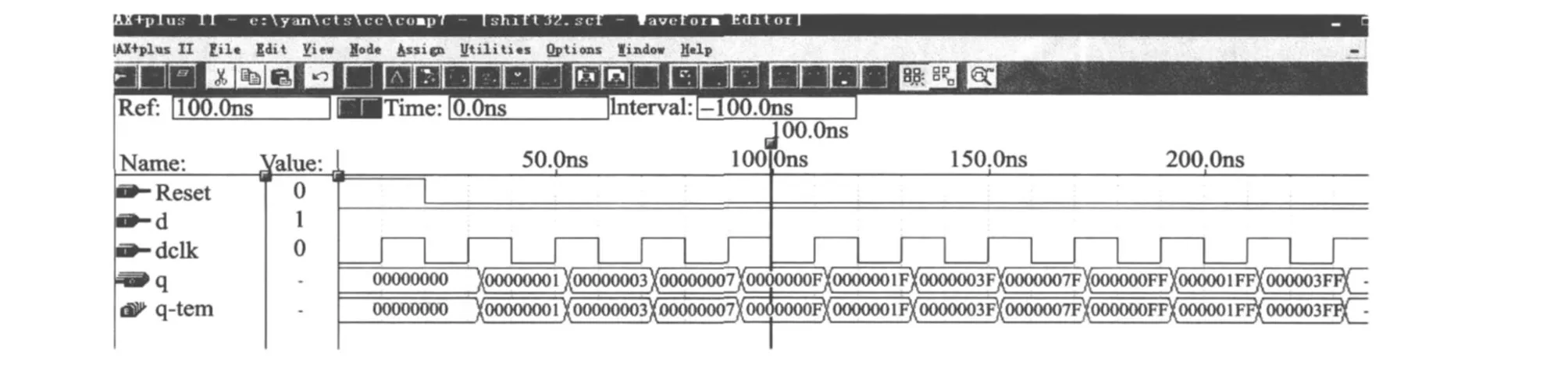

为确保设计的可行性,对各模块都进行了功能仿真和时序仿真。功能仿真只是从电路的功能上验证设计的正确性,电路中没有延时;而时序仿真能模拟实际电路中的器件延时,从而能进一步验证设计的正确性[3]。移位模块时序仿真波形如图3。从图中可以看到,Reset为高电平时,系统清零,q输出00000000H,共32位。当Reset为低电平,d一直保持高电平,dclk每来一个时钟,在时钟的上升沿将d的数据移入q,q的数据低位为1,高位移出,在100ns处,经过4个时钟后,q输出0000000FH,即q低4位为1111。通过该模块,下传指令就寄存到移位寄存器的可读输出端,将移位寄存模块的输出作为地址识别模块的输入信号,与井下仪器的地址码进行比较识别以及向井下仪器发送下传指令。

图3 移位功能模块仿真图

5 结束语

本设计采用自顶向下的系统设计方法,并采用VHDL语言输入,笔者自己定义器件的内部逻辑和管脚,将工作放在芯片的设计中进行,这样不仅可以通过芯片设计实现多种逻辑功能,而且增加了设计的灵活性、可靠性,缩短了开发周期,提高了效率。

[1] 刘雁飞,吴 进.基于CPLD的曼彻斯特编译码实现[J].西安:西安邮电学院学报,2003,15(1)

[2] 庞巨丰.测井原理及仪器[M].北京:科学出版社,2008

[3] 吴爱平,熊晓东.基于FPGA的测井信号分离卡的设计[J].石油仪器,2005,19(2)

TN914

B

1004-9134(2010)03-0090-02

2009-08-25 编辑:姜 婷)

吴爱平,男,1977年生,硕士,讲师,2000年毕业于江汉石油学院,现在长江大学电子信息学院主要从事信号采集与处理的教学和科研。邮编:434023