基于NiosII的DMA传输及调试

覃洪英

(长江大学电子信息学院 湖北荆州)

基于NiosII的DMA传输及调试

覃洪英

(长江大学电子信息学院 湖北荆州)

文章通过波码开关上的数据向SDRAM的DMA传输,介绍了基于NiosII进行DMA传输的过程及调试方法。在定制一个包含DMA控制器的SOPC系统时,需对DMA控制器硬件进行相关参数配置;在软件编程时需根据DMA传输中源地址和目的地址是外设和存储器的不同,分别选择开启发送和接收通道;在NiosIIIDE中加载μC/OS-II操作系统,指定了文件的存放路径,则可在文件中观察传输的数据。

NiosII;DMA传输;波码开关;SDRAM

0 引 言

在一般的程序控制传送方式(包括查询与中断方式)下,数据从存储器送到外设、或从外设送到存储器,都要经过CPU的累加器中转,再加上检查是否传送完毕以及修改内存地址等操作都由程序控制,要花费不少时间。采用DMA传送方式是让存储器与外设、存储器与存储器之间直接交换数据,不需要经过累加器,减少了中间环节,并且内存地址的修改,传送完毕的结果报告都由硬件完成,因此大大提高了传输速度。随着信息技术的发展,处理和传输的数据量越来越大,DAM传输在视频采集、处理和传输及通信等领域具有十分重要的应用价值[1]。

1 NiosII上的DMA传输

NiosII是Altera公司推出的第二代软核嵌入式处理器,除NiosII处理器外,Altera公司还提供了基于该处理器进行SOPC系统开发的串行接口核、三态桥、SRAM控制器、DM9000A网络控制器等标准外围设备。为满足大量数据的快速传输,Altera公司在SOPC Builder中还提供了DMA控制器核。同时,为了方便用户编程,NiosIIIDE还在HAL中为用户提供了包括DMA控制器等标准外设的驱动程序。基于这些外围设备或自定制外设,则可进行SOPC系统开发,以实现视频控制、网络控制、DMA传输等功能[2、3]。

1.1 SOPC系统配置

在SOPCBuilder中定制包含DMA控制器的SOPC系统,添加NiosIICPU、添加连接片外8MSDRAM的SDRAM控制器、连接片外4Mflash的cfi-flash控制器、系统标识符sysid、实现PC和NiosII系统间串行通信的调试接口jtag_uart、通用异步收发器uart、系统定时器time_0和 time_1、连接cfi_flash控制器的 tristate_bridge及发光二极管、拨码开关switch_pio等常用的标准外围设备。

DMA控制器通过2个主端口和1个从端口来控制DMA传输。从端口为Avalon从端口,负责与Avalon总线通过地址线、数据线、控制线、中断等相连接;2个主端口为主设备读端口和主设备写端口,负责DMA传输的数据读/写操作。

在SOPCBuilder中添加DMA控制器核,使用DMA控制器配置向导。硬件配置的参数如下:

①DMA长度寄存器 该参数值可选范围为1~32位,表示单次DMA传输数据的最大值。这里可以使用缺省值32位,即满足所有从外设的传输要求。

②主设备读/写端口间的FIFO缓冲器实现方式

考虑到如使用从寄存器构建FIFO,当DMA控制器数据宽度较大(如32位)时,将对逻辑资源的占用有很大影响。因此选择从存储块来构建FIFO,由FPGA中的嵌入式存储块实现。

③DMA硬件支持的数据传送宽度 在DMA传输中,根据需要选择合适的传输宽度,没有必要进行其他数据宽度的传输,因此在配制向导的Advanced选项卡中勾选需传输的数据宽度,禁止其他数据宽度的传输,这样可以节省逻辑资源。

这里考虑利用DMA传输将波码开关上的数据传输到SDRAM,以观察DMA的传输过程。故在SOPC Builder中需将DMA的read_master连接到switch_pio;将DMA的write_master连接到sdram。整个SOPC硬件系统的系统时钟是100MHz,SDRAM时序要求将DE2所提供的50MHz时钟延时3ns或者相位延迟60°处理之后作为 SDRAM的时钟输入DRAM_CLK。这个时钟延迟可以用锁相环产生。

1.2 数据的DMA传输

DMA传输不需要CPU的参与,源和目标可以是内存也可以是设备,在NiosII中通过基于 HAL编程完成,即三种基本的DMA传输:设备到存储器传输、存储器到存储器的传输和存储器到设备的传输。

在NiosII的HALDMA设备模式中,DMA传输被分为两类:transmit和receive。NiosII提供两种设备驱动实现transmitchannels和 receivechannels。transmit channels把缓冲区数据发送到目标设备,receivechannels读取设备数据存放到缓冲区。

在数据从源地址到目标地址的传送中。对于地址的操作方式,一种是地址自增,另一种是地址固定。就是说DMA控制器读或写完一个数据后,对地址增加模式,下次读写下一个地址;对地址固定模式,下次还是读写同一个地址。由于地址固定模式一般是用在外设,所以在Nios的文档中,使用地址固定模式的一方就称为设备(Peripheral),而使用地址自增模式的一方则称为存储器(Memory)。

在HAL的API中,对于地址自增一方,需要打开一个接收或发送的Channel,然后配置地址;而如果是地址固定的一方,则不需要打开一个Channel,只需要用alt_dma_rxchan_ioctl()的ALT_DMA_RX_ONLY_ON 或ALT_DMA_TX_ONLY_ON参数设置,并配置地址即可。

2 DMA传输的调试和分析

2.1 调试过程和方法

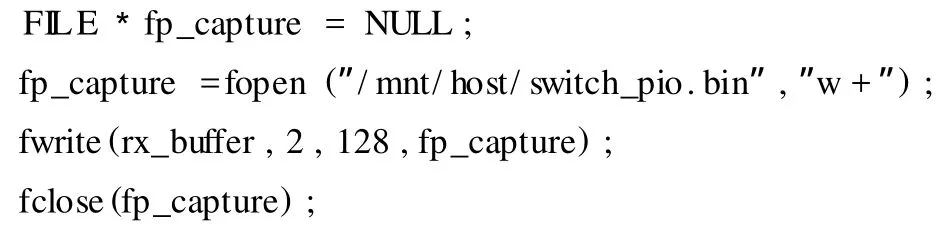

将波码开关上的数据通过DMA传输到SDRAM的过程属于设备到存储器的传输,应用程序的设计需要打开DMA设备、开启DMA接收通道、发送接收请求,从而实现波码开关上的数据通过DMA设备向SDRAM的传输。为了观察传输到SDRAM的数据,这里在NiosⅡIDE的文件系统属性设置中加上μC/OS-Ⅱ操作系统[4]。当指定大小的数据传输完成后,可以利用μC/OS-Ⅱ操作系统的文件管理系统将SDRAM中的数据以二进制的形式写到指定的文件中。要完成此功能,需在NiosⅡIDE中按图1对指定文件的挂载点进行设置,然后在应用程序代码中增加如下语句:

最后利用相关的软件(如WinHex)打开 switch_pio.bin文件,则可观察到传输数据的十六进制形式。

图1 读写文件的位置设定

2.2 调试结果分析

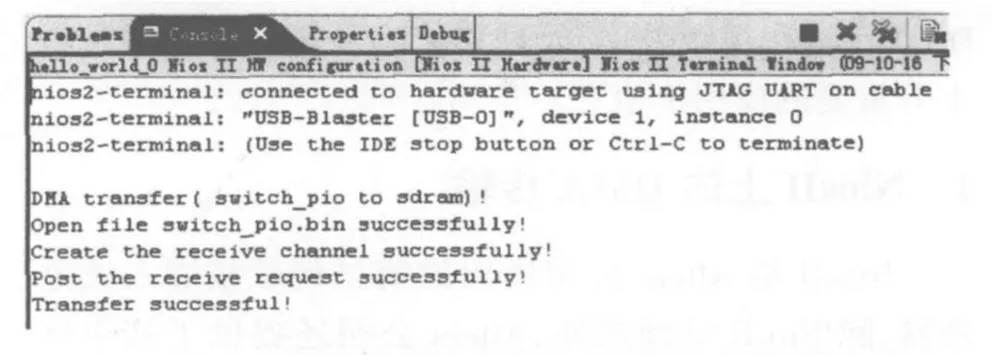

图2 所示是在μC/OS-II操作系统下控制波码开关上的数据通过DMA向SDRAM传输的应用程序调试结果,从运行结果可看到,DMA接收通道已成功开启,且存储在SDRAM中的数据已成功写入到switch_pio.bin文件中。根据图1所示读写文件的挂载点可知,switch_pio.bin文件与应用程序在同一路径下。

图2 μC/OS-II操作系统下波码开关数据通过DMA向SDRAM传输的软件调试结果

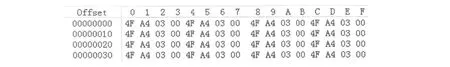

DE2开发板上波码开关SW17~SW0设定的数据是11_1010_0100_0100_1111,系统调试后,在WinHex软件中打开switch_pio.bin文件,观察到图3所示数据,比较可知图3中的数据与波码开关的初始设定值完全一致。这说明波码开关上的数据到SDRAM的DMA传输成功,且数据传输正确。

3 结 论

图3 switch_pio.bin文件中的数据

在NiosII上使用DMA可实现海量数据的嵌入式处理,在模式识别、视频控制等领域中具有重要的应用价值。基于NiosII的DMA传输根据源地址和目的地址是外设和存储器的不同,分外设到存储器、存储器到外设和存储器到存储器三种传输方式。外设到存储器的传输需开启接收通道,存储器到外设的传输需开启发送通道,存储器到存储器的传输既要开启发送通道,又要开启接收通道。利用QuartusII中的逻辑分析仪可观察到DAM传输数据的波形,要将传输的数据写入文件,通过打开文件来观察更多的数据,则需要在NiosIIIDE中加载μC/OS-II操作系统,并指定文件的存放路径。

[1] 刘乐善.微型计算机接口技术及应用[M].武汉:华中科技大学出版社,2000

[2] 周立功,等.SOPC嵌入式系统基础教程[M].北京:北京航空航天大学出版社,2006

[3] 杨 进,邱兆坤.SOPC中自定义FIFO接口与DMA数据传输[J].单片机与嵌入式系统应用,2008,(8)

[4] Altera.NiosIISoftwareDeveloper′sHandbook[DB/OL].May2008.http://www.Altera.com

TN919.6

B

1004-9134(2010)03-0087-03

2009-10-21 编辑:刘雅铭)

覃洪英,女,1979年生,硕士,讲师,长江大学电子信息学院工作,主要研究方向:视频通信。邮编:434023