基于MATLAB和Dsp Builder的电网信号FIR滤波器设计

葛远香, 胡开明

(东华理工大学,江西抚州 344000)

基于MATLAB和Dsp Builder的电网信号FIR滤波器设计

葛远香, 胡开明

(东华理工大学,江西抚州 344000)

针对FIR数字滤波器的基本原理和结构特点,利用DSP Builder技术,将MatLab/Simulink设计工具和QuartusⅡ有效的结合起来,根据电网谐波分析的要求设计了64阶低通FIR滤波器,对该滤波器的性能进行了仿真,并将设计下载到FPGA中进行了硬件测试,测试结果表明:采用该方法设计FIR滤波器简单易行,可缩短设计进程,设计出的滤波器的性能稳定可靠,达到了预期目标。

FPGA;DSP Builder;MATLAB工具箱;FIR数字滤波器

根据“电能质量,公用电网谐波”国家标准(GB/T14549),当谐波电压幅值小于基波幅值的3%时,测量误差要求小于基波幅度的0.15%,这就要求抗混叠滤波器的通带波动小于0.15%,并且阻带衰耗要大于60 dB。对于这样的性能指标,模拟滤波器很难实现。所以本文采用FPG A/CPLD设计来实现数字滤波器。基于快速发展的大规模可编程器件和EDA技术,用硬件实现数字滤波器,有效地克服了传统DSP技术中的诸多技术瓶颈,在高速与实时性、高可靠性、系统的重配置与硬件可重构性、单片系统的可实现性及自主知识产权化等许多方面显示了突出的优势。按照Matlab/Simulink/DSP Builder/QuartusⅡ流程,设计一个FIR滤波器。

1 数字滤波器简介

1.1 数字滤波器选择

系统希望滤波器具有线性相位的特性,因此,在滤波器通带内的信号通过滤波后,除了由相频特性的斜率决定的延迟外,可以不失真地保留通带以内的全部信号。而FIR(有限冲激响应)滤波器具有精密的线性相位,同时又可以具有任意的幅度特性。并且FIR滤波器的单位抽样响应是有限长的,因而滤波器是稳定的(刘波,2006)。所以本设计选择FIR数字滤波器。

1.2 FIR滤波器的基本原理

FIR滤波器的传递函数为:

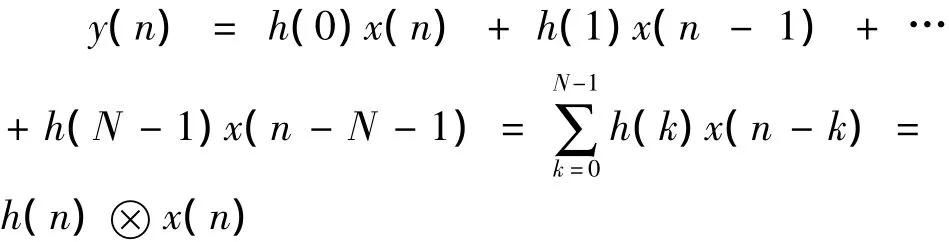

可得FIR滤波器的差分方程为:

因此,FIR滤波器又称为卷积滤波器。其中:k是FIR的滤波器的抽头数;h(k)是第k级抽头数(单位脉冲响应);x(n-k)是延时k个抽头的输入信号。FIR滤波器不断地对输入样本x(n)延时后,再作乘法累加算法,将滤波结果y(n)输出,因此,FIR实际上是一种乘法累加运算。在数字滤波器中,FIR滤波器的最主要的特点是没有反馈回路,故不存在不稳定的问题;同时,可以在幅度特性是随意设置的同时,保证精确的线性相位。稳定和线性相位特性是FIR滤波器的突出优点(程佩青,2006)。

2 FIR数字滤波器的DSP Builder设计

2.1 窗函数的选择和阶数的计算

使用DSP Builder可以方便地在图形化环境中设计FIR数字滤波器,且滤波器系数的计算可以借助Matlab强大的计算能力和滤波器设计工具完成(潘松,2004)。根据本系统的谐波要求需要保证19次谐波以下谐波的平直特性,另外为了能对滤波后的信号进行重抽取,应该滤除32次以上谐波成分。这样选定第 20-32次谐波点(1000Hz-1600Hz)为过渡带,由此可得FIR滤波器的设计指标:通带截止频率:fp=1000 Hz;阻带截止频率;fs=1600 Hz;采样频率:Fs=6400 Hz;阻带最小衰减α≥60 dB;根据阻带衰耗指标,选布莱克曼窗(李凌冰,2008);过渡带宽 B=ws- wp=0.1875π,根据布莱克曼窗的过渡带宽可计算出阶数N=12π/B=64。

采用Matlab的FDAtool确定FIR滤波器的系数(张登奇,2007)。该低通滤波器要求阻带最小衰减大于60dB,所以采用布莱克曼窗函数方法设计。FDATOOL计算出的值是一个有符号的小数,而DSP Builder下建立的FIR滤波器模型需要一个整数作为滤波器系数,所以必须进行量化,并对得到的系数进行归一化(王春玲,2009)。根据给定的误差指标决定系数量化的字长。得到64个整数系数。如图1所示:

图1 Matlab命令窗口中量化后的系数Fig.1 the quantized coefficient in matlab command window

2.2 FIR滤波器模型设计

滤波器的硬件模块是基于DSP builder进行设计的(罗韩君,2009)。在 Matlab/Simulink中完成设计输入,即在Matlab/Simulink环境中建立一个mdl模型文件,用图形方式调用Altera DSPBuilder和Simulink库中的其它模块(Block),构成系统级或算法级设计框图。本系统设计的64阶FIR数字滤波器可由8阶FIR数字滤波器构成,首先在DSPBuilder中设计一个直接I型的8阶 FIR滤波器(Altera,2003),把设计的8阶FIR滤波器作为一个子系统,然后在64阶滤波器设计中直接调用,组成一个直接I型的64阶FIR滤波器系统。并把前面算好的系数添加到本次滤波器中,如图2所示:

完成模型设计后,在Matlab的Simulink环境下,直接I型FIR滤波器的仿真波形如图3所示,输入一个3000Hz和100Hz的混合波,图3中示波器显示的波形,上方是输入FIR滤波器的波形,下方是FIR输出的波形,可以看到具有良好的滤波作用,达到了系统的要求。

在Matlab中仿真验证达到要求后,就需要把设计转换到硬件上加以实现,通过DSPBuilder可以获得针对特定FPGA芯片的HDL代码。

3 在FPGA器件中实现FIR滤波器

由于Simulink建模仿真使用的输入正弦波都是仿真信号,而不是实际的信号源。在硬件实际运行时,可以从外部信号源接入芯片内部或者在芯片内部存储正弦波的数据。本设计采用的是后者,即在顶层文件中引入LPM_ROM宏模块,在其中存入正弦波数据的mif文件(存储初始化文件),FIR滤波器模块直接从ROM中读取数据,经过滤波处理之后数据存入另一ROM中,可以通过 In_system_工具从中读出数据,再利用Matlab还原出波形,从而在实际硬件中验证了滤波器的功能。实现的顶层电路如图4所示。

图2 64阶FIR数字滤波器的模型图Fig.2 64 -order FIR digital filter model diagram

图3 滤波器的仿真波形Fig.3 Simulation waveform filter

4 总结

设计实践表明,在进行电网信号的FIR滤波器设计时,利用matlab的fdatool工具箱和DSP Builder可以简化计算与设计难度,加快设计速度,灵活选择精度,模块化的设计方法使设计简单易行,避免了繁琐的VHDL语言编程,使仿真验证过程变得尤其简单。

图4 FIR滤波器的顶层图Fig.4 top-level figure of FIR filter

程佩青.2006.数字信号处理教程 [M].北京:清华大学出版社.

李凌冰,徐娅萍,李蒙,等.2008.基于 MAT LAB的测控系统滤波器设计[J].中国制造业信息化,37(3).

刘波.2006.MATLAB信号处理[M].北京:电子工业出版社.

罗韩君,刘明伟.王成.2009.基于DSP Builde的FIR滤波器设计与实现[J].微计算机信息,(25):148-149.

潘松,黄继业,王国栋.2004.现代DSP技术[M].西安:西安电子科技大学出版社,

王春玲,王蒙.2009.基于 FPG A和 DSP Builder的FIR滤波器设计[J]泰山学院学报,31(3):99-103.

张登奇,李望移.2007.基于MATLAB的FIR数字滤波器的设计[J].计算机时代,(11):47-49.

Altera Corporation.2003.DSP Builder reference manual.

The FIR Filter Design of Power Signal Based on Matlab and Dsp Builder

GE Yuan-xiang,HU Kai-ming

(East China University of Technology,Fuzhou,JX 344000,China)

According to the principle and structure of FIR digital filter,using dspbuilder technology,make Matlab/Simulink design tools and QuartusⅡto effective combination,according to the requirements of Harmonics A-nalysis to design a 64 - order lowpass FIR filter.Finally,the design is downloaded into FPGA device for testing,testing results indicate:this design method is effective for FIR.

FPGA;DSP Builder;MATLAB Toolbox;FIR digital filter

TN713

A

1674-3504(2010)02-197-04

10.3969/j.issn.1674-3504.2010.02.016

2010-01-19

东华理工大学校长基金项目“基于SOPC的电能质量在线分析仪的研制”(DHXK0920)

葛远香(1978—),女,河南人,主要研究方向:嵌入式控制的研究与应用。E-mail:yxge@ecit.edu.cn