基于DSP开发工具的自适应滤波器

杨 东,王建业,蔡 飞

(空军工程大学导弹学院,陕西三原 713800)

0 引言

随着数字超大规模集成(VLSI)技术的发展,自适应信号处理技术在许多领域(例如:数字通信、雷达、生物医学、地震学、导航系统等)得到了广泛应用。传统上自适应信号处理是基于DSP处理器实现的,但其固有的缺点无法满足高速、实时系统的要求,而利用FPGA实现自适应信号处理能够很好地解决并行性和速度问题以及改善系统的抗干扰能力。传统上,自适应滤波器的FPGA实现主要是采用VHDL或者Verilog HDL等硬件描述语言通过编写代码来实现的,这种方式开发效率低,难度比较大,也不便于仿真观察。而DSP Builder工具则能更好地满足开发要求。

1 主要技术与工具

DSP Builder作为Matlab的Simulink工具箱,是基于FPGA的DSP开发工具,它支持系统、算法和硬件设计共享一个公共开发平台,在算法友好的开发环境中帮助设计人员生成DSP设计硬件表征,从而缩短了 DSP设计周期。设计人员可以使用DSP Builder模块迅速生成Simulink系统建模硬件。

Altera可编程逻辑器件(PLD)中的DSP系统设计需要高级算法和 HDL开发工具。Altera的DSP Builder将Matlab和Simulink系统级设计工具的算法开发、仿真和验证功能与QuartusⅡ的综合、仿真以及Altera开发工具整合在一起,实现了这些工具的集成。

在DSP Builder的开发过程中,可以运用硬件回环(Hardware in the Loop,HIL)仿真,它是将软硬件技术结合在一起的综合仿真系统。HIL仿真被证明是一种有效的仿真验证解决方法,该技术能确保在开发周期早期就完成嵌入式软件的测试,到系统整合阶段开始时,嵌入式软件测试就要比传统方法做得更彻底更全面,这样可以及早地发现问题,因此降低了解决问题的成本。

2 DLMS自适应滤波器的算法概述

自适应滤波器经近40年的发展,形成了多种准则下的自适应滤波理论。然而,1969年由Widrow和Hoff提出的LMS算法,因其具有计算量小、易于实现等优点而在实践中被广泛采用,并且几乎适用于所有场合,尤其在回声抵消、信道均衡、噪声对消等应用中处于绝对的统治地位。其基本思想是调整滤波器的权值参数,使滤波器的输出信号与期望信号之间的均方误差最小。LSM算法通过以下迭代式来描述:

式中,x(k)表示第k时刻输入信号向量,d(k)为第k时刻的输入期待信号,即参考输入,e(k)和y(n)分别为误差信号和滤波器的输出,w(k)表示第k时刻权系数向量,N和μ分别为滤波器阶数和迭代步长(影响LMS算法失调量和收敛速度的主要参数)[1]。

采用自适应LMS算法滤波器结构如图1所示。

图1 LMS自适应FIR滤波器结构Fig.1 The structure of LMSadaptive FIR filter

然而,LMS自适应滤波器的系数更新路径比较长,从迭代公式和滤波器结构中可以看出权系数更新必须在输出信号y(k)与误差信号e(k)计算完毕以后才能进行。换言之,以上步骤含有一种顺序关系,权系数的更新与滤波(y(k)的计算)不能同步进行。对于高速信号处理,这种串行的算法不能满足要求。并行的流水线结构是高速设计中的一种常用手段,这种方法是在时序电路中通过插入寄存器将较长的更新过程划分成较小模块,从而实现提高系统工作频率的目的[2]。

相对于LMS算法,DLMS算法的权系数更新模块采用延迟了D个节拍的数据来产生下一时钟周期的权系数,本设计中权系数更新延迟了6个周期。引入延迟的好处在于可以用前一时间的误差值来实现更新,在时钟的驱动下,系数更新和误差计算可以同时进行。DLMS算法权系数更新方程可以用下式表示:

DLMS算法权系数更新中延时D的引入对算法的稳态行为影响不大,关键问题是步长因子 μ的选取。DLMS算法的收敛条件相对于LMS算法的收敛条件DLMS算法收敛条件更为苛刻[3]。

3 基于DSP Builder工具的延时最小均方自适应滤波器

DSP Builder是 Altera公司推出的一个面向DSP开发的系统级(或算法级)设计工具,它架构在多个软件工具之上,并把系统级(算法仿真建模)和RTL(硬件实现)两个涉及领域的设计工具连接起来,作为Matlab的一个Simulink工具箱出现,可以在Simulink中进行图形化设计和仿真,同时又通过Signal-Compiler可以把Simulink设计文件(.mdl)转成相应的硬件描述语言 VHDL(.vhd),DSP Builder可以很方便地帮助设计者完成基于FPGA的DSP系统设计的整个流程[4]。

本文设计了一个16阶系统辨识自适应滤波器,输入信号x(k)、输出信号y(k)与误差信号e(k)均用16位二进制符号数表示。图2给出了16阶DLMS自适应FIR系统辨识顶层设计构造图。

为了构造完整系统,观察设计效果,此处设计了一个16阶直接型FIR低通滤波器作为未知系统(辨识对象)。根据文献[5]所提出的定点数L阶FIR滤波器的动态范围级数G的最坏情况计算公式:总位宽应是输入位宽和级数G之和,由此可确定滤波器内部运算位数最少应为16+3共19位。本设计对滤波器输出信号采用了缩放,采用16位输出。同时为了减少资源的消耗并提高速度,步长的选择放弃了乘法器,而是采用移位的方法实现,将误差信号向右移一位,结合输出信号的缩放,相当于系统采用模块化设计,将权系数更新模块封装成一个子系统cofe(见图3),便于调用,结构清晰。

图2 16阶DLMS自适应FIR系统辨识顶层设计Fig.2 Top level design of 16-taps adaptive FIRfilter

图3 子系统Fig.3 Subsystem

此处,在权系数更新时对输入信号额外延迟了6个周期,即DLMS权系数更新方程的具体实现。特别要提出的是权系数更新延迟时间的确定是不断经过试验得出的,对于滤波器阶数不同延迟时间也不同[6]。

4 DLMS自适应滤波器的硬件回环(HIL)及QuartusⅡ仿真测试

硬件回环(HIL)仿真是将软硬件技术结合在一起的综合仿真系统,其最大优点在于利用硬件系统能够提高仿真速度,直接检测硬件运行效果,并且可以充分利用软件提供的各种仿真源作为信号源。硬件平台选择了Altera公司出品的DE2开发板(CycloneⅡ系列 EP2C35F672C6芯片),通过 USBBlaster下载电缆,以JTAG模式的方式直接下载到开发板中,运行数据又通过JTAG接口返回到计算机显示,HIL系统结构如图4所示,信号源选择了线性调频信号,这样低通滤波的效果可以很容易地观察出来。

图4 DLMS自适应滤波器HIL结构图Fig.4 The HIL figure of DLMS adaptive filter

图5 是经过HIL回环系统的仿真波形图,图中第1行为DLMS滤波器输出,第2行为误差信号,第3行为输入线性调频脉冲压缩信号,第 4行为FIR低通滤波器输出。可以清楚看出,经过大概150步(约5μs)以后,误差信号基本上收敛,而 DLMS自适应滤波器也成功学习FIR低通滤波器,两者输出基本一致。

图5 HIL仿真波形图Fig.5 The HIL simulation wave figure

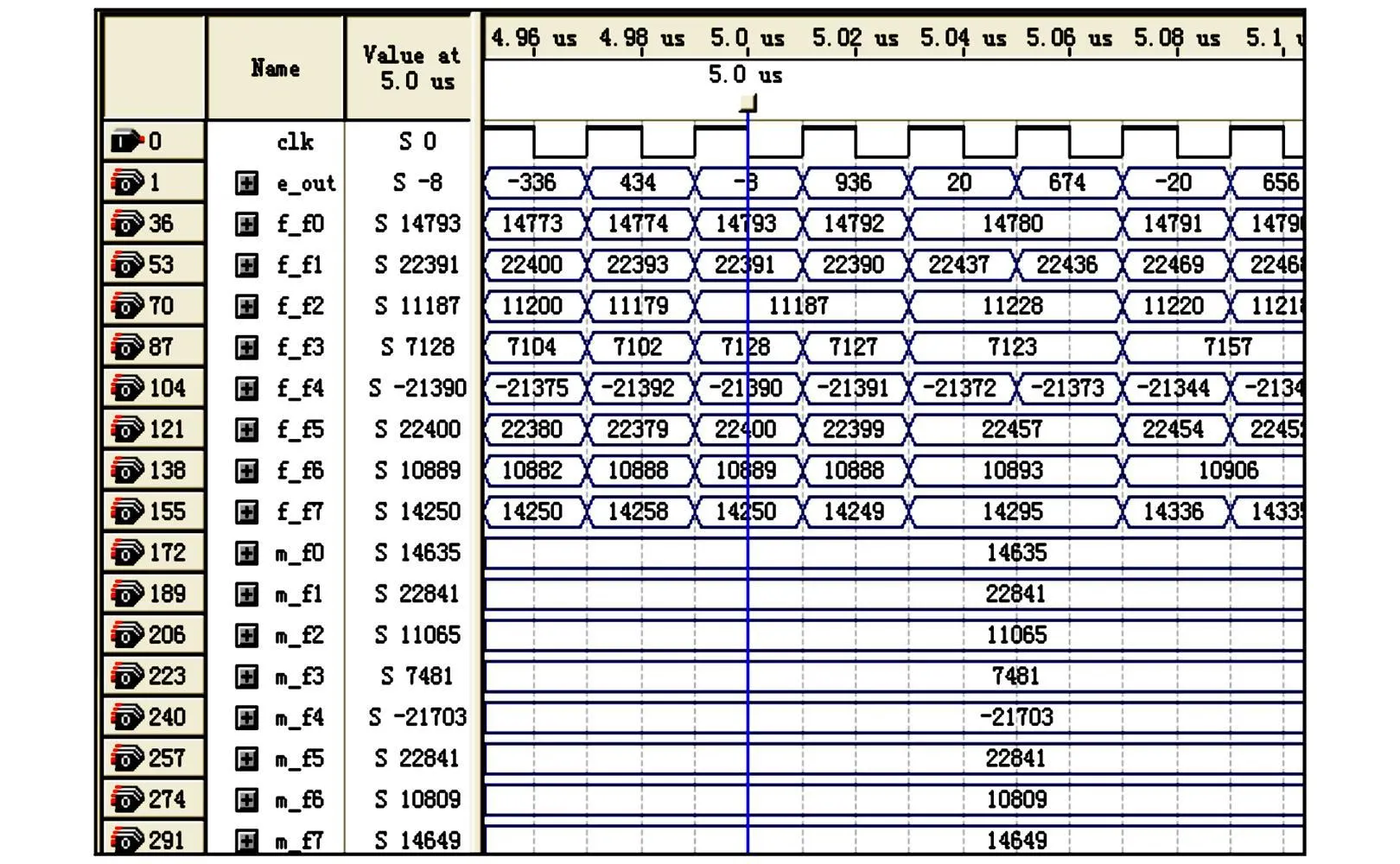

系统成功进行仿真以后,运行Singal Compiler创建QuartusⅡ工程,进行综合、编译和适配,最终生成编程文件(即.pof文件和.sof文件)下载到FPGA芯片中去。本文为了观察资源消耗情况,最终在QuartusⅡ中完成综合、编译、适配和下载(在QuartusⅡ中仿真结果如图6所示)。在程序成功仿真以后,在QuartusⅡ仿真资源列表中可以看到:耗费资源为6 301个logic elements,1 576个logic registers,系统最高工作频率达到82.07 MHz。由此可以看出DLMS自适应滤波器数据吞吐量已经达到较高水平。

图6 QuartusⅡ仿真结果Fig.6 The simulation results In quartusⅡ

5 结论

最大限度地提高开发效率和节约成本是开发者不懈追求的事情。本文利用Matlab的Simulink工具箱DSP Builder设计出了基于延时最小均方算法的自适应滤波器,仿真与测试结果表明设计的正确性,并在CycloneⅡ系列FPGA芯片上完成了硬件验证,滤波器最高频率达到82.07 MHz,数据吞吐量显著提高。事实证明,DSP Builder工具箱可以很明显地提高数字信号处理系统的开发效率,具有较高的应用价值。

[1]Paulo SR diniz.自适应滤波算法与实现(第二版)[M].刘郁林,景晓兵,谭刚兵,等,译.北京:电子工业出版社,2004.

[2]Ejaz Mahfuz,Wang Chunyan,Omair M.A high-throughput DLMS adaptivealgorithm[J].IEEE Trans on Circuits and Systems,2005,23:871-875.

[3]Long GuoZhe,Ling FuYun.The LMS Aglorithm with Delayed Coef ficient Adaptation[J].IEEE Trans on A-coustics,Speech,and Signal processing,1989,37:1 397-1 405.

[4]潘松,黄继业,王国栋.现代 DSP技术[M].西安:西安电子科技大学出版社,2003.

[5]Uwe Meyer-Baese.数字信号处理的FPGA实现[M].刘凌,译.北京:清华大学出版社,2003.

[6]刘雄飞,高金定,齐海兵.LMS自适应滤波器FPGA实现的新方法[J].压电与声光,2007(1):23-26.LIU Xiongfei,GAO Jinding,QI Haibing.A new way of theimplementation of LMSadaptive filter based on FPGA[J].Piezoelectrics&Acoustooptics,2007(1):23-26.

——信号处理