基于DVB-H标准的RS译码器算法与FPGA实现

周国良,王波

(1.中国船舶重工集团公司江苏自动化研究所,江苏连云港222006;2.哈尔滨理工大学,黑龙江哈尔滨150001)

RS码是一类具有很强纠错能力的多进制BCH码,也是典型的代数几何码,最初由里德(Reed)和索罗蒙(Solomon)于1960年构造出来。由于其具有很强的纠正随机错误和突发错误的能力以及极低的不可探测差错率,所以在数字视频广播、军用通信、卫星通信、计算机通信、存储介质等领域得到广泛的应用[1]。

DVB-H标准是在DVB-T标准基础上针对移动手持终端的数据和多媒体服务而制定的新一代数字地面广播标准。它将电视广播、移动通信及互联网IP技术相结合,可开展移动手机电视业务。为了使数字节目在传输过程中避免出现因受到各种信道噪声干扰而出现失真的现象,DVB-H标准采用了包括RS码在内的多种编码技术来保护传输数据。其中,RS(204,188)码被用作为DVB-H标准的外码解决方案。本文将针对DVB-H标准规定的RS(204,188)码给出译码算法分析、基于FPGA的译码器实现以及译码器性能的仿真与测试结果。

1 RS(204,188)码及译码算法

1.1 RS(204,188)码参数

RS(204,188)码是在有限域GF(28)上运算得到的,属于RS(255,239)的缩短码。根据DVB组织发布的《手持终端传输系统(DVB-H)》[2]规定,其具体参数如下:

(1)m=8,m为每个符号的位数;

(2)n=2m-1=204,n为一个码字包含的符号个数;

(3)k=188,k为一个码字中信息位符号个数;

(4)2t=n-k=16,2t为一个码字中校验位的符号个数;

(5)t=8,t为一个码字内所能纠正的最大错误符号数;

(6)GF(28)域上的本原多项式为:

(7)码生成多项式为:

1.2 译码算法

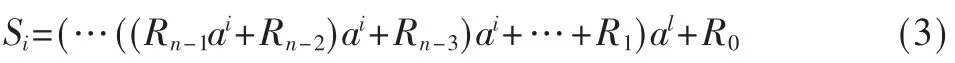

(1)伴随式计算,由接收到的码字R(x)计算伴随式S(x);

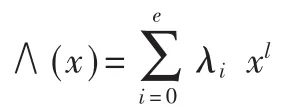

(2)求解关键方程,确定错误位置多项式∧(x)和错误值多项式Ω(h)(x);

(3)计算错误位置和对应错误值,确定E(x)。由C(x)=R(x)-E(x)计算译码器输出码字C(x)。

译码器的实现框图如图1所示。

其中第(2)步求解关键方程是决定译码器复杂程度与速度的关键。常见的关键方程求解算法主要有Euclidean算法、BM算法及其改进形式。BM算法译码延时较Euclidean算法小,实现电路较简单,所以在工程中较为常用。针对传统BM算法需要进行求逆运算的不足,Blahut和Berlekamp分别提出了无需求逆的BM算法,即iBM算法。文献[3]在iBM算法的基础上提出了一种改进型iBM算法,即RiBM(Reformulated inversionless BM)算法。表1给出了各译码算法关键路径时延和复杂度比较。

表1 关键路径时延和硬件复杂度比较

表1中“加法器、乘法器、锁存器、二选一器”的数量代表算法实现时的硬件开销大小,时钟周期决定译码过程所需的总时间,而关键路径时延决定译码器能够工作的最高时钟频率,三者综合在一起决定译码算法能够达到的最高译码速率。译码器实现时,乘法器使用的最多,可见RiBM算法的硬件开销大约是折叠Euclidean算法(Folded Euclidean)的3倍,但求解关键方程的时间是它的1/6,而且关键路径时延也较短,付出的代价也在可接受范围之内。RiBM算法在关键路径延时和资源使用等方面与传统的BM和Euclid算法及其改进算法相比,做到了更好的折中,因此本文采用RiBM算法进行关键方程求解。

2 译码器的FPGA设计

2.1 伴随式计算

其中n=204,i=1,2…2t,a为x8+x4+x3+x2+1=0所生成的GF(28)域中的本原元。其实现结构如图2所示。

2.2 求解关键方程

采用RiBM算法求解关键方程。算法的具体过程如下:

2.3 求解错误位置和错误值

在计算错误值过程中,求逆运算使用ROM查找表法。Chien搜索电路和Forney算法电路作为一个整体实现,电路结构如图4所示。

3 实现与验证

本文设计的RS(204,188)译码器选择ALTERA公司StratixII系列的EP2S15F484C3芯片作为目标器件,在QuartusII 9.1集成环境中,使用Verilog HDL语言编写。综合工具为Synplify Pro 9.6.1,综合结果在QuartusII中进行布局布线,使用Modelsim 6.5进行仿真。结果表明该译码器最高工作频率可达117.32 MHz,译码延迟仅为358个时钟周期。译码仿真结果如图5、图6所示。

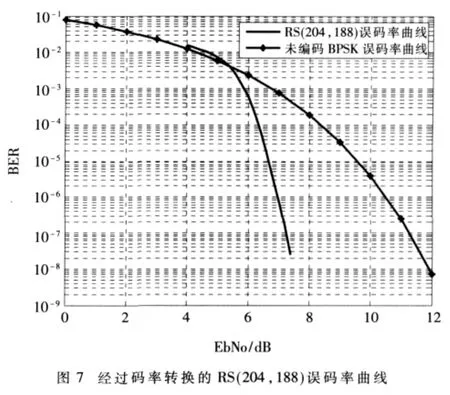

使用Matlab对译码器性能进行测试。首先在Matlab中实现RS(204,188)编码器,对伪随机码发生器产生的随机数据进行编码,仿真BPSK调制解调方式和高斯白噪声(AWGN)对编码数据进行加噪,加噪后的编码数据存储在文本文档中。然后编写testbench测试程序,读入加噪后的编码数据,经译码器处理后,将结果写入另一文本文档[4]。对比未加噪的原始数据和译码结果从而得到误码率曲线如图7所示。

本文介绍了用FPGA实现基于DVB-H标准的RS(204,188)码译码器的方法。译码过程采用了改进型无逆BM算法—RiBM。通过计算机仿真以及测试分析,证明该译码器可以稳定可靠地实现译码功能,在尽可能节约硬件资源的同时满足了高速处理的需要。

[1]王新梅,肖国镇.纠错码-原理与方法[M].西安:西安电子科技大学出版社,2001.

[2]DVB Documents A081.Transmission System for handheld Terminal(DVB-H),2004(6).

[3]Sarwate D V,Shanbhag N R.High-speed architectures for Reed-Solomon decoders.IEEE Transactions on Very Large Integration(VLSI)System.2001,9(5):641-655.

[4]夏宇闻.Verilog数字系统设计教程[M].北京:北京航空航天大学出版社,2002.