基于DSP和FPGA的实时图像压缩系统设计*

彭旭锋,刘文怡,李金力

(中北大学 电子测试技术国家重点实验室,仪器科学与动态测试教育部重点实验室,山西 太原030051)

目前使用的图像采集系统输入信号通常为PAL或者NTSL制式的CVBS复合信号,压缩速度25帧/s(PAL)或者30帧/s(NTSC)。但在工业控制、航天以及安防领域,有时需要监测快速移动的目标,或者瞬间发生的物理现象,事后还要对数据进行分析、处理。为了提高测量精度,通常需要采用高频帧图像采集系统。本文针对某Camera Link接口的图像传感器,设计了一个高频帧图像采集系统,该系统能够每秒采集100帧,并对其进行JPEG压缩,压缩完的数据通过RS422传输至远处的监测系统。

1 系统工作原理及硬件设计

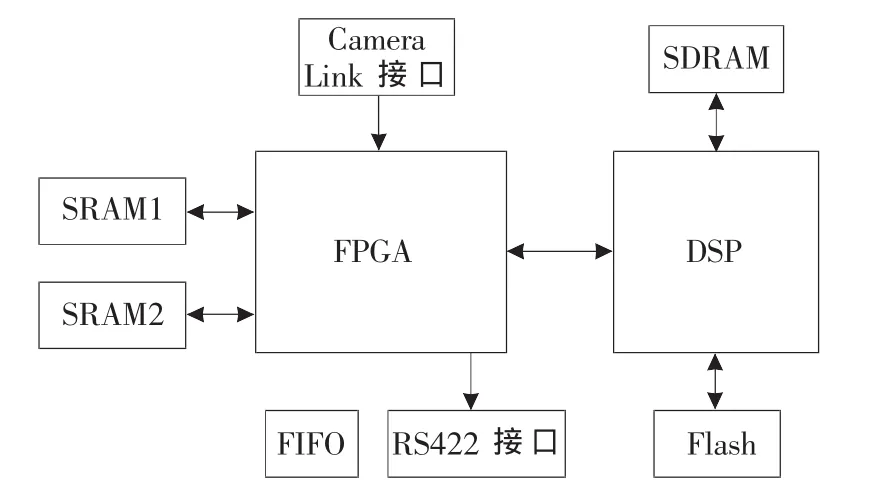

系统由Camera Link接口模块、以FPGA为核心的图像采集预处理与传输单元、以DSP为核心的图像压缩单元以及RS422远距离数据传输单元组成。由于采集、处理均需要访问存储器,为了降低成本,采用普通的异步SRAM,按功能区分可分为采集SRAM和压缩处理SRAM。读写逻辑由FPGA控制,采用乒乓机制进行切换。整个系统结构如图1所示。

系统工作过程:图像信号经由LVDS转换芯片后转换成LVTTL信号,直接传送至FPGA解码为8位数据,以字节方式一行一行写入SRAM静态存储器(存储器由两部分组成),用于乒乓缓存输入数据,每部分满1帧后由FPGA控制送出帧中断给DSP,DSP启动EDMA读入1帧数据,采用JPEG2000方式编码后连续写入到FIFO_OUT,FPGA负责从FIFO_OUT读出数据,非空即读,缓存积累不会超过1帧数据。读出的数据另行打包后以9 Mb/s的码率通过DS26LV31 422接口芯片从out1接口输出,或者分流后从out1和out2以各4.5 Mb/s的码率输出。

图1 系统结构图

2 FPGA功能模块设计

2.1 Camera Link接口模块

Camera Link接口模块负责对高频帧数字摄像头输出的LVDS信号转换为TTL标准信号。

关于Camera Link的采集数据的逻辑代码,关键之处在于产生存储器的地址信号、存储器写信号以及在对应的地址处将数据稳定地写进存储器。本系统用像素时钟产生列地址计数器、行同步信号产生行地址计数器,两者拼接产生存储器的地址信号。这样产生的有效地址虽然不连续,但意义明确,而且有利于显示部分的隔行隔列显示。对于8 bit的数据,可将2个有效数据拼接成16 bit后再存储,这样可以提高FPGA读写存储器的速度。

Camera Link接口时序如图2所示。

图2 Camera Link接口时序

图2中:VD为帧同步信号,电平模式,高电平有效;HD为行同步信号,脉冲模式,上升沿有效;PCLK为像素同步时钟,脉冲模式;DATA为10 bit图像数据,在PCLK的下降沿推出,接收端在PCLK上升沿采集,PCLK为常运行模式。每个VD有效期内有480个HD有效信号,在第0~478个HD有效时,每个HD有效期间有600个有效图像数据,第 479个HD(即每帧的最后 1行)有效时,前 600个DATA为有效图像数据,600个 DATA后预留6个字节输出图像相关信息,即第D600~D605为预留字节。

2.2 SRAM乒乓缓存

在图像采集处理系统中,DSP的压缩算法在实现时间上往往并不是固定不变的,然而前端的采集模块却使用均匀速度对图像进行采集,这样存在时间上的不同步,有可能会导致图像数据的丢失和影响帧数据的完整性[2]。为此,本系统在采集和压缩模块之间增加1个缓冲电路来解决这一问题。

常用的缓冲电路主要有3种[3]:双口RAM结构、FIFO结构和乒乓结构。由于乒乓结构可以使用相对比较便宜的高速大容量SRAM,而且可以实现数据的连续性,因此本系统采用了乒乓结构双SRAM作为视频数据的缓冲。在将1帧图像的数据全部存储完以后,DSP再利用很短的时间直接将1帧图像数据读入片内,这样既可以保证不丢失像素数据、DSP可以连续采集每1帧像素数据,又能为DSP留出更多空余时间,为后面进行图像处理提供可能。为了实现数据帧的完整性,必须保证读取数据帧的优先级要高于写数据帧的优先级,所以本系统的数据输入输出单元是根据数据处理流程来进行切换的。

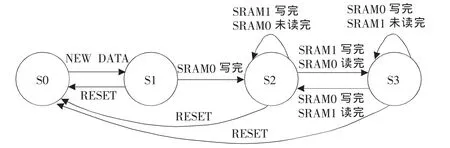

乒乓控制模块按照功能还分为:S0、S1、S2、S3 4个转换状态。其中,状态S0为初始化状态(所有信号都处于初始化状态),系统加电或者复位后进入此状态;在S1状态,主要负责对SRAM0的写入,不可以对SRAM1进行读操作;在S2状态,主要负责对SRAM1进行写操作,对SRAM0进行读操作,当SRAM1写完后,如果 SRAM0未读完,则继续处于状态 S2,如果 SRAM0读完,则进入状态S3;在S3状态,主要负责对SRAM0进行写操作,对SRAM1进行读操作,当SRAM0写完后,如果SRAM1未读完,则继续处于状态 S3,如果 SRAM1读完,则进入状态S2。乒乓控制模块状态转换图如图3所示。

图3 乒乓结构状态转换图

SRAM乒乓电路如图4所示。图中,wr_data为Camera Link接口接收到的只包含灰度信号的图像数据。为了方便图像数据的管理,每个像素、每行的像素都对应到了SRAM的固定地址,所以wr_addr为该像素在SRAM中的地址,同时也可以表示该像素在一幅图像中的位置。CHANNEL_SEL为读SRAM的标志位,0代表SRAM0,1代表 SRAM1。

2.3 FIFO缓存模块和RS422传输模块

由于DSP向RS422模块传输数据并不是匀速传输,而且传输速度比RS422的传输速度快很多倍,所以必须采用FIFO模块。

图4 SRAM乒乓原理图

3 DSP程序设计

TI公司的TMS320DM642芯片是一款高性能视频处理器,其主频可以高达600 MHz,数字处理能力可以达到4 800 MI/ps[3]。

DSP工作流程图如图5所示,DSP在相关外设与EDMA相关寄存器初始化完成后,才开始响应中断事件触发EDMA传输,在本系统中由EXITUINT4中断上升沿触发EDMA进行传输。在接收到FPGA发送的中断信号后,开始进行EDMA传输,整个EDMA传输的过程需要10 ms左右,传输完成后触发EDMA中断,在中断服务函数中触发1个软中断,在软中断服务函数中进行图像数据的压缩。

图5 DSP程序流程图

3.1 EDMA乒乓程序设计

在整个DSP的工作流程中,要实现图像数据采集、压缩、传输同时进行,则在DSP程序中需要1个双缓冲buffer,在向 buf1中采集图像信号的时候,DSP可以对buf2中的数据进行压缩,而在对buf2中进行采集的时候,DSP可以对buf1中的数据进行压缩。

实现这个功能的方法是采用EDMA ping_pong方式。在DSP中使用hEdmaPing和hEdmaPong双通道EDMA并建立PingBuffer和PongBuffer两个数据存储区。当写完1帧图像后,FPGA发送EXTINT4中断信号启动hEdmaPing将数据搬移到 PingBuffer,同时将通道链接至hEdmaPong。在下一个中断事件发生时将数据搬移到PongBuffer中,CPU在hEdmaPong通道完成中断服务程序中链接hEdmaPing通道。如此往复,使系统数据搬移和处理连续进行。

3.2 DSP/BIOS调度程序设计

仅仅采用EDMA乒乓方式进行EDMA数据传输还是不够的,不能实现数据的采集和压缩同时进行,还需要DSP/BIOS调度程序。在任务、硬件中断、软件中断中进行调度,在软中断服务函数中进行图像压缩任务。

DSP/BIOS是TI公司所设计开发的、尺寸可裁剪的实时多任务操作系统内核,通过使用DSP/BIOS提供的丰富的内核服务,开发者能快速地创建满足实时性能要求的精细复杂的多任务应用程序。

DSP/BIOS程序编写过程如下:

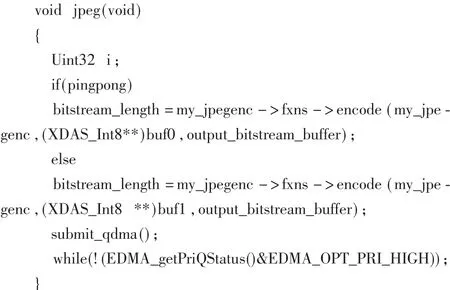

(1)在DSP/BIOS配置面板中添加1个软中断jpeg_swi,并将该软中断的服务函数设置为jpeg。

(2)添加软中断服务函数jpeg();代码如下:

(3)在EDMA中断服务函数中添加如下代码:

该函数的作用是触发jpeg_swi软中断。

4 系统关键技术

4.1 时钟

在使用内部生成的时钟过程中,可能引起设计上的功能和时限问题。组合逻辑产生的时钟会引入毛刺,造成功能问题,而引入的延迟则可能会导致时限问题。

本设计中用到很多全局时钟的整数倍分频,且由于分频的整数倍较大,如果利用FPGA中自带的DCM模块很难实现这样的功能。因此,采用同步计数器的分频方法,并且在各个时钟信号输出之前,再加一级寄存器输出,这样的操作就避免了组合逻辑生成的毛刺被阻挡在寄存器的数据输入端口上。

4.2 DSP与FPGA数据交换

由于压缩算法采用MECOSO公司的JPEG压缩算法,经过优化和处理后,压缩1幅图像仅需要4 ms。所以影响整个系统能否实现高频帧的关键技术是EDMA向SDRAM中搬移数据的速度,在本设计中设帧图像的大小为600×480=288 KB,传输1幅图像所需的时间需要10 ms。影响其速度主要有2个因素:EMIF所使用的ECLOCK和EMIF相关设置的寄存器。

在本系统中,ECLOCK采用了DSP的CPU4分频,使EMIF的CLOCK工作在150 MHz,大大提高了搬移速度。由于SRAM映射在DSP的CE2空间,考虑到读取数据需要建立(setup)、选通(Strobe)和保持(Hold)3个步骤,故将CE2相关寄存器的建立时间和选通时间选择为1个clk,经Hold时间设置为 0。这样设置后 EMIF总线的数据吞吐量为:

本文设计的图像压缩系统实现了分辨率为600×480、帧频率为100帧/s的视频信号输入的图像采集,并能够进行实时的JPEG压缩。系统采用DSP+FPGA的方案,虽然是一种较常用的组织方式,但在该系统中解决了一些关键的问题,大大提高了图像压缩速度及系统的灵活性。本系统已经应用于航天领域某监测系统,效果良好,运行稳定。

[1]李武森,迟泽英,陈文建.高速 DSP图像处理系统中的乒乓缓存结构研究[J].光电子技术与信息,2005(3):76-79.

[2]周如辉.实时视频处理系统中乒乓缓存控制器的设计[J].电子元器件应用,2006,33(4):66-68.

[3]江思敏,刘畅.TMS320C6000 DSP应用开发教程[M].北京:机械工业出版社,2005.